Setting up a SystemVerilog project in Sigasi Studio is easy. First you add all your source files. Next you configure the include paths, and you’re ready to go.

Sigasi Studio follows the Eclipse approach in setting up projects. This means that there is a lot of flexibility, but in most cases it is a matter of pointing Sigasi Studio to the correct source folder. If you want to exclude some SystemVerilog source files from your project, right click on the source files and select Exclude from build (This also works for folders).

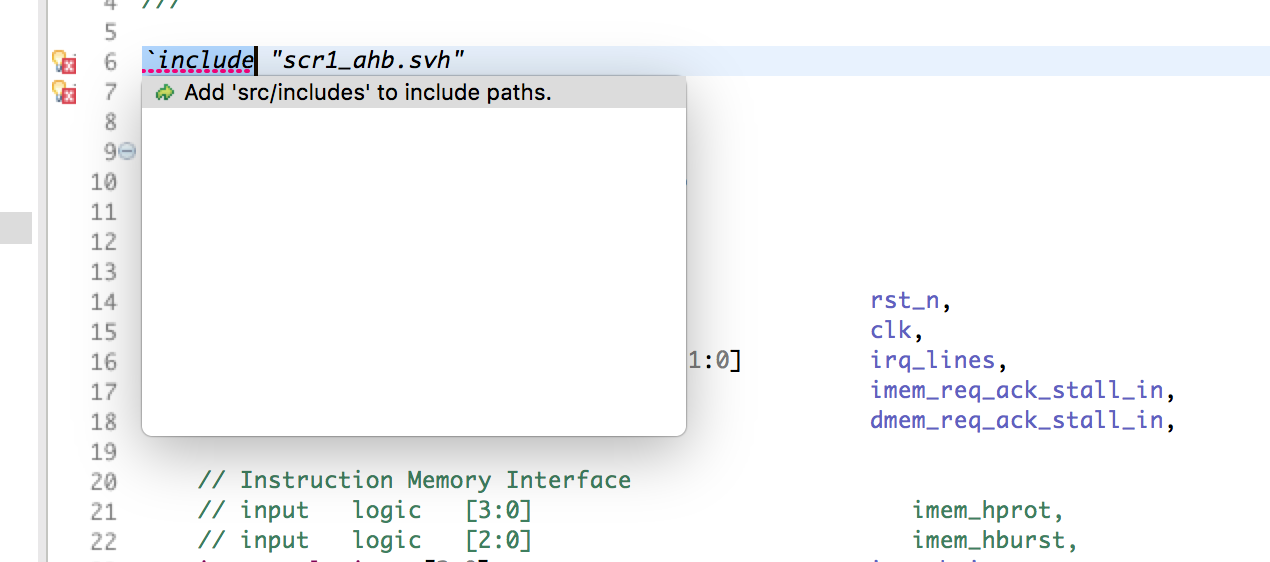

If you are using Verilog Preprocessor includes, and the include files are not next to your source files, you also have to set include paths. The most convenient way to configure this, is with a Quick Fix: Open the source file with the `include directive, click on the error marker, and select the suggested fix.

Example: Opening the SCR1, open-source RISC-V project from GitHub

To demonstrate how easy this is, I will guide you through opening the SCR1 project in Sigasi Studio. SCR1 is an open-source RISC-V compatible MCU core, designed by Syntacore.

Importing a checked-out version of the project

If you already have cloned the project on your computer, follow these steps:

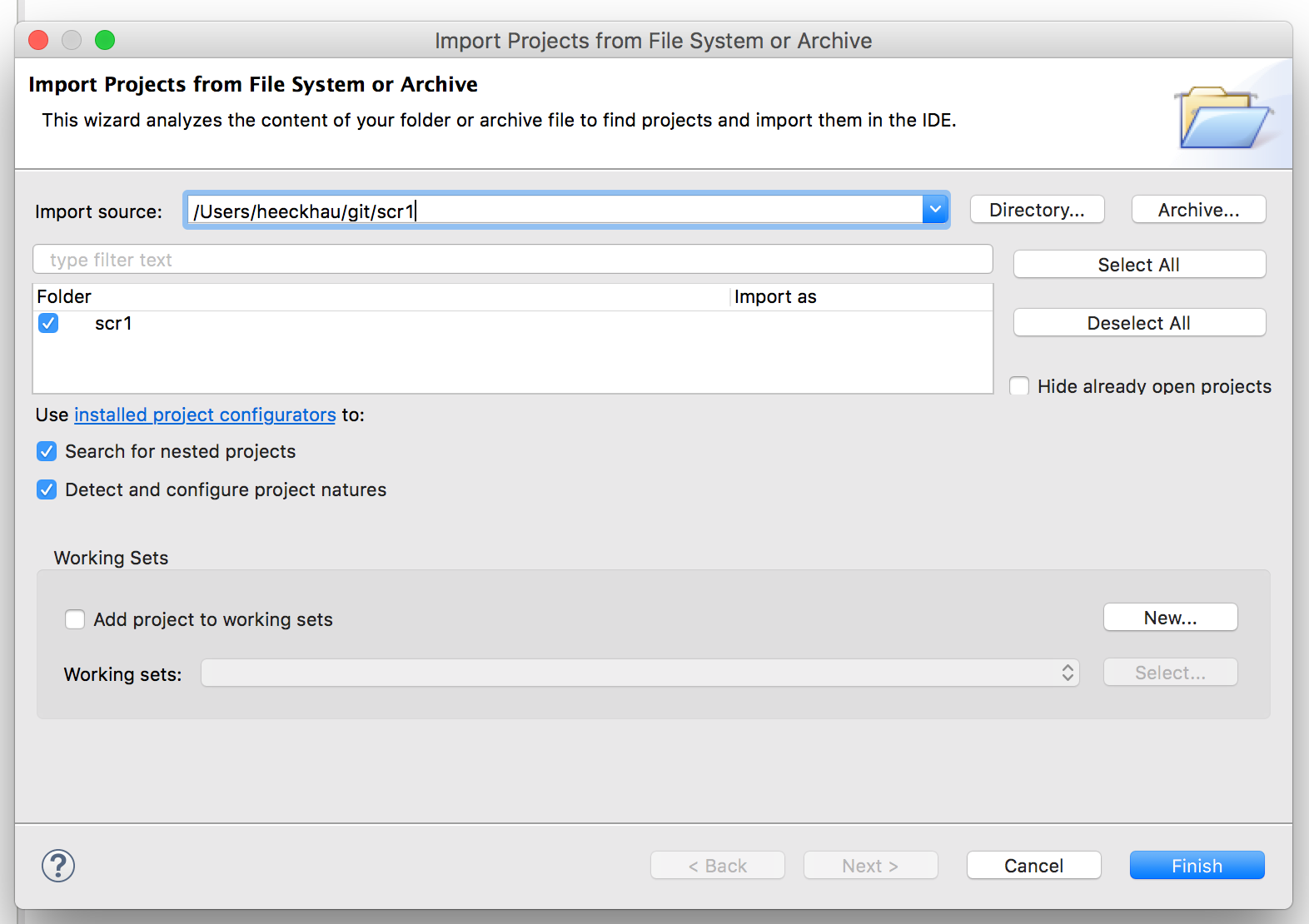

- Select File > Open Project from File System…, click Directory… and browse to the location of the source files (in my case this is

/Users/heeckhau/git/scr1).

- Click Finish

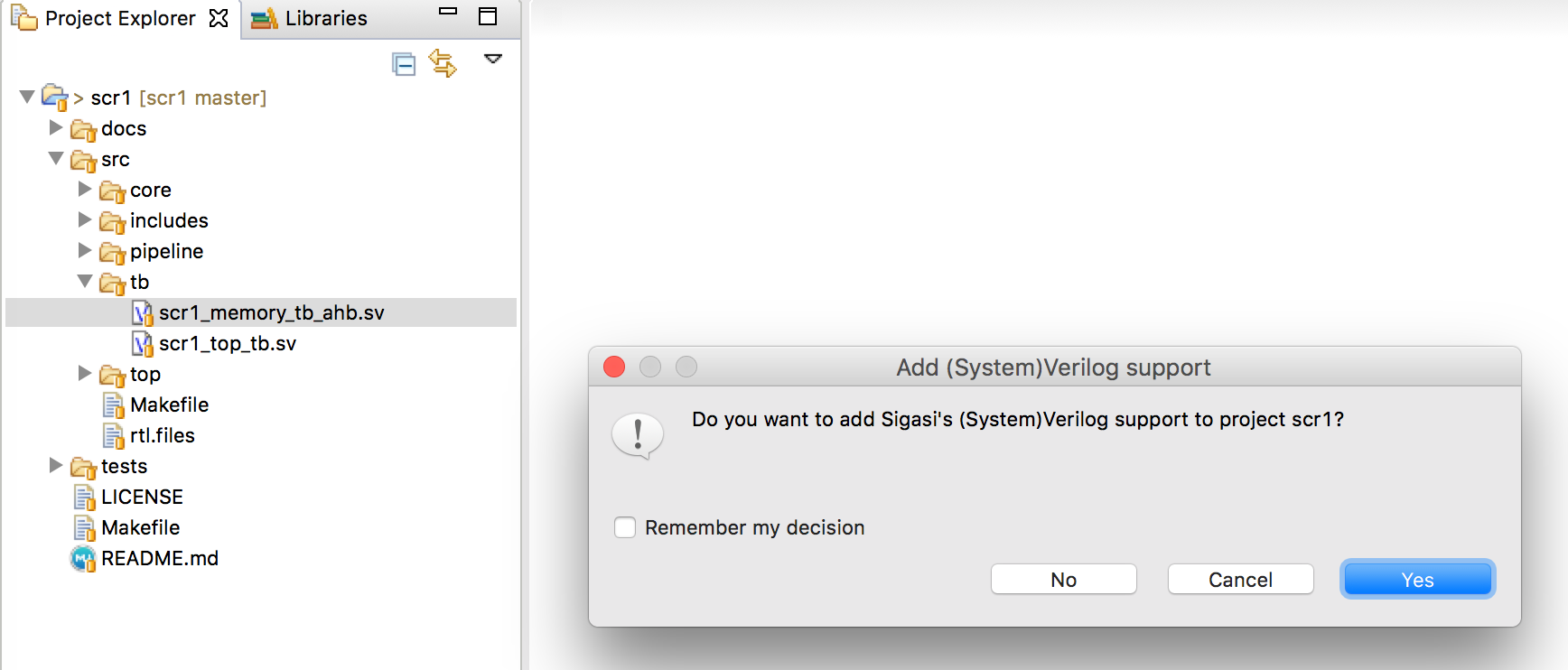

- Open any SystemVerilog source file (e.g.

src/scr1_memory_tb_ahb.sv) and confirm that you want to add Sigasi’s (System)Verilog support to the project.

- Click on the error marker (with the light bulb decorator) next to the `include directive and select Add ‘src/includes’ to include paths..

Clone the project using the Git plugin

Sigasi Studio offers Git support via the EGit plugin . This way you can also clone the sources inside the tool itself:

- Click File > Import…

- Next inside the Git category select Projects from Git and click Next

- Select Clone URI and click Next

- Paste the git repo location

https://github.com/syntacore/scr1.gitin the URI: field and click Next - Select the master branch and click Next

- Select the local destination for the cloned source

- Select Import as generic project

- Confirm the project name

- Click Finish

- Follow steps 3-5 from the list above

Remarks

- Sigasi Studio treats SystemVerilog include files as regular SystemVerilog code by taking the ‘including’ context into account. This requires no extra setup or configuration from your part.

- The project information is stored in:

- The

.projectfile, it describes which files belong to the project - The

.library_mapping.xmlfile, it describes the project’s library information (and excluded files) - All other project settings are stored in the

.settingsfolder

- The

See also

- How to set up the UVVM Library in Sigasi Studio (legacy)

- Making sense of HDL Verification Methodologies (opinion)

- ANSI and Non-ANSI Port Declarations in Verilog (blog post)

- Sigasi's Software Development Kit Part 2 (legacy)

- Sigasi's Software Development Kit Part 1 (legacy)