Extension Setup

This page explains how to install and configure Sigasi Visual HDL (SVH).

Requirements

VS Code Version

The extension requires VS Code or VS Codium version 1.77.0 or higher.

Java Runtime (Optional)

The path to use the Java Runtime (JRE) can optionally be configured in the settings. If empty, the extension will extract the included JRE in the user’s home folder.

- Linux:

~/.config/Code/User/globalStorage/sigasi.sigasi-vscode - Windows:

%AppData%\Code\User\globalStorage\sigasi.sigasi-vscode

If you wish to provide the JRE:

- The extension requires a Java Runtime

- The Java runtime must be 64-bit. Make sure to use JRE 11 or JRE 17

- You can check your Java version with

java -version - Java can be downloaded from several sources, a.o. Adoptium

- Make sure the

javaexecutable is available in thePATHenvironment variable

Installation

You can install the extension from the VS Code marketplace .

To install the extension from VS Code, open the Extensions pane using Ctrl+Shift+X. In the Search field on top, type Sigasi. Click the Sigasi extension and click Install.

You can also download the self-contained VSIX file directly. Go to the SVH extension marketplace webpage , and on the right panel under Resources, click on Download Extension. This will give you the option to download the Windows x64 or the Linux x64 VSIX.

If you’re working on a remote host for your HDL development, the extension only needs to be installed on the remote.

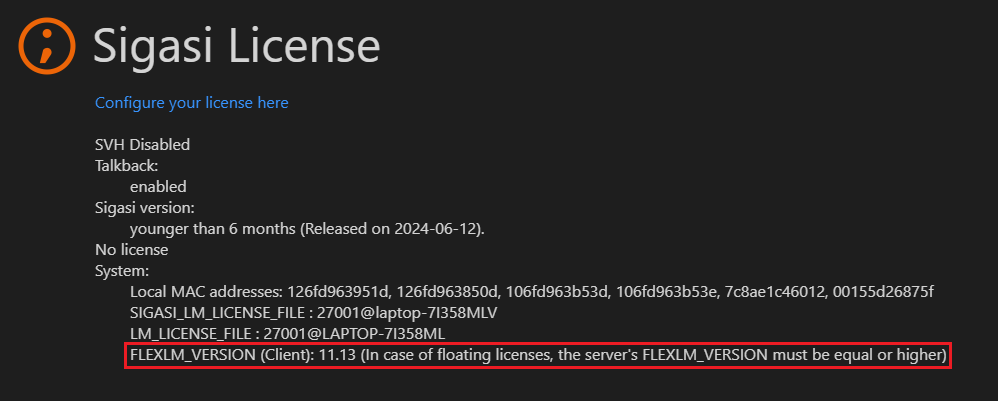

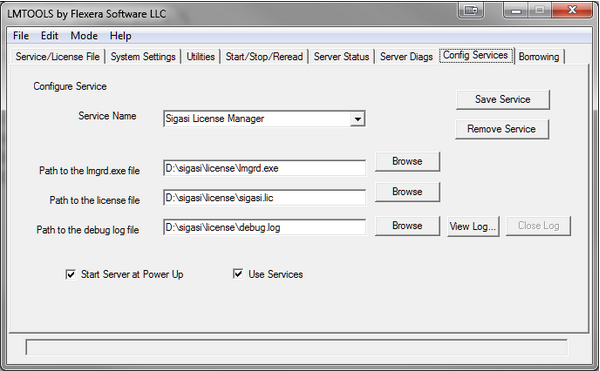

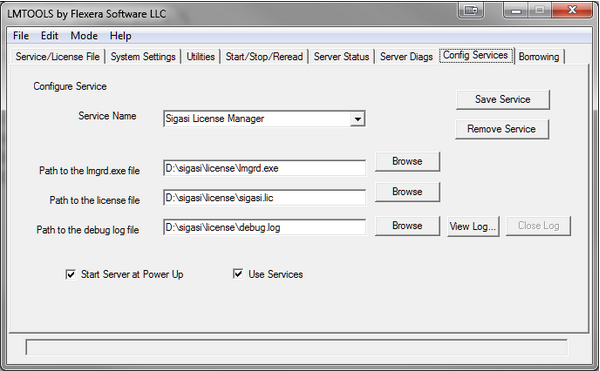

Licensing

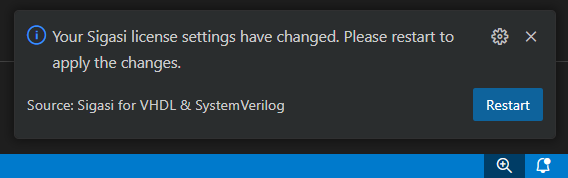

More details can be found here. Your license unlocks the features for your edition.

Updating

VS Code supports automatic extension updates.

Since VS Code version 1.85, fine-grained control about which extensions to auto-update is available.

If your Extensions: Auto Update setting is set to _Selected Extensions, you can right-click the Sigasi extension in the Extensions pane and select the Auto Update option. Doing so ensures that your Sigasi extension will be updated even when other extensions are not auto-updating.

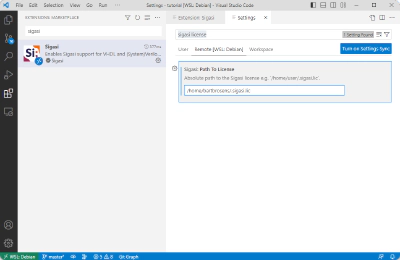

Settings

You can reach the settings for the Sigasi extension as follows.

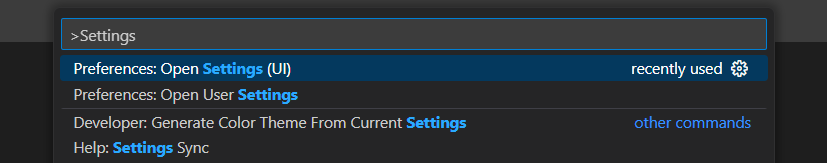

- Open the Command Palette using Ctrl+Shift+P

- Start typing and select Preferences: Open Settings (UI)

- In the Search field on top, type Sigasi.

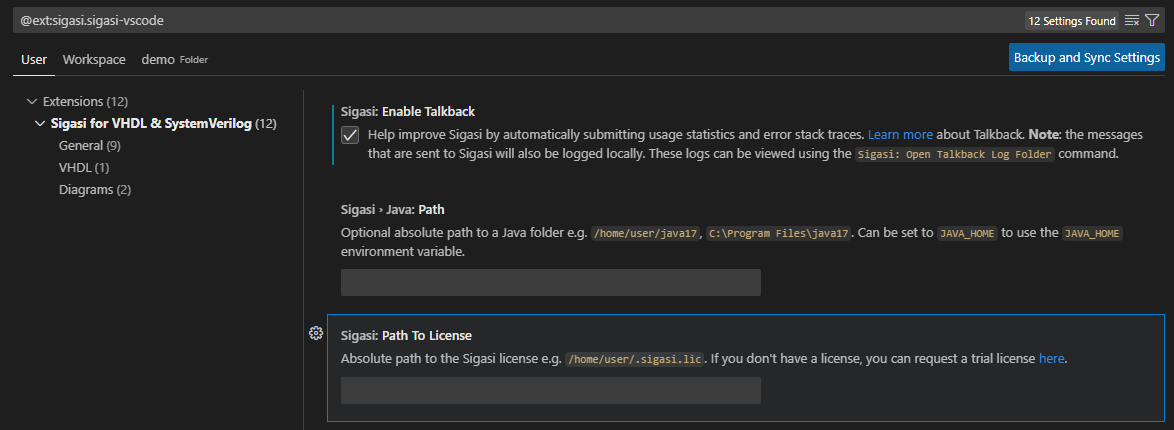

- First, configure the Path To License. It can be a local node-locked license file or a floating license server, e.g.,

27000@myserver.example.com. - Optionally, configure the JRE location in Sigasi > Java: Path. Make sure to add the

javaexecutable name to the configured value.

Alternatively, you can access the Sigasi extension settings through the Manage icon () in the extensions overview.

Talkback and Telemetry

You can help improve the Sigasi extension for VS Code by enabling automatic submission of usage statistics and error stack traces through Talkback and telemetry. More information about these features is available on the Talkback manual page.

Talkback is disabled by default.

To enable Talkback in the VS Code extension, open the settings and enable the Sigasi: Enable Talkback option.

The messages sent to Sigasi are logged locally. You can view these messages using the Sigasi: Open Talkback Log Folder command.

On Disk Caching

Disk caching is enabled by default in the Sigasi extension for VS Code. We recommend leaving it enabled as the cache will significantly speed up the extension by preserving the state from an earlier moment.

However, if you’d like to disable it, you can turn off the setting Sigasi > Server > Caching: Enable On-Disk Caching.

[Back to top]

Setting up a Project

The Sigasi Visual HDL (SVH) extension will start once a .project file is detected in the root of the open folder. Make sure that you configure your license before trying to work on a project.

For project configuration, open the Sigasi Projects View.

Creating and Importing Projects

Importing a Project from the File System

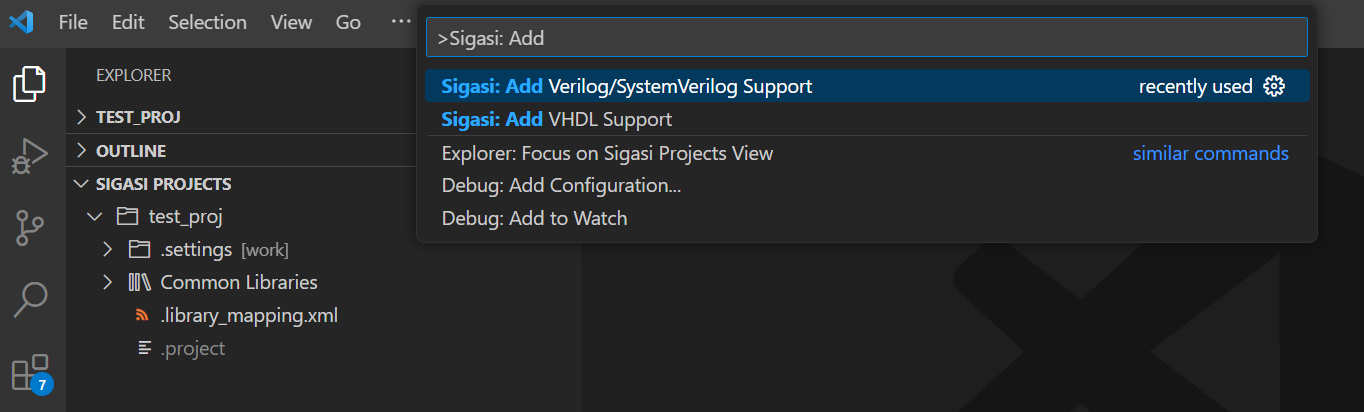

First, open the folder you want to import through (File > Open Folder…). Then, open the Command Palette (Ctrl+Shift+P) and run the command Sigasi: Add Sigasi Support.

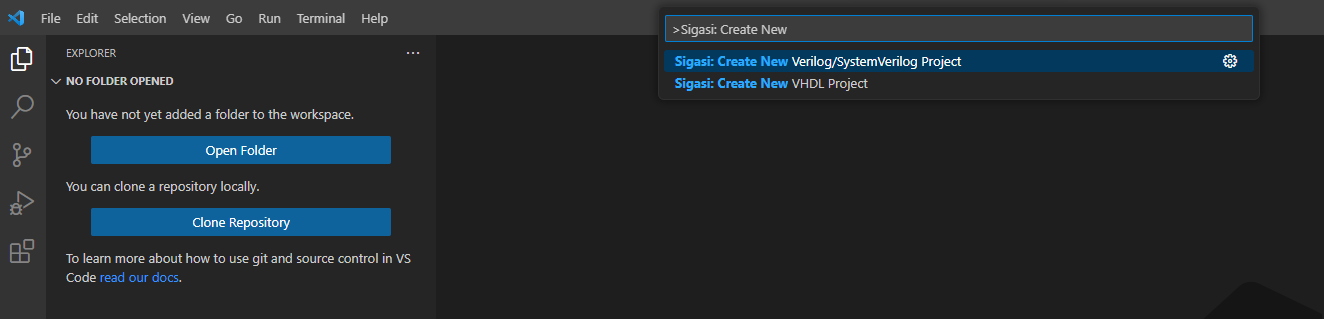

Creating a New Project From Scratch

To create a new project, open the Command Pallet (View > Command Pallete…), execute the command Sigasi: Create New Sigasi Project, choose the project location, then give your project a name.

Next, you need to have the project’s root folder to create a .project file in your folder containing the project configurations.

Once the .project file is detected, SVH will fully start, indicated by a Projects View below the default VSC file explorer.

From then on, you should use the Projects View instead of the VSC file explorer.

Every Sigasi project has mixed-language support.

Importing Another Tool’s Project

You can import a project from another tool (e.g., a Quartus project) by first it converting into an SVH project using scripts. Find the scripts and documentation at https://github.com/sigasi/SigasiProjectCreator .

Tutorial and Demo Projects

The extension contains both a tutorial project and demo project.

Tutorial

The tutorial project covers most of Sigasi’s features. Press Ctrl+Shift+P and start typing Sigasi: Create Tutorial Project to open the tutorial.

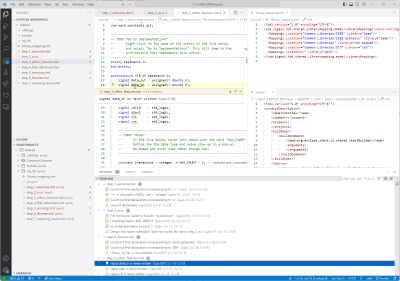

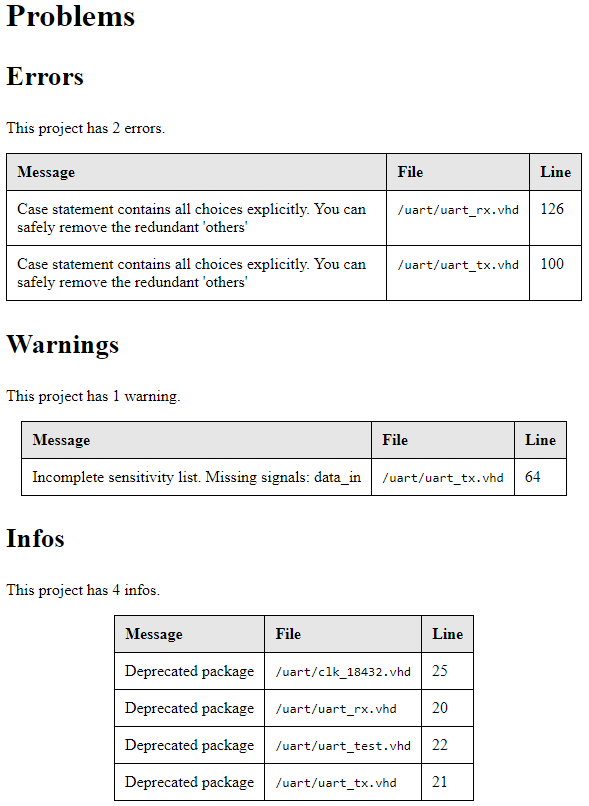

When the extension has finished building the project, you will see a number of issues for some files pop-up in the Projects View.

There will also be several errors and warnings in the status bar, which you can click to open the Problems View. Within that view, you can navigate through the error and warning markers for the project.

See also: Tutorial Project in Sigasi Visual HDL

Demo

You can also open a larger demo project using the command Sigasi: Create Demo Project.

Project Configuration

Library Configuration

VHDL libraries are fully supported. For Verilog/SystemVerilog, Sigasi reuses the VHDL library concept (just work in practice) to distinguish between design files that should and shouldn’t be analyzed.

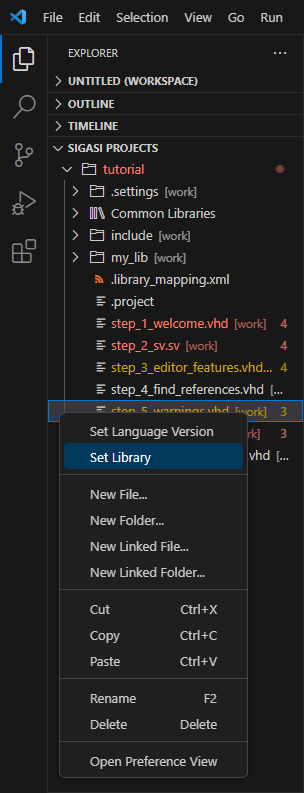

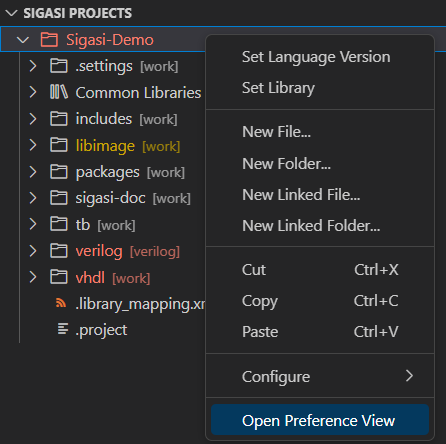

To change library mappings, you can use the right-click menu in the Sigasi Projects View and select Set Library as shown in the image below.

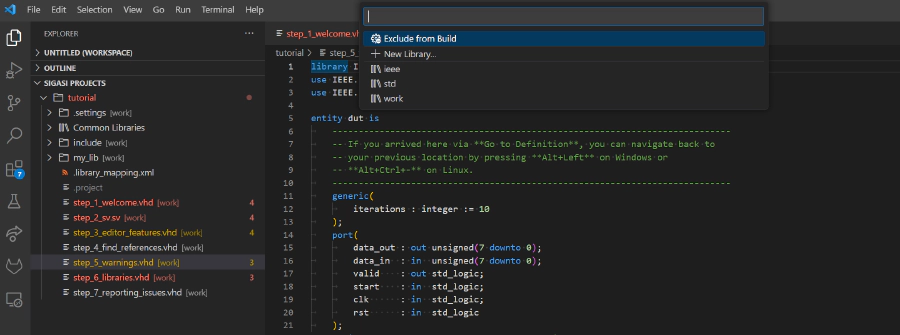

Then, you can select an existing library or choose New Library… to type a new library name.

Once you type a new library name, the file/folder you selected will be added to the library you created.

If you want to add a file/folder to an existing library, you can choose one of the existing ones from the list (such as work).

If you want to exclude files/folders from a Sigasi project, select Exclude from Build. Note that the excluded resource(s) will still be visible in the Sigasi Projects View, and you can still add them (Set Library) to the project.

Creating new libraries, adding a file/folder to an existing library, or excluding files/folders from the build will modify your project’s .library_mapping.xml file.

VHDL and Verilog Version

To change the VHDL or Verilog version, right-click on a project, folder, or file in the Sigasi Projects View and click Set Language Version. Then, select whether you want to set the VHDL or Verilog version. If you only see one of the two, you might need to add language support. Bes sure to select the version you want.

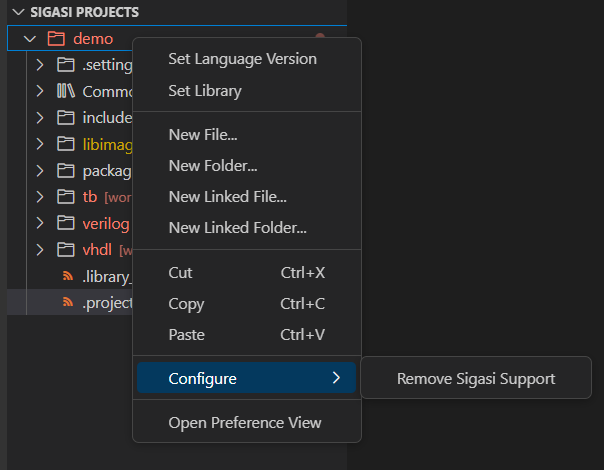

Sigasi Support

To add or remove Sigasi support, you can right-click on a project from the Sigasi Projects View, click Configure, and Add/Remove Sigasi Support. This will enable or disable Sigasi support.

Workspace

To add a new project to your workspace, press File > Add Folder To Workspace.

Make sure the project you’re adding has a valid .project file.

Linked Resources

Linked resources are a convenient way to link to a file/folder in the Sigasi ecosystem. They work without having to create symlinks or copy content.

To add a linked resource, you can right-click on the node where you want to add it, then click Add Linked File/Add Linked Folder. A file open dialog will pop-up and you can select the file(s)/folder(s) you want to link.

Environment Variables

SVH supports environment variables in its project configuration.

This helps to avoid absolute paths in the .project file.

To use environment variables, you have to prefix the environment variable with ENV-.

For example, to refer to the home directory, you can use ENV-HOME.

Custom Project Variables

Some variables are automatically defined.

PROJECT_LOCwith the PATH of your projectPARENT-<COUNT>-<VARIABLE>which points toCOUNTlevels above the PATH of theVARIABLE

For example, if your project lives in /design/projects/project1, then PARENT-2-PROJECT_LOC/companylibrary points to /design/companylibrary.

You can also use custom project variables, e.g., VUNIT, to point to your VUnit installation.

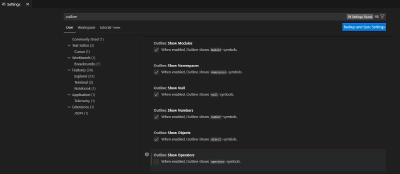

You can configure these variables as follows:

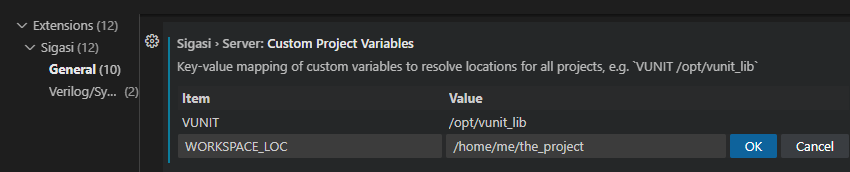

- Press Ctrl+Shift+P to open the Command Palette

- Select Preferences: Open Settings (UI)

- In the Setting tab, navigate to Extensions > Sigasi for VHDL & SystemVerilog > General > Custom Project Variables

- Add variables and their values as required

Note that custom project variables can be set on the User level and also per Remote or for a specific Workspace.

[Back to top]

Libraries

Introduction

HDL libraries are a very powerful feature of the HDL languages. Sigasi Visual HDL (SVH) makes it easy to configure and use them. We’re assuming that you understand the basic concepts of HDL libraries, and so this section focuses on how they are implemented in SVH.

As with any HDL tool, SVH needs to know where the libraries are located on your file system. Below, we describe how the library configuration can be examined and modified using the GUI.

We’ve also presented a use case about how to set up libraries with SVH to organize your projects.

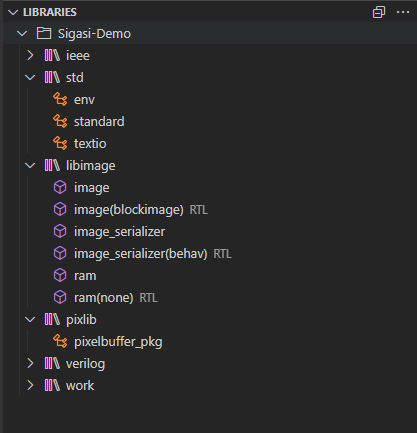

Examining the Library Configuration

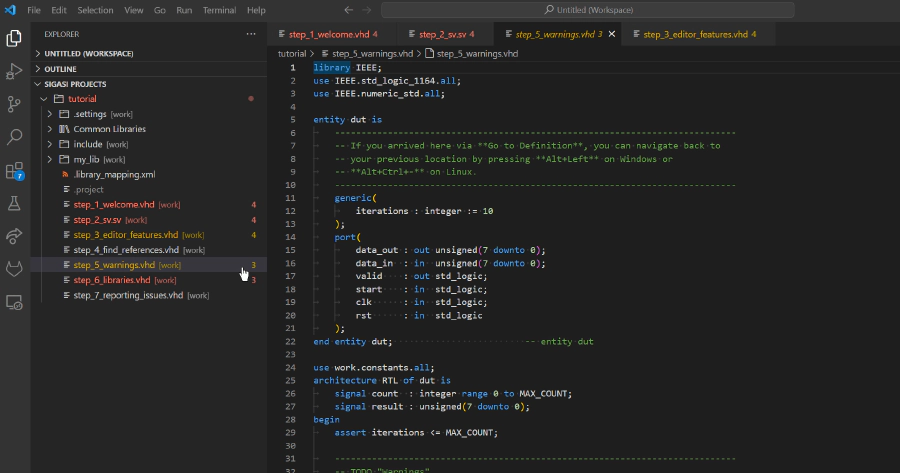

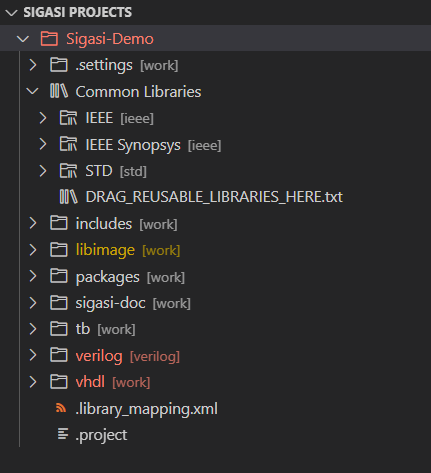

You can examine the library configuration in the Sigasi Projects view, which shows how VHDL or SystemVerilog files are mapped.

Each physical file or folder is annotated with the library it belongs to between square brackets.

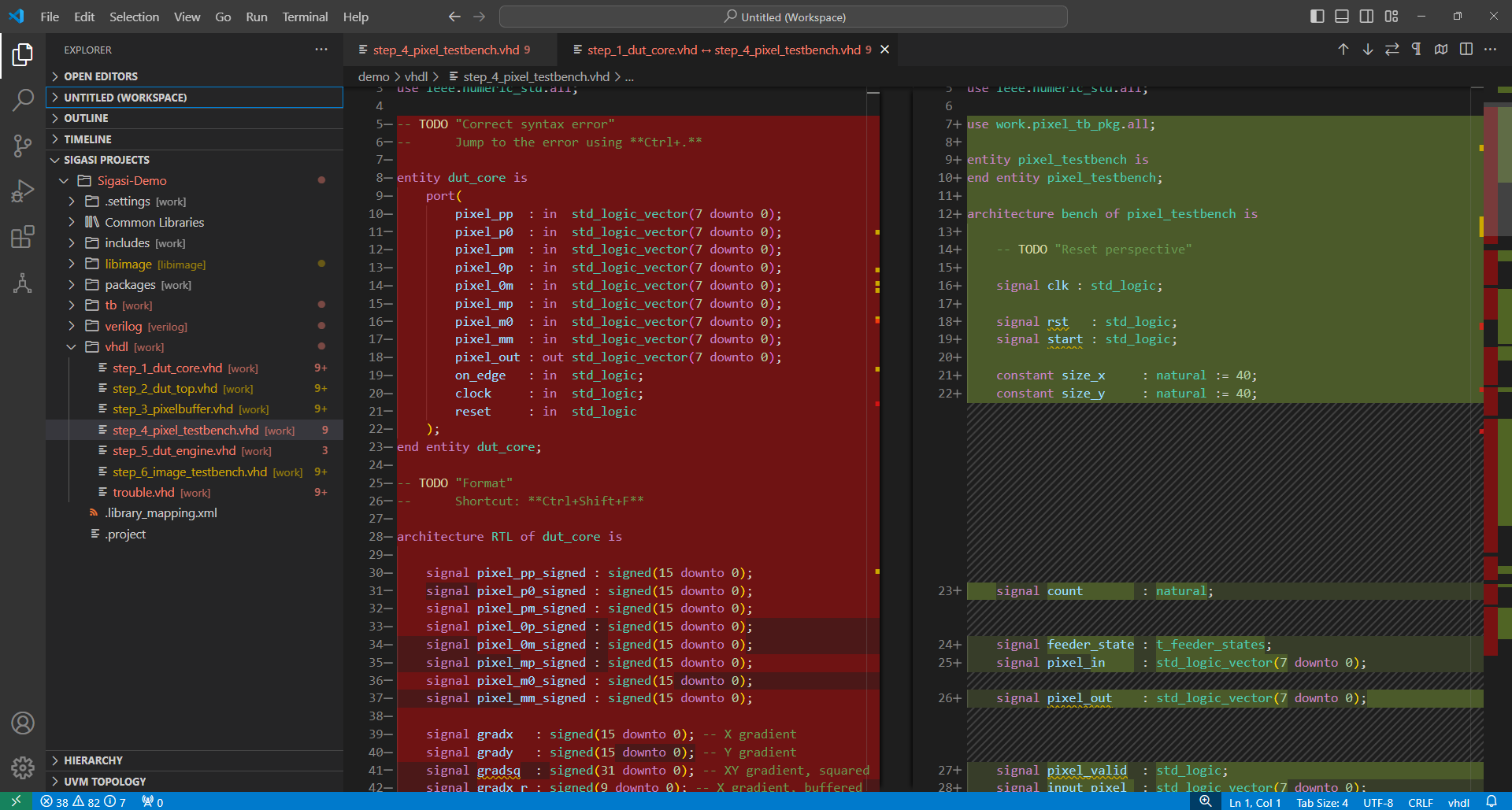

In the image above, you can see a mixed-language project called Sigasi-Demo, with a folder named

Common Libraries. In that folder, you see the typical standard

libraries (std and ieee) upon which all VHDL projects depend.

Lower down, you can see other folders, most of which are mapped to the library work.

One of the folders (verilog) is mapped to the library verilog.

Modifying the Library Configuration

You can modify library mapping for project files right in the Sigasi Projects view.

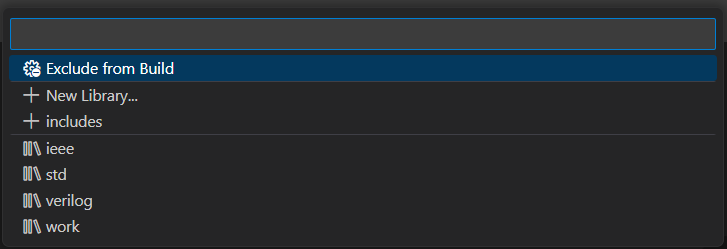

Select a file or a folder in the view and right-click.

Once you select Set Library in the menu, you will get the library configuration options, as you can see in the image below.

- Select Exclude from Build to exclude a file or folder from any library

- Select New Library… to define a new library and map a file or folder to it

- If you select one or more folders, SVH automatically suggests the folder name as a library - in this case, the

includesfolder - Select the name of an existing library to map a file or folder to that library

When you map a file into a library, only that file is affected. However, if you map a folder into a library, then everything in that folder will be mapped into that library. Any previous library mapping configurations applied to files or folders in the given folder will be overridden. When you are defining the library mapping for a new project, you should map from top to bottom.

So, in the case of our Sigasi-Demo project, if work is not

a good default, you would change the top folder’s mapping first and then override the

mapping in the sub-folders.

To exclude any file from all libraries, you can select the Exclude from build option.

SVH will then assume that the corresponding resource is

not part of the project and will not include that resource in a

project build. This is typically useful when you have stale copies of

HDL files or folders lying around that you simply want to ignore.

SystemVerilog Include Files

SystemVerilog include files are always excluded from the build. Any

file that is included in another design file gets excluded from the

build, even if it has an extension that would normally identify it as

a design file, e.g. .v or .sv. It often doesn’t make sense to

compile include files by themselves. Instead, include files are

compiled in the context of the file in which they are included.

Configuration File

All library configuration information is stored in the .library_mapping.xml

file in the root of your project.

If you edit this file, the affected HDL files in your project will be rebuilt automatically.

Note that .library_mapping.xml should be checked into your version control system.

SVH only writes changes to this configuration file when you make changes to the library configuration. When you do make changes, SVH first checks that all paths in the library configuration still exist. If a path no longer exists, it will be removed from the configuration file. Note that the library configuration file is case-sensitive, even on Windows.

Common Libraries

Each project has a folder called Common Libraries.

This is where reusable libraries go: whether vendor libraries, third-party IP

libraries, or your own reusable libraries. By default, the VHDL STD and IEEE

libraries are added to this folder.

The Common Libraries folder behaves like any other folder.

You can delete it, rename it, or apply a different library mapping.

In most cases, however, the default configuration is just what you need.

How To Add Files To Common Libraries

In any newly created Sigasi project, the Common Libraries folder

contains the VHDL files of the IEEE and STD libraries.

To add files, right-click the Common Libraries folder and select the

New Linked Folder to create a Linked Folder pointing to the actual folder location that contains the

files you wish to add to the Common Libraries.

How Is “Common Libraries” Different From Other Folders?

Common Librariesby default is a virtual folder. This means that it is not a real folder in the project directory and it can only contain references to folders on your file system.- Files in

Common Librariesare supposed to be error free. SVH will not mark errors or warnings in these files. - Aside from these, a few other libraries’ errors and warnings are never marked, regardless of their location.

These libraries are:

std,ieee,altera_mf,altera,XilinxCoreLib,unisim,mentor,lpm,simprim,std_developerskit,unimacro, andmodelsim_lib. - While you work on your project, you don’t want to edit the files in the

Common Libraries, but you do need them to compile your project.

Using Common Libraries is recommended for files that are supposed to be error free.

This increases SVH’s performance by preventing it from analyzing files that don’t need to be analyzed.

Adding Third-Party Libraries to a Project

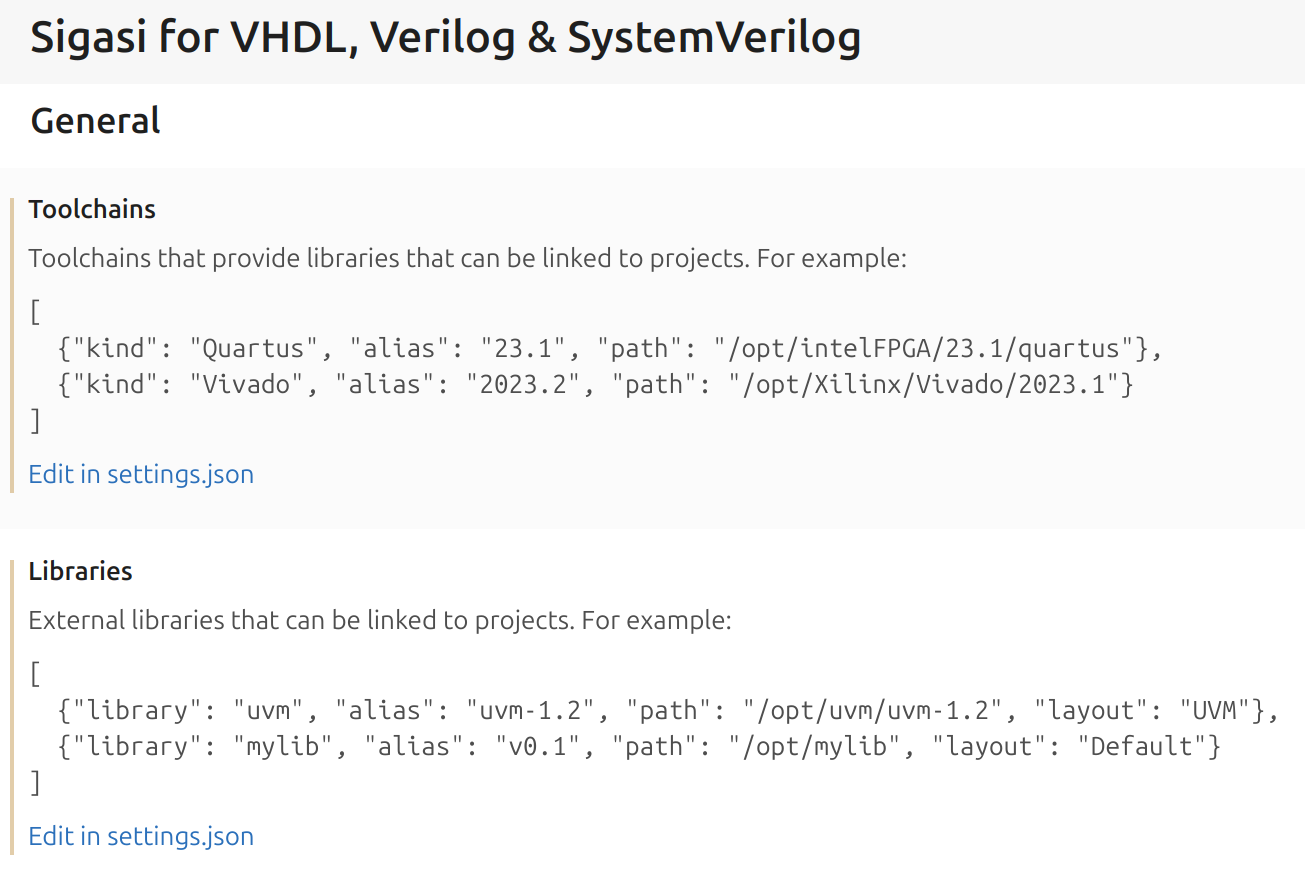

If your project uses libraries from Quartus or Vivado or standalone libraries (e.g. UVM), SVH provides a mechanism that makes it easier to add such libraries to a project and to switch between versions of libraries and toolchains.

First, SVH needs to know the location of the toolchains and standalone libraries on your system. SVH can automatically detect Quartus and Vivado installations:

- in default installation locations:

/opt,/tools,C:\,<home>, and<home>/Documents. - via environment variables that point to installation or

bindirectories of these tools (e.g.QUARTUS_ROOTDIR,XILINX_VIVADO,PATH, etc.).

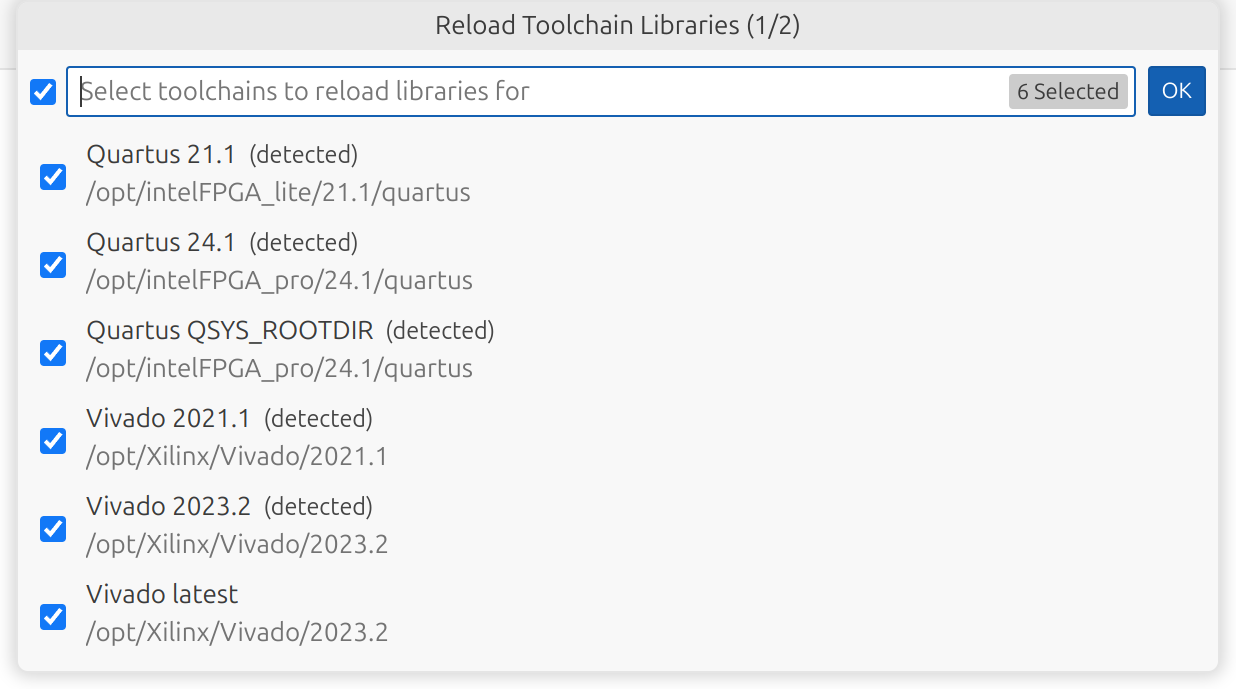

Note: You can run the Reload Toolchain Libraries command to see what toolchains were detected (they would have a (detected) mark).

You can override detected toolchains or add additional toolchain installations and external libraries in the extension settings:

- When adding a toolchain, you’ll have to specify:

- the installation path,

- the Kind (

QuartusorVivado), and - an alias that would be used in a project to reference this installation.

- When adding a library, you’ll have to specify:

- the library path,

- the library name, that would be used to map HDL files,

- the layout, which would configure how to link this library (at the moment, only two layouts are supported: a

UVMlibrary layout or aDefaultone that would simply link, map, and add a specified directory to include paths), and - an alias that would be used in a project to reference this library path

Once you’ve added all required toolchains (or are happy with detected toolchains) you have to extract their libraries with the Reload Toolchain Libraries command.

This would allow using these libraries in your project.

You can choose whether to extract only family-independent libraries or all libraries.

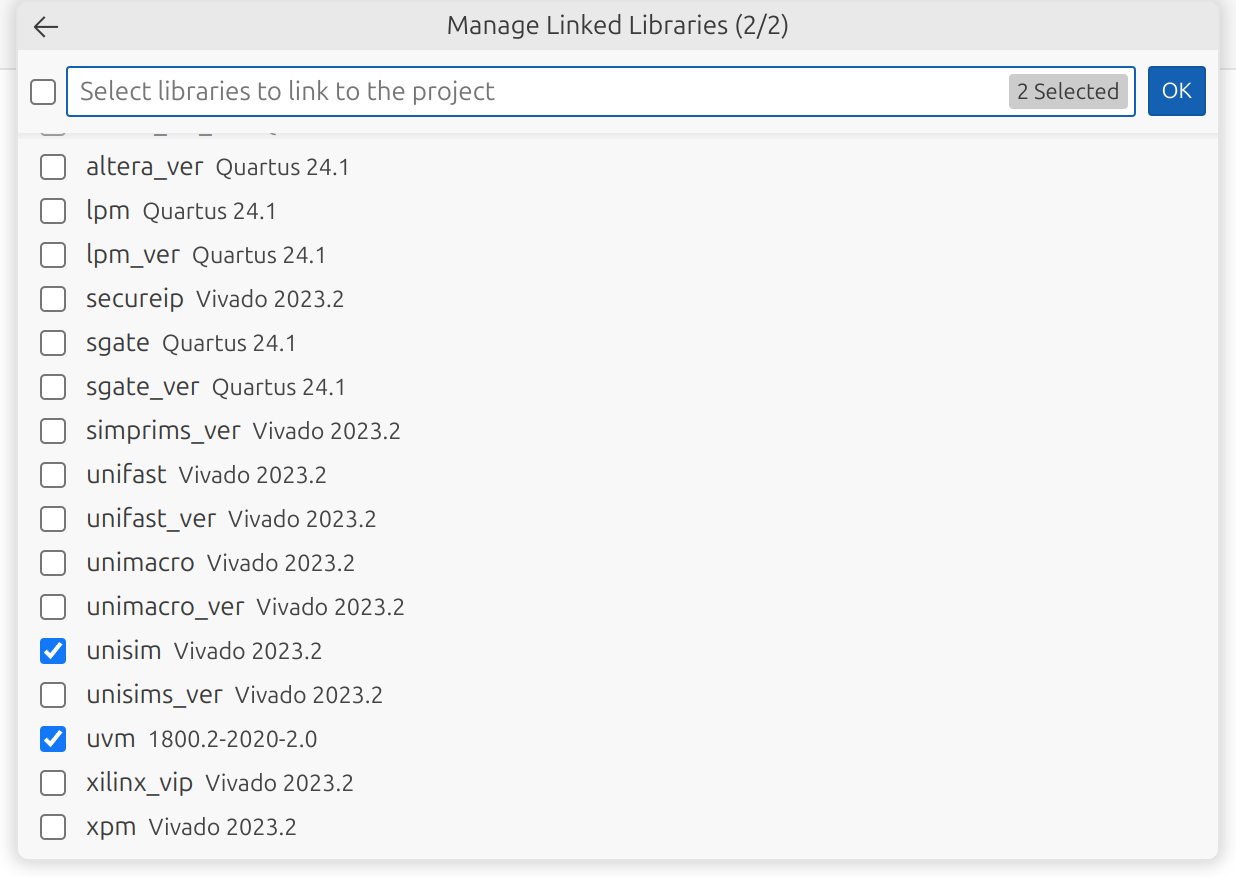

Now you can run the Manage Linked Libraries command and select what libraries you want to use in your project

(if you don’t need them later on, you can unselect them here as well).

After pressing the OK button (or Enter), the selected libraries will be linked to your project in the Common Libraries folder

(while unselected libraries will be removed). To the right of the library name in a wizard you can see what library or toolchain version is used.

Note: If the project configuration for a linked library is out-of-sync with an intended library layout (e.g. library files mapping was manually changed), this library will be marked as (out-of-sync) on this wizard page. Pressing the OK button (or Enter) will fix the configuration of all linked libraries that are out-of-sync.

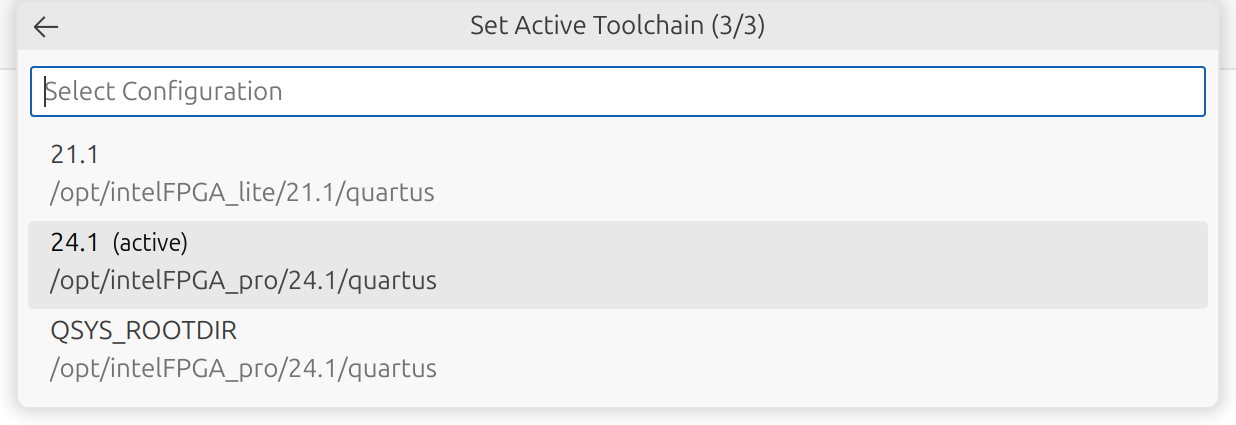

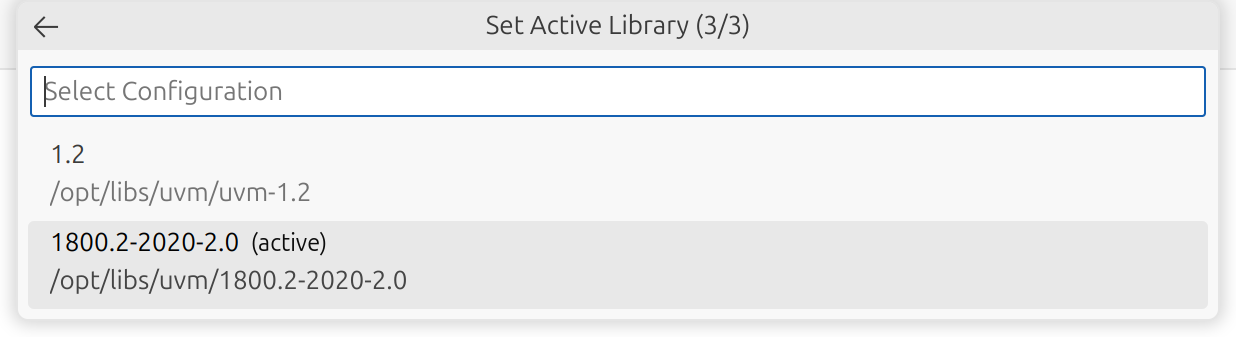

If you have multiple toolchain installations or library versions and would like to use a different one,

you can run the Set Active Toolchain or Set Active Library command and set a desired version as active.

A Reset Active Toolchains and Libraries command removes active toolchain and library aliases from project configuration files if those are not used by currently linked libraries. It can make configuration cleaner without affecting libraries linked to a project.

Note: When you link libraries this way, your project file and project settings will contain only aliases of toolchains and libraries, not their absolute paths on your system. This way, when multiple people work on a project, it’s sufficient to add a toolchain or library with the same alias in workspace settings (or use the same environment variable to point to the library or toolchain installation path).

[Back to top]

Views

This page documents the views the SVH extension adds to VS Code.

Sigasi Projects View

The Sigasi Projects View offers a file browser for your projects, including external folders that are not physically part of your project. This can be useful for including external IP in your projects.

The Projects View also offers a lot of custom Sigasi functionality, such as library mapping, version setting, and displaying the Preference View.

Linked Libraries

You can add any (external) libraries and files not within an open project’s folder using the Sigasi Projects View.

In the Sigasi Projects View, right-click any file or folder and select the New Linked File… or New Linked Folder… option to add files and folders from outside the project location.

The configuration of these external files and folders will be kept in the .project file in the project root.

You can add external files and folders anywhere in a project.

If you add a large folder, for example, the unisim primitives, make sure to exclude the folder (Right-click > Set Library > Exclude from Build) from being built and only include the required files.

Alternatively, you can put the library files in a folder called Common Libraries.

Then they will only be indexed and not analyzed for errors.

Buttons in the Sigasi Projects View

These buttons are available in the Sigasi Projects View:

Create a new file

Create a new folder

Refresh

Collapse all folders in the Sigasi Projects View

More Actions

- Toggle Follow Cursor (links the Sigasi Projects View with the editor)

Hierarchy View

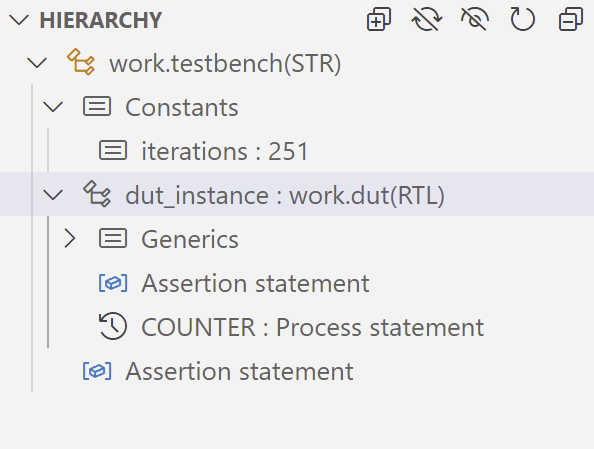

Initially, the Hierarchy View will be empty. To use the Hierarchy View, right-click an entity, architecture, or module name in the editor and select Set as Top Level from the pop-up menu. This will populate the Hierarchy View with the structure of your top level.

As you make changes to the design, the Hierarchy View will not automatically refresh.

To refresh the Hierarchy View, use the refresh button (

If you want the selection in the Hierarchy View to follow your position in the editor, make sure to enable Follow Cursor from the More Actions (

Buttons in the Hierarchy View

These buttons are available in the Hierarchy View:

Expand the full hierarchy

Only show Instantiations (enabled)

Only show Instantiations (disabled)

Refresh the Hierarchy View

Collapse the hierarchy

More Actions

- Toggle Follow Cursor (links the Hierarchy View with the editor)

- Toggle Auto Refresh on save

- Sort by: Position

- Sort by: Name

- Sort by: Category

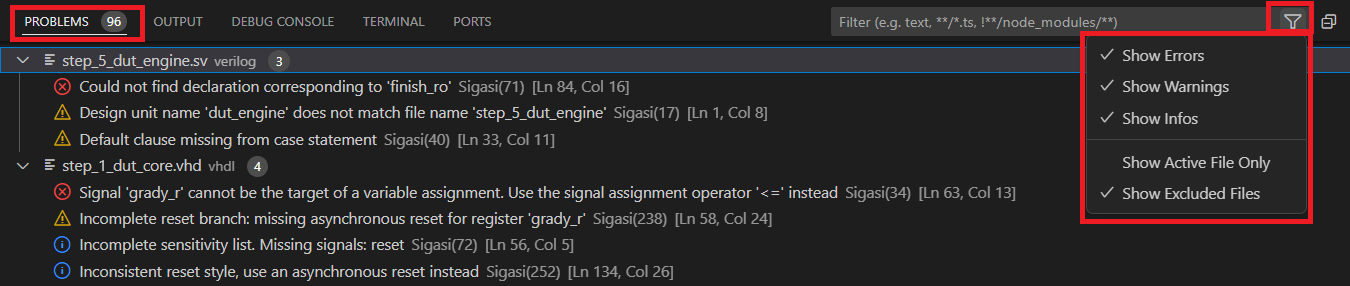

Problems View

The Problems View shows problems (errors, warnings, or info) related to your code. The Problems View is located at the bottom window by default. If it is not open, you can open it by going to View > Open View… and then selecting Problems.

Using the Problems View, you can navigate to the source of a problem by double-clicking on it. You can filter problems by using the filter icon located at the top-right.

Libraries View

The Libraries View shows the library mapping as well as the description style of the design units in all projects. You can use it to navigate to a particular design unit in your project. When you click on a file, it will open in the editor.

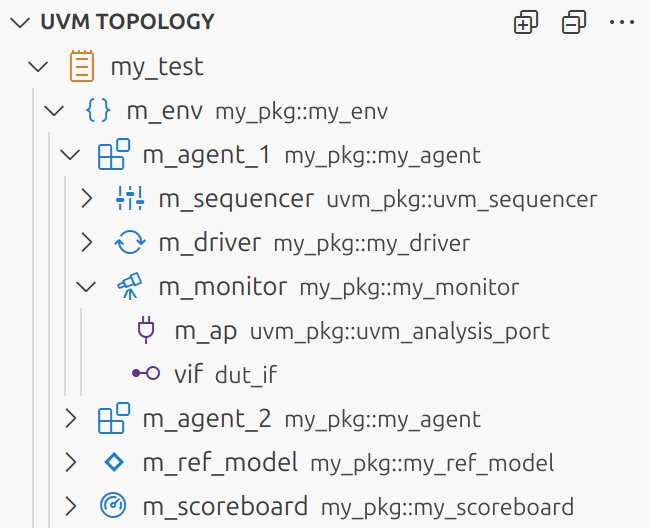

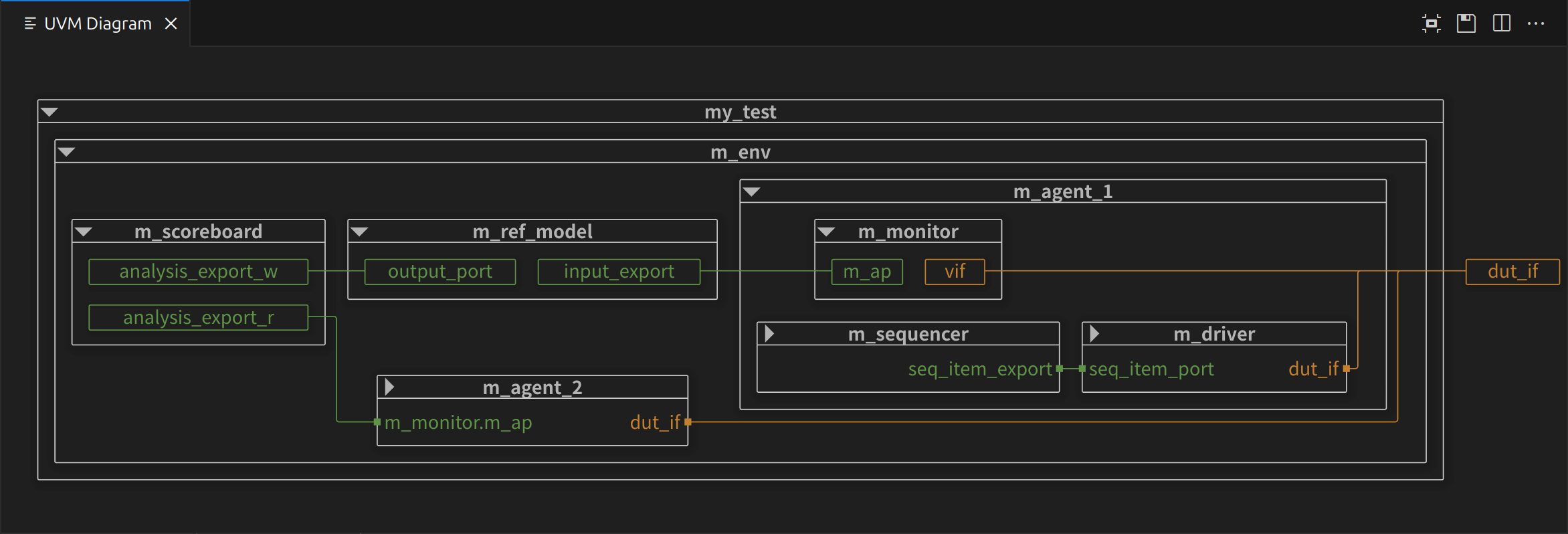

UVM Topology View

Sigasi Visual HDL Professional Edition or Sigasi Visual HDL Enterprise Edition, [Only for SystemVerilog]

The UVM Topology View shows the verification environment’s component topology. To view a component’s topology, right-click its class name in the editor and select Set as Root UVM Component from the pop-up menu. This will populate the UVM Topology View with the structure of the selected component and its children, including their ports and virtual interfaces.

As you make changes to the design, the UVM Topology View will automatically refresh.

You can navigate to a topology element in an editor by double-clicking it. Right-clicking an element opens a context menu with more navigation options: you can open the type, declaration, or instantiation of a selected element in an editor.

Buttons in the UVM Topology View

These buttons are available in the UVM Topology View:

Expand all components

Collapse all components

Other available actions:

- Sort components, ports, and interfaces alphabetically.

- Sort components, ports, and interfaces by position in the source code.

Preference View

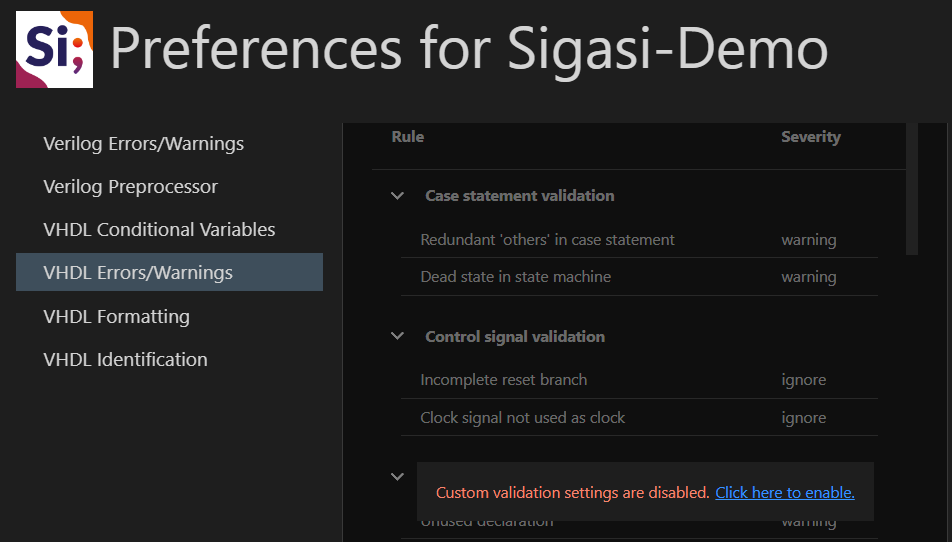

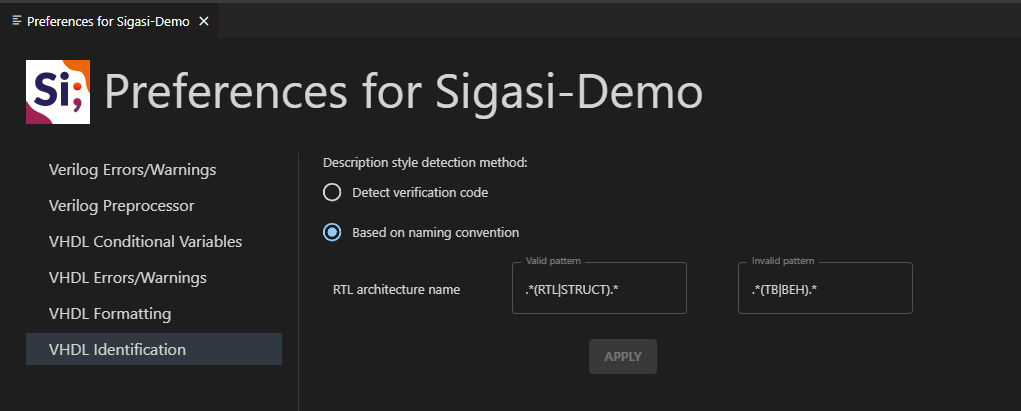

To open the Preference View, right-click the project, folder, or file you want to configure in the Sigasi Projects View. This view allows you to configure all preferences for the selected project, folder, or file.

- Change the severity of linting rules for your project

- Tweak validation parameters

- Modify conditional variables for VHDL 2019 projects

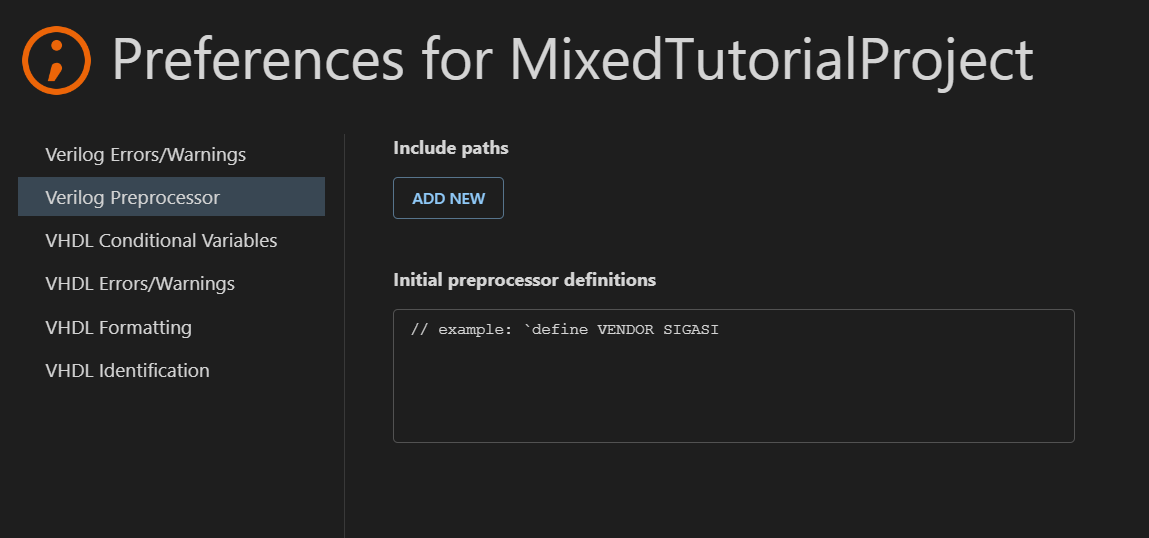

- Configure include paths and initial defines for the SystemVerilog Preprocessor

Make sure to click the APPLY button at the top right after making your changes.

Changes you make here will be stored in the .settings/ folder within your project.

This way, if you commit the settings with your project, they will be available for your fellow team members.

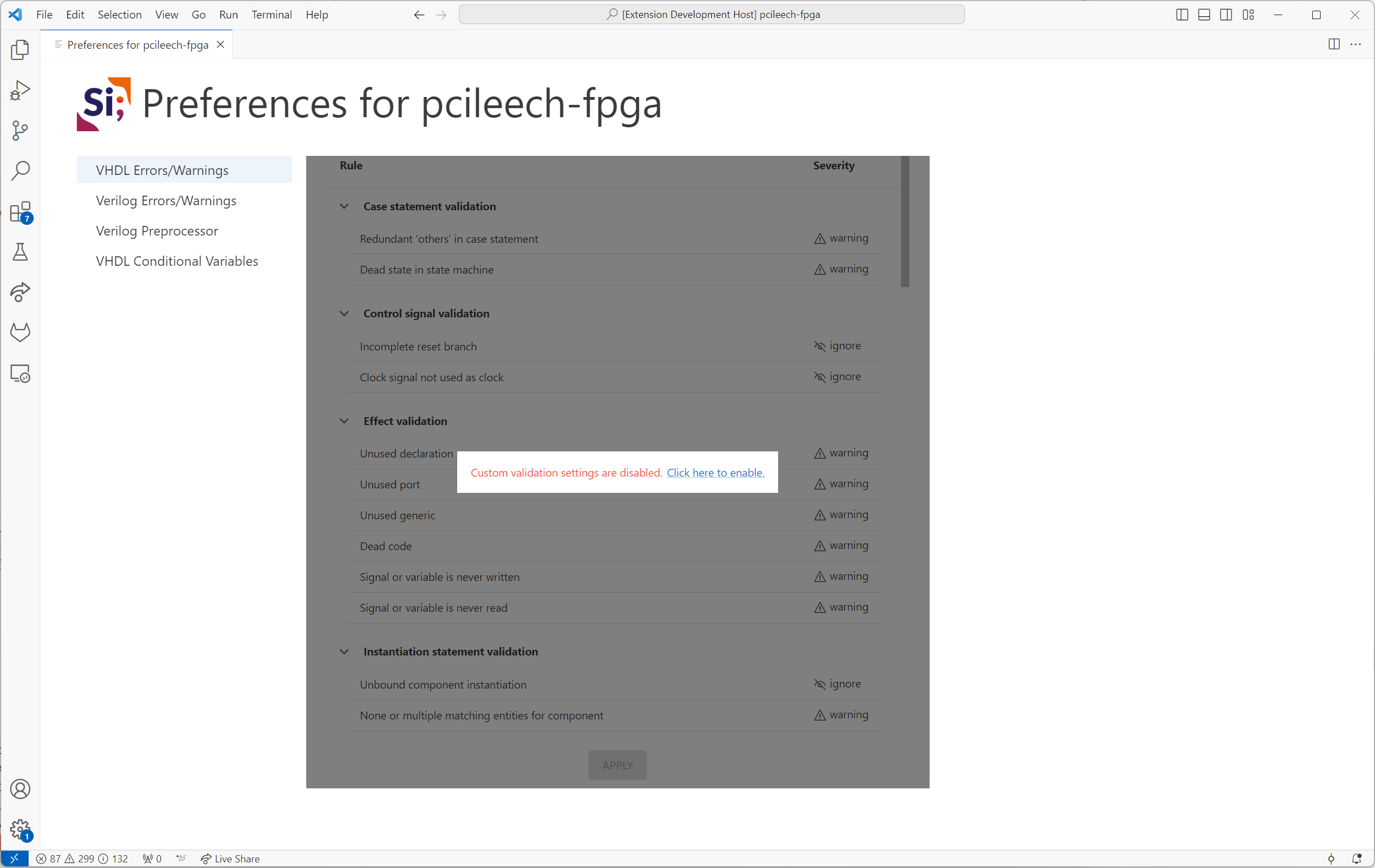

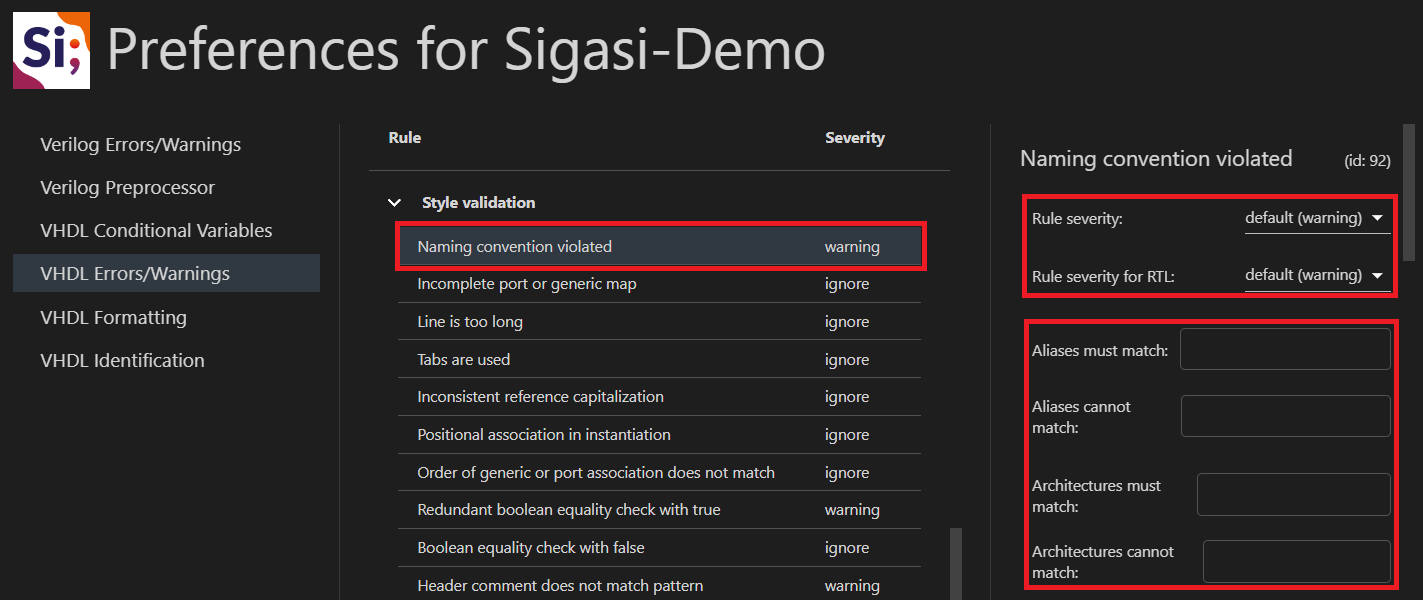

Configuring Linting Rules

You can configure linting rules per project, folder, or file by right-clicking a project, folder, or file > Open Preference View in the Projects View and then selecting Verilog Errors/Warnings or VHDL Errors/Warnings. In the middle of the page, Click here to enable to activate the rule configuration.

Refer to the linting documentation to learn more.

Graphical Views

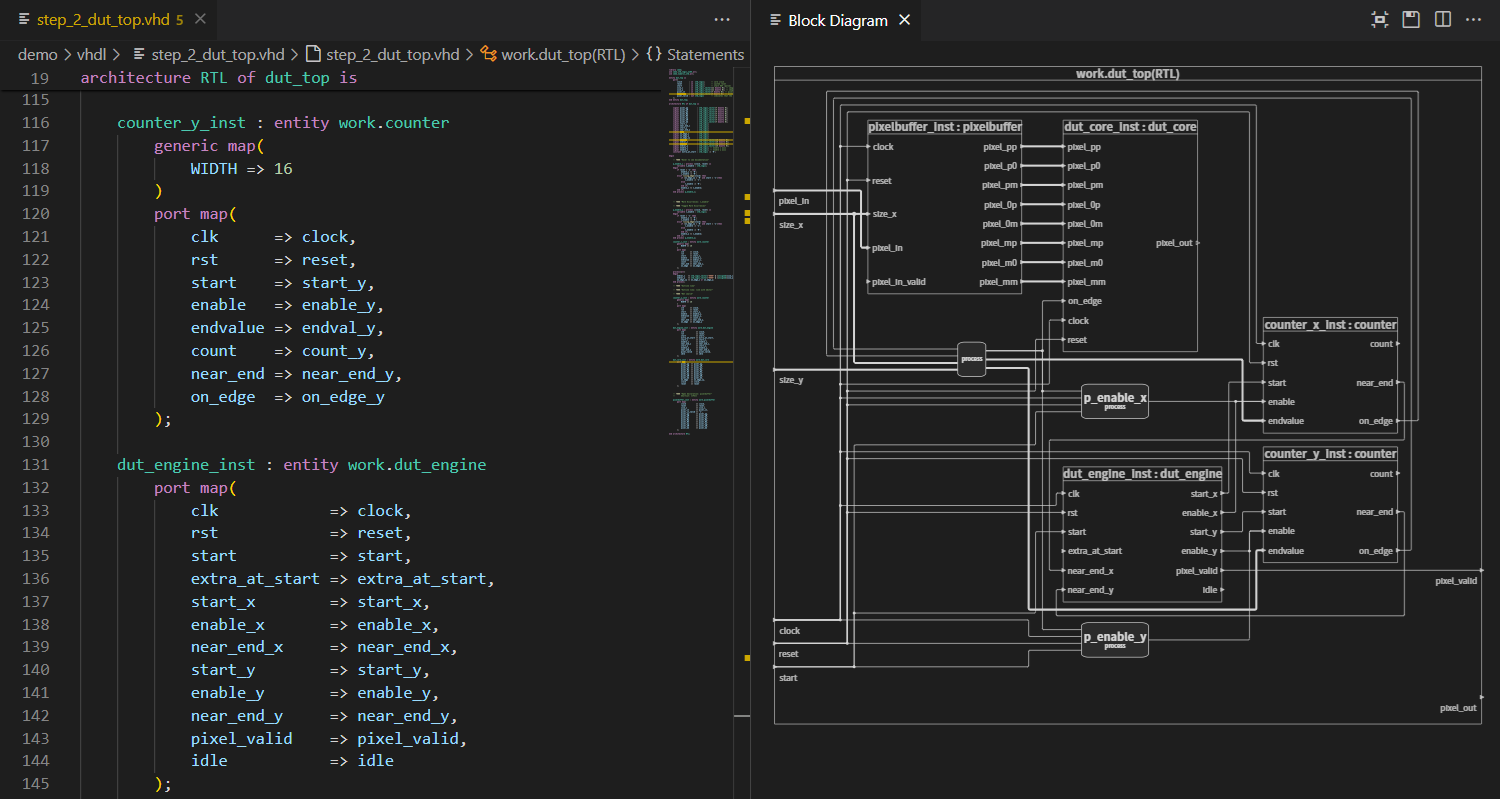

Block Diagram View

Sigasi Visual HDL Professional Edition or Sigasi Visual HDL Enterprise Edition

The Block Diagram View displays a graphical view of all architectures, modules, their instantiations, and generate constructs in your selected editor’s VHDL or SystemVerilog code.

VHDL processes and SystemVerilog always blocks are also shown in the block diagram.

This view automatically updates while you are editing your code and offers a convenient way to visually inspect and navigate your code, even when it’s unfinished or broken.

You can open the Block Diagram View by right-clicking in the editor and selecting Show In > Block Diagram. Alternatively, you can open the view using the command palette Ctrl+Shift+P and typing Sigasi: Open Block Diagram.

You can double-click blocks, ports, or wires to navigate to the corresponding HDL code. If you want to go into a block, you have to select it, right-click, and click Open Entity Declaration, Open Architecture, or Open Module.

To find an object in the Block Diagram, you can navigate from your code to the Block Diagram. In your code, right-click a signal, port, process, generate, or instantiation and select Show In > Block Diagram - just like when opening the Block Diagram View the first time. If the Block Diagram is already open, the corresponding element will be highlighted, and the Block Diagram View will center upon it.

You can export the Block Diagram View to an image with the save button on the toolbar. Both SVG and PNG are supported. Choose a *.svg filename for SVG export or a *.png filename for PNG export.

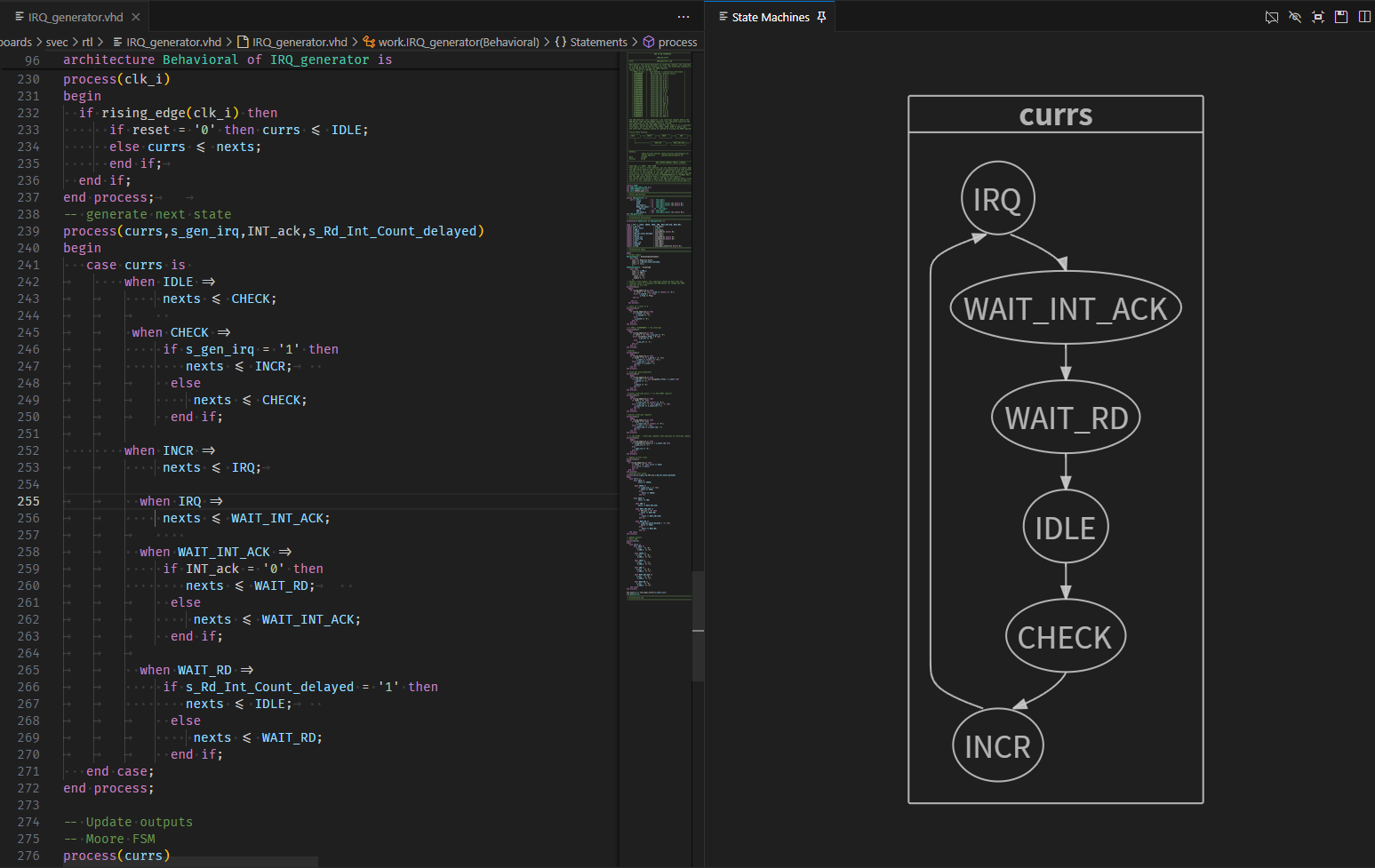

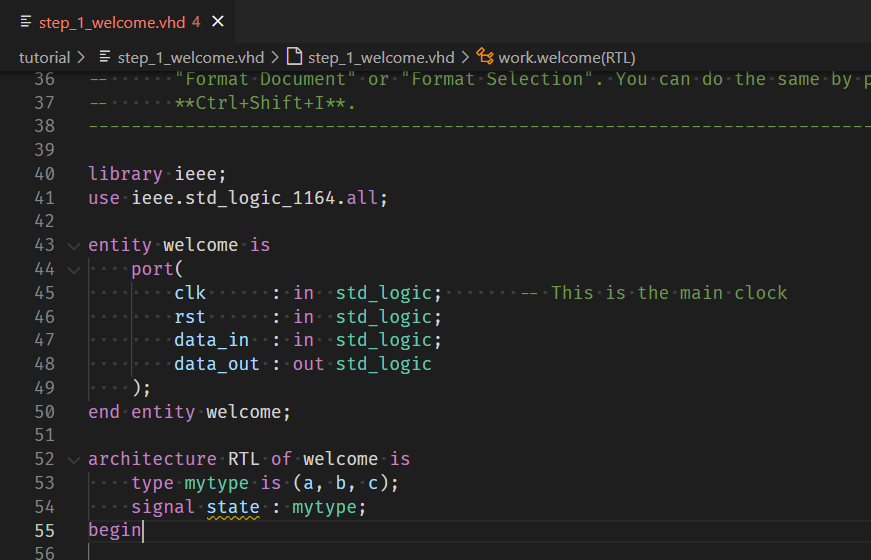

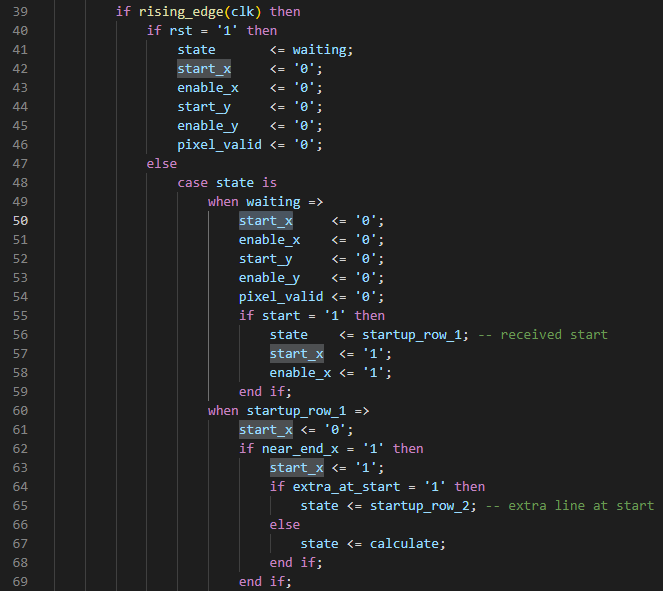

State Machines View

Sigasi Visual HDL Professional Edition or Sigasi Visual HDL Enterprise Edition

The State Machines View displays a graphical (bubble diagram) view of all state machines in your current VHDL or SystemVerilog editor. This viewer automatically updates while you are editing your code and offers a convenient way to visually inspect and navigate your code, even when your code is unfinished or broken.

You can open the State Machine View by right-clicking in the editor and selecting Show In > State Machines. Alternatively, you can open the view using the command palette Ctrl+Shift+P and typing Sigasi: Open State Machines Diagram.

If you have documented your state transitions (i.e., the assignments), the comments will be added as text to the transitions in the view.

You can double-click nodes or transitions to navigate to the corresponding HDL code.

With the hide comments button, you can toggle the display of comments on edge labels.

With the hide conditions button, you can toggle the display of comments on edge labels. These labels show the code comments of the transition statements.

You also have the option to Zoom In, Zoom Out, or Zoom to Fit.

You can export state machines to an image with the save button. Both SVG and PNG are supported. Choose a *.svg filename for SVG export or a *.png filename for PNG export.

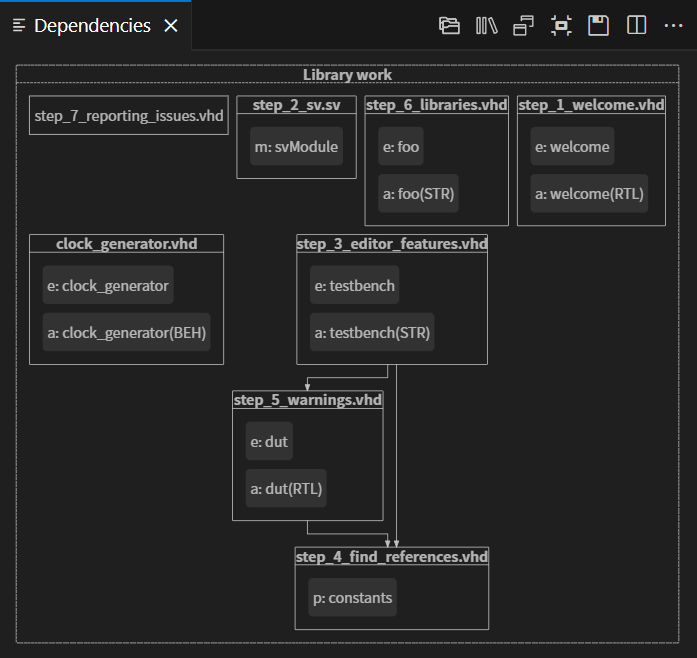

Dependencies View

The Dependencies View visualizes the dependencies of your VHDL, SystemVerilog, or mixed language projects. This view shows the relationships between your source files and makes it easy to see top levels and important packages. The Dependencies View also makes it easy to detect orphaned files.

The view is automatically updated each time you save your files.

You can open the Dependecies View by right-clicking in the editor and selecting Show In > Dependencies.

The Dependencies View has the following options:

shows dependencies of the entire project, which you can uncheck to focus on the active editor dependencies only

groups design files per library

shows design units inside design files prefixed with an abbreviation of their kind architecture, module, package, etc.

The Dependencies View can help you navigate, too. Double-click a file name in the diagram to open the corresponding editor.

You can export this diagram for documentation by clicking the save button.

UVM Diagram View

Sigasi Visual HDL Professional Edition or Sigasi Visual HDL Enterprise Edition, [Only for SystemVerilog]

The UVM Diagram View displays a graphical representation of the UVM component structure through an intuitive graphical display. It visualizes the relationships between components, their hierarchical arrangement in the topology, the connections between ports, and the referenced design interfaces. The dynamic expansion of the diagram allows for efficient tracking of connections throughout the UVM component structure.

Similar to the UVM Topology View, this diagram offers a set of navigation options for each element (both by double-clicking on elements and through the context menu), allowing you to access an element’s types, declarations, or instantiations. Double-clicking on a port connection line navigates to the corresponding connect method call in the source code.

Like other diagram views, you can find buttons on the toolbar to Zoom to Fit and export the UVM Diagram as an image (supports both SVG and PNG).

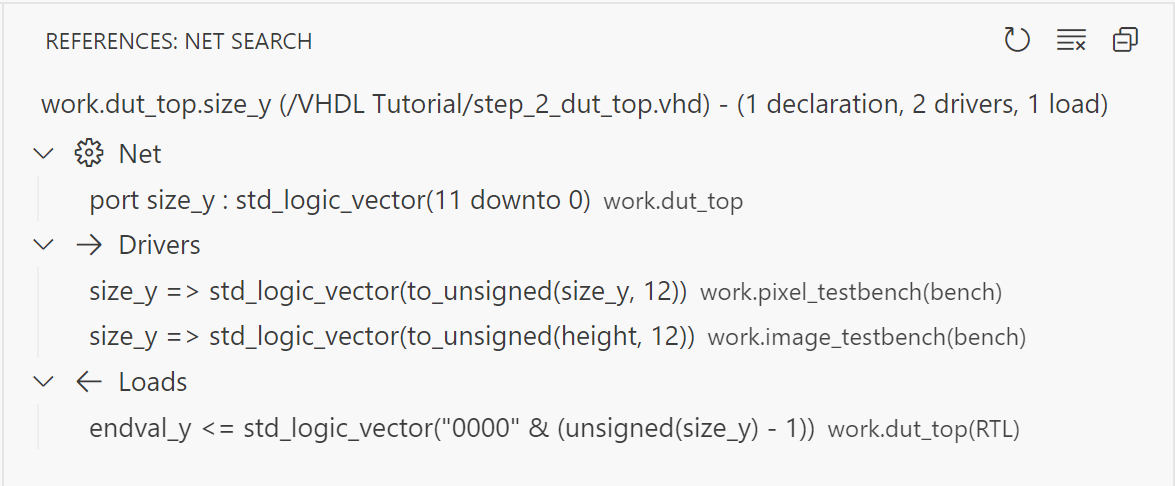

Net Search View

[Only for VHDL]With Net Search, you can find a net’s loads and drivers. A net is defined as a signal or port and all other signals and ports that are directly connected to it. The loads are where you read the value of a net, and the drivers are where you write to it.

To find the entire signal or port net, place your cursor on the identifier and right-click. Then select Find Net. Alternatively, you can press Ctrl+Shift+H.

The Net Search View will appear. For big designs, it might take a while before the results appear.

From the Net Search View, you can navigate to the code by double-clicking the search results.

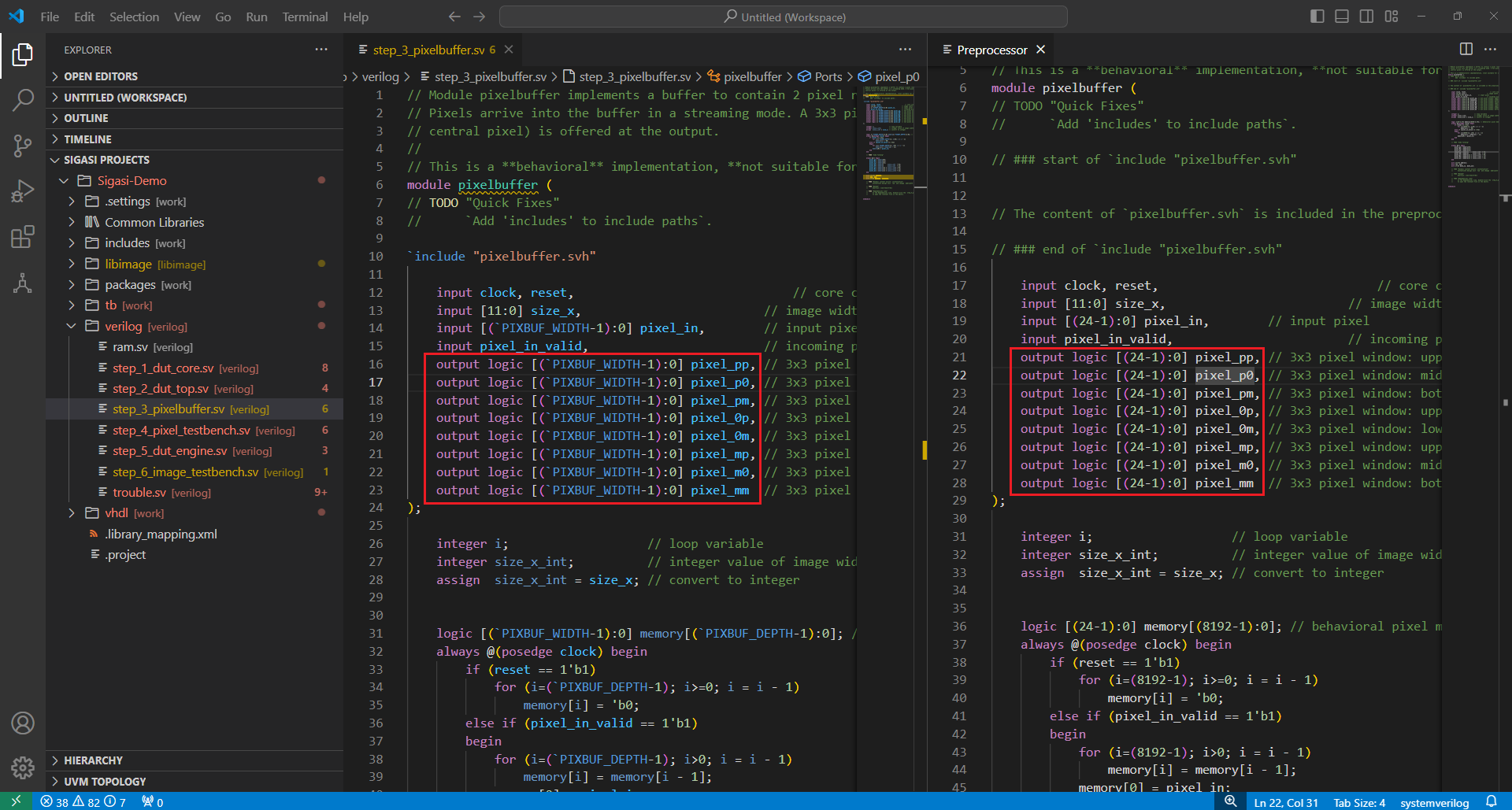

Preprocessor View

[Only for SystemVerilog]In order to open the Preprocessor View, which shows preprocessed text, right-click in the editor and select Show In > Preprocessor.

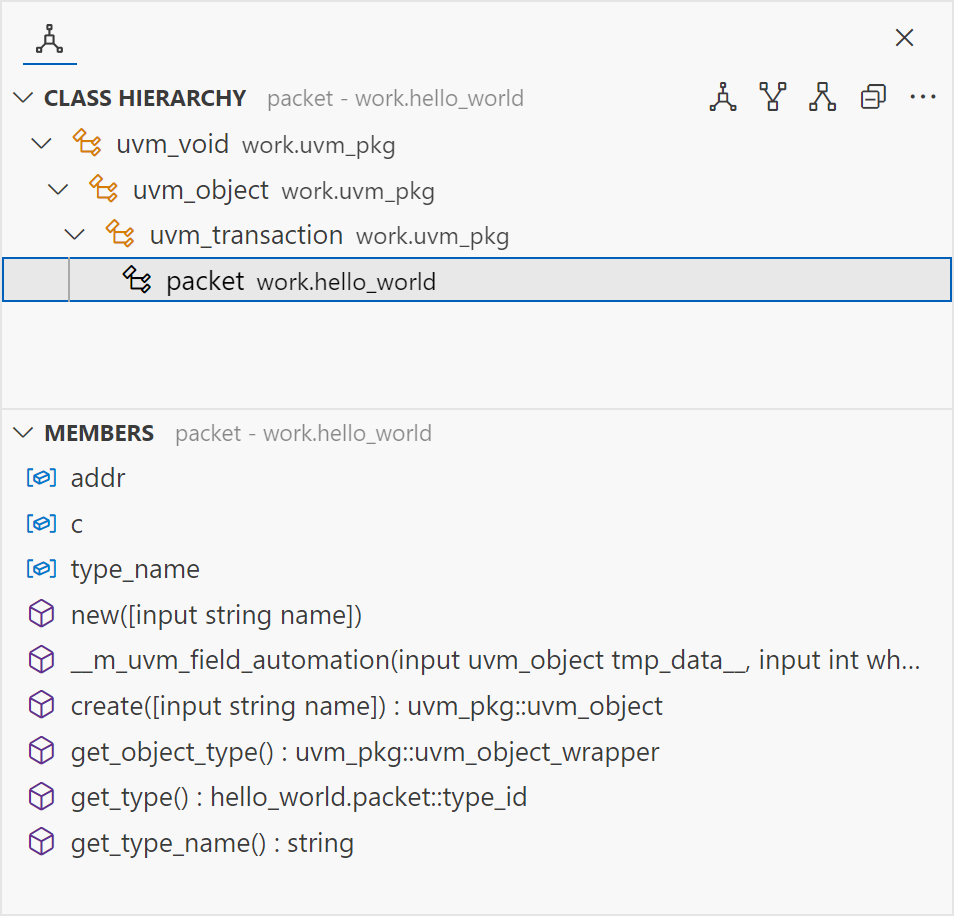

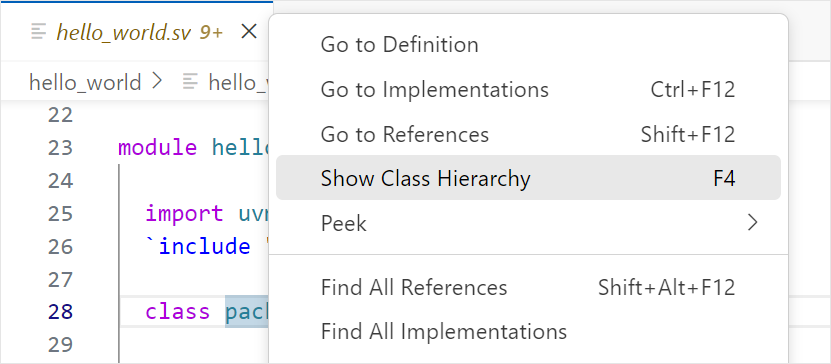

Class Hierarchy View

[Only for SystemVerilog]The Class Hierarchy View displays more information about the hierarchy of a class. It consists of a hierarchy tree and a list of its class members. To open the Class Hierarchy of a class, click the class name, right-click, and select Show Class Hierarchy (or press F4).

Class Hierarchy Tree

The class hierarchy tree displays the superclasses, subclasses, or both.

| Icon | Command | Description |

|---|---|---|

| Class Hierarchy | Displays all superclasses and subclasses. |

| Superclass Hierarchy | Displays all superclasses and implemented interface classes. |

| Subclass Hierarchy | Displays all subclasses that extend or implement the selected (interface) class. |

| Toggle Show Qualified Class Names | Shows the qualified name next to each class. |

Member List

The member list shows all members (fields, functions, tasks, and constructors) of a selected class in the class hierarchy tree.

The icon shown in the view describes the current active state of the members list options.

| Icon | Command | Description |

|---|---|---|

| Show Inherited Members | Shows members inherited from superclasses. |

| Hide Inherited Members | Hides members inherited from superclasses. |

| Show Fields | Shows fields in the members list. |

| Hide Fields | Hides fields in the members list. |

| Toggle Sort By Defining Class | Sorts members by the class in which they are defined. |

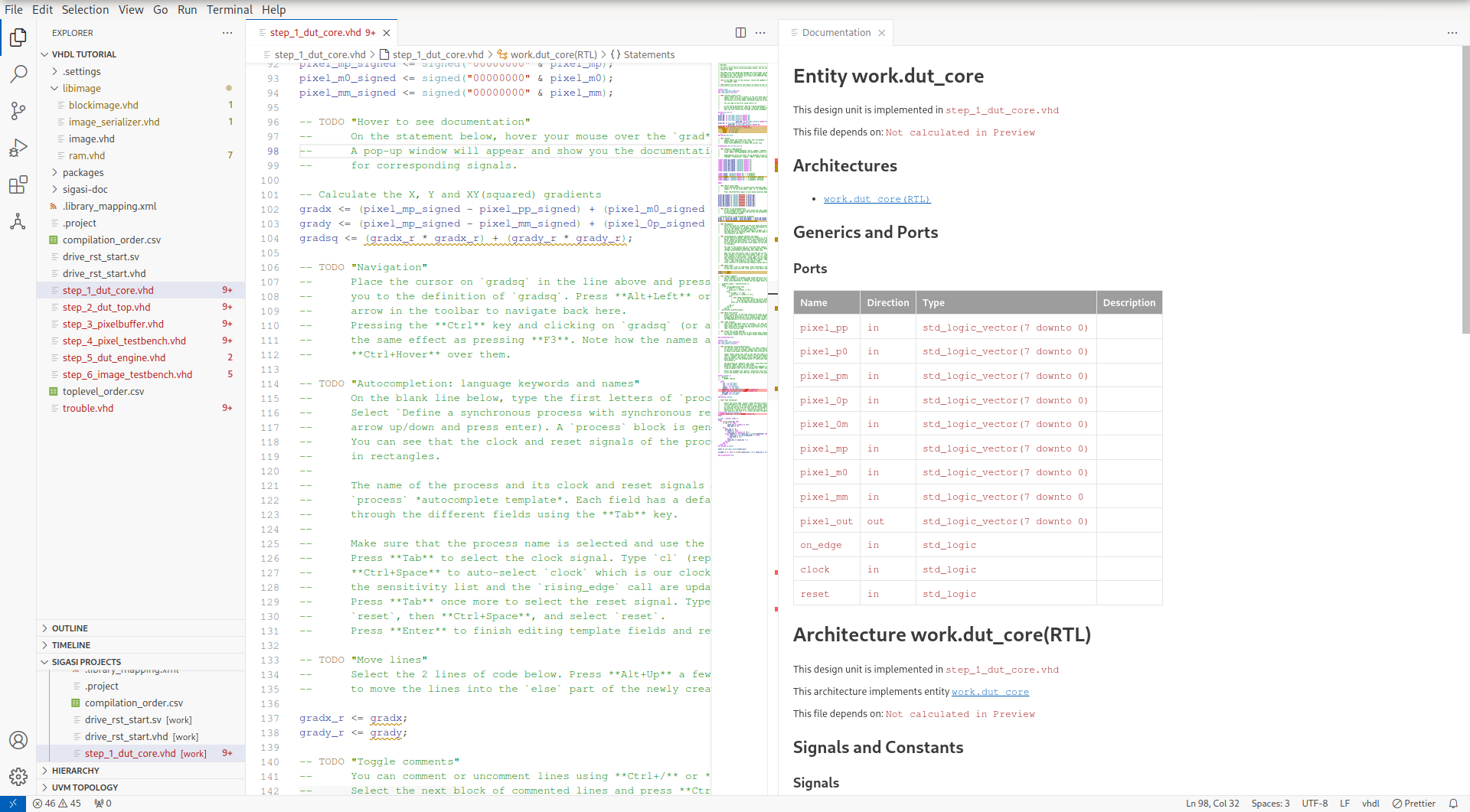

Documentation View

Sigasi Visual HDL Professional Edition or Sigasi Visual HDL Enterprise Edition

The Documentation View gives you a live preview of the automatic documentation SVH can generate for your project.

[Back to top]

Sigasi Visual HDL in the VS Code Editor

The VS Code Editor shows the content of files and allows you to edit them. It has a tabbed view such that multiple files can be opened simultaneously. The active file is the one currently selected.

VHDL and SystemVerilog Editor

The VHDL and SystemVerilog (or Verilog) editors are optimized to help you browse and edit VHDL and SystemVerilog code. Most browsing and editing features are similar for both languages.

Language-specific features are explained in the “VHDL Specific” and “Verilog and SystemVerilog Specific” sections.

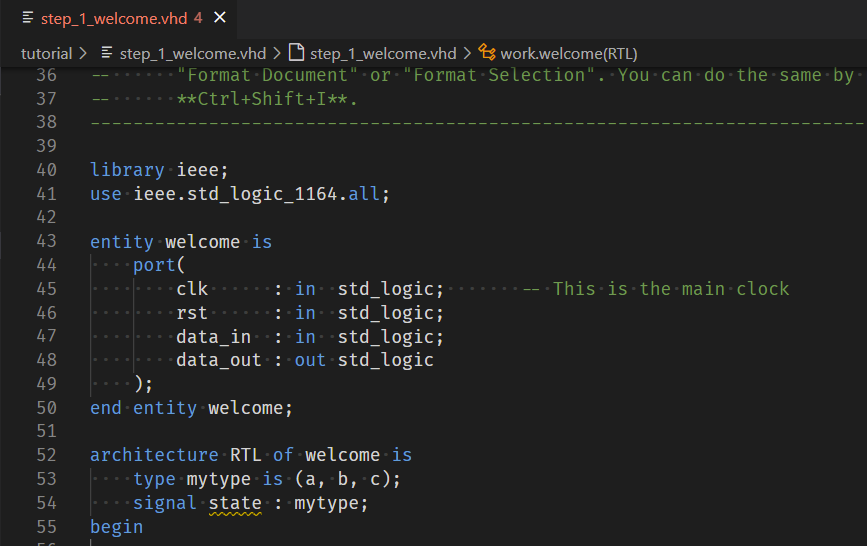

Code Highlighting (Syntax Coloring)

The Sigasi Visual HDL (SVH) extension supports syntax and semantic highlighting.

- Syntax highlighting: colors code according to lexical classification (such as keyword or string).

- Semantic highlighting: colors code according to meaning (different colors for constants and signals).

Note that some VS Code themes might not support semantic highlighting. If you appear to be missing this feature, make sure you’re using one of the default VS Code themes. If the feature still doesn’t appear, get in touch with support .

- In themes that support semantic highlighting, you’ll see that names like those of a

port,signal, ortypeare a different color from language keywords. - In themes that do not support semantic highlighting, names like those of a

port,signal, ortypewill have the default text color.

The latter might also happen when there’s no .project file in your root directory. Without this, the SVH extension will not start and only provides basic syntax highlighting.

See also:

Type-time Syntax Error Reporting

SVH marks VHDL and SystemVerilog syntax errors while you type. It will also report broken SystemVerilog preprocessor code.

Project Exploration and Navigation

SVH offers powerful techniques to explore a file or project and navigate through it. This section covers: Occurrence Highlighting, Find References, Go To Definition and Hyperlinks, and Hovers.

Occurrence Highlighting

Clicking on an identifier highlights it and all other occurrences of the identifier that refer to the same object. Note that this occurrence highlighting is intelligent: it is not based on the identifier’s string value but on the object to which the identifier refers. Only true references will be highlighted, not occurrences in strings, comments, or other such instances.

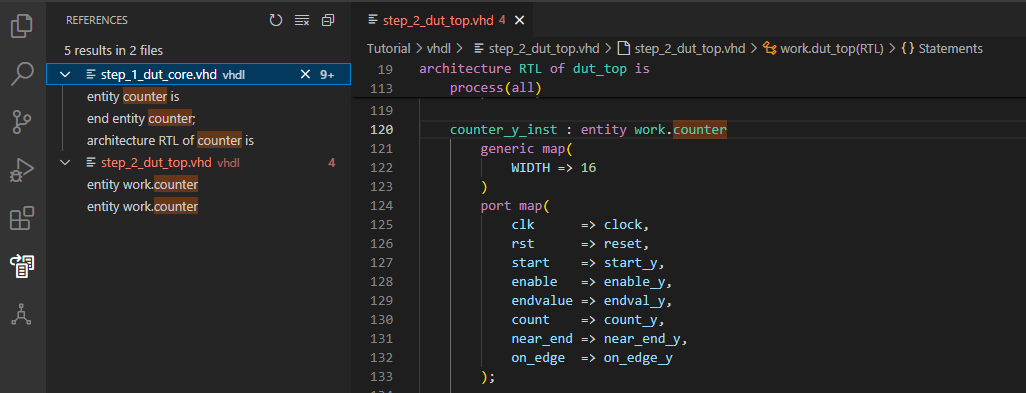

Find References

To look for occurrences of a given identifier throughout your design, place your cursor on the identifier and right-click. Then select Find All References.

A search window will appear to the left of your workbench, displaying all occurrences of the selected identifier. You can easily navigate through all occurrences by clicking the items in the list. Note that all occurrences are also highlighted in the editor, making them easily recognizable.

Go To Definition and Hyperlinks

You can easily navigate to the declaration of any port, signal, entity, etc. Place the cursor on the identifier, right-click, and select Go to Definition. The editor immediately jumps to the declaration.

You can also navigate your code like a web browser by clicking hyperlinks. If you press and hold the Ctrl key, hyperlinks will appear in your editor. If you click a link (while holding the Ctrl key), you will navigate to the target of the link.

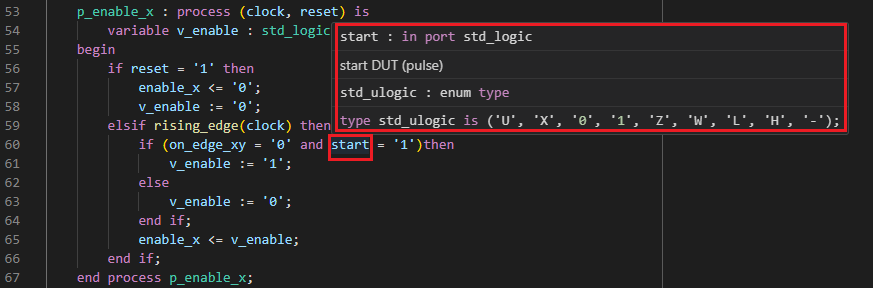

Hover

To learn more about the declaration of a given identifier, you can hold your mouse over it. After a short time, a popup will show you the name and datatype of the signal. This technique is called hovering.

Hover pop-ups can show different kinds of information:

- datatype

- comments: inline documentation written for the declaration (association rules)

- value: the value of constants

- errors or warnings: a description of the problem, if the given identifier has an error or warning associated with it

- binary/decimal conversion: for hexadecimal, octal, or binary values, the decimal equivalent

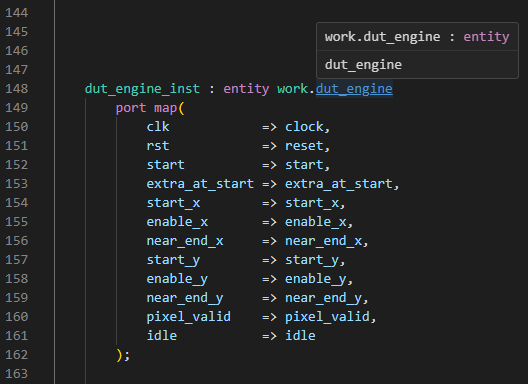

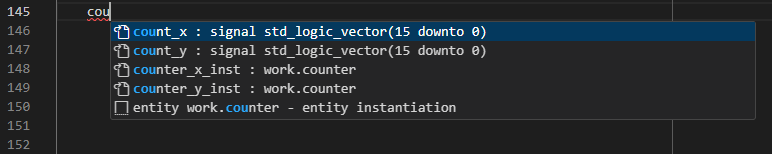

Autocomplete and Content Assist

SVH provides powerful autocompletion capabilities. This means that the tool can help you complete identifiers and constructs as you are working on the code. Like other tools, it provides syntax-based autocompletion depending on the HDL language you’re using. However, it goes much further: it can also provide autocompletion based on the design context because it knows everything that has been declared in the design.

Autocompletion Interface

Autocompletion can come from different sources, as discussed in the following sections. However, the user interface to initiate it is always the same. SVH will suggest appropriate autocompletion options at any point as you enter code.

You can also trigger autocompletion suggestions by first placing your cursor where you want to autocomplete and then pressing Ctrl+Space.

Based on the Design Context

SVH uses its knowledge of designs to provide intelligent autocompletion that boosts your productivity tremendously.

The tool understands the current context, which identifiers are visible, and which constructs are legal at any given point in the code. As you start typing and ask for autocompletion, it will suggest appropriate identifiers as autocompletion candidates.

SVH provides autocomplete suggestions for:

- component declarations

- component instantiations

- entity instantiations

- module instantiations

- case statements (based on variables/signals with an enumeration type)

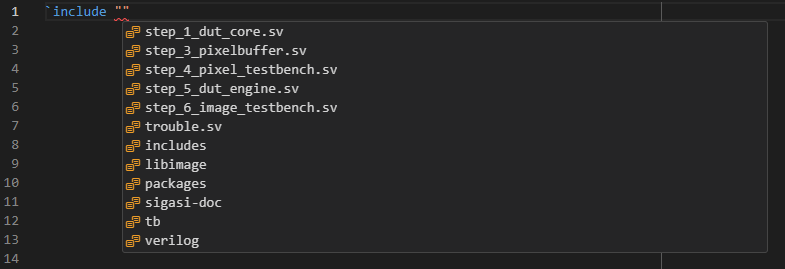

- SystemVerilog preprocessor/macro directives, e.g.,

`defineor`ifndef - SystemVerilog include paths (

`include ""): triggering autocomplete between the double quotes will present a list of files and folders. If you select a folder, trigger autocomplete again to get completions in this folder.

Based on Templates

SVH can help you declare VHDL and SystemVerilog constructs, using autocomplete based on templates. SVH comes preconfigured with templates for all common declarations and statements, including (for VHDL):

- function, procedure

- process

- type: enum, file, range, array, record

- signal, constant, variable

- component

- entity

- architecture

- entity/architecture pair

- package/package body pair

- and much more

Some autocompletions are templates that require further user input. In such a case, the editor window will go into a special template editing mode after performing an autocomplete. Use TAB to go through the items that have to be modified or completed. When done, press ENTER to return to normal editing mode. The cursor will be placed at an appropriate position to continue working.

You can also configure your own templates as described in User-Defined Code Snippets.

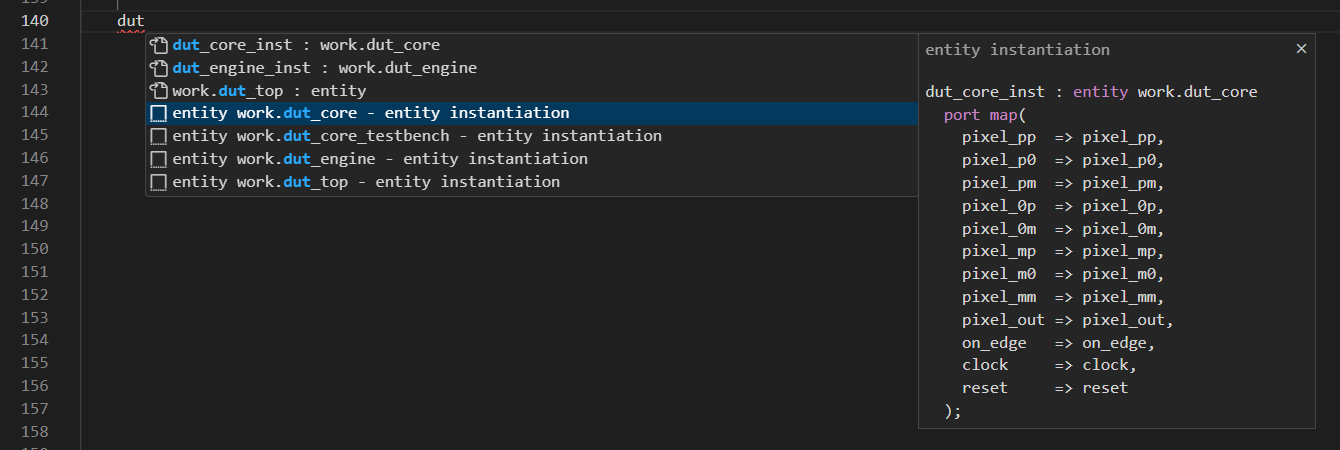

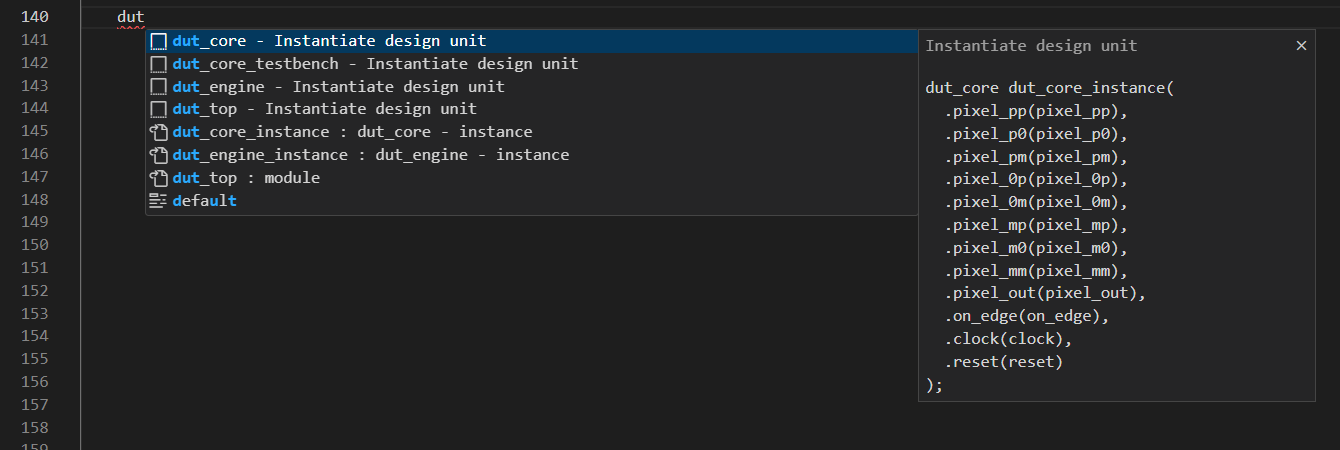

Instantiating a Design Unit

Note: In other tools, this feature may be known as paste as instantiation or port translation.

SVH knows all design units (entities, components, and modules) in a design and their ports and parameters or generic interfaces, and can therefore automate much of the instantiation process. At the point in the code where you normally enter a design unit’s name, use autocompletion instead to suggest a list of possible design units. Upon selection, the tool will complete the instantiation with a generic or parameter list, and a port list with named associations. As an initial suggestion, each actual parameter will have the same name as its formal parameter. Of course, the actual parameter names need to be reviewed and edited by the user. Therefore, the editor will go into template editing mode after the autocompletion.

Note that design units will only be shown if they are visible in the current scope.A number of VHDL-specific and Verilog and SystemVerilog-specific autocompletes are available in SVH.

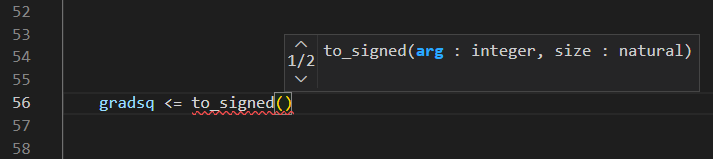

Signature Helper

When you invoke a function in VHDL or Verilog, SVH will list that function’s arguments in a pop-up window that will appear once you type an open parenthesis.

The Signature Helper also activates when instantiating a VHDL entity or a Verilog module by listing the ports or generics of that entity or module.

Smart Indentation

When you press enter, SVH automatically adjusts the indentation of

the current and the new line. Depending on the content of the preceding

line, SVH will automatically increase or decrease the indentation

level. For example, it may add an extra indent after a module or an entity and remove an indent for

the matching endmodule or end entity.

See also:

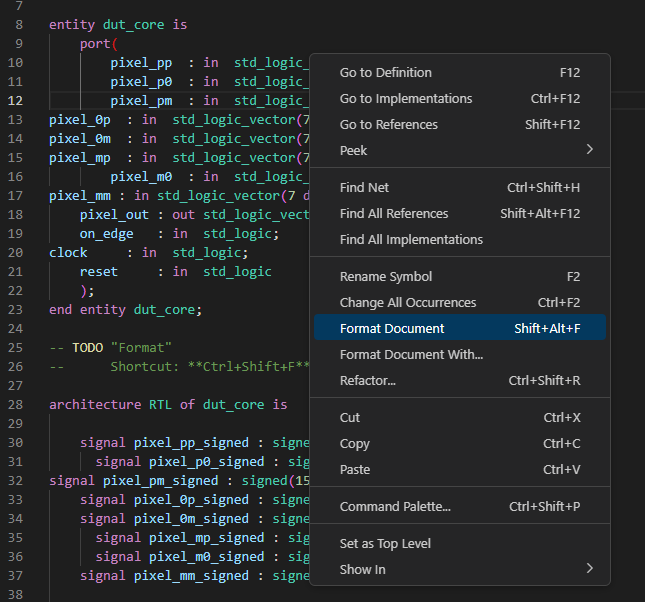

Code Formatting

Automated consistent code formatting makes code more readable and understandable for developers, whether working on their own code or when cooperating with colleagues. In order to format your code, right-click in the editor and select Format Document.

Read more in the VHDL code formatting and Verilog and SystemVerilog code formatting sections.

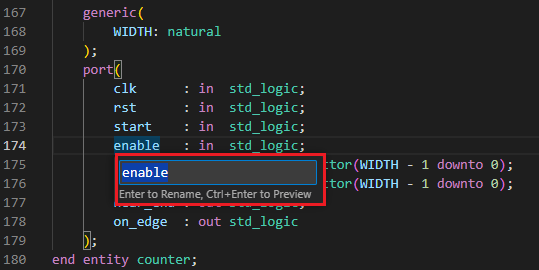

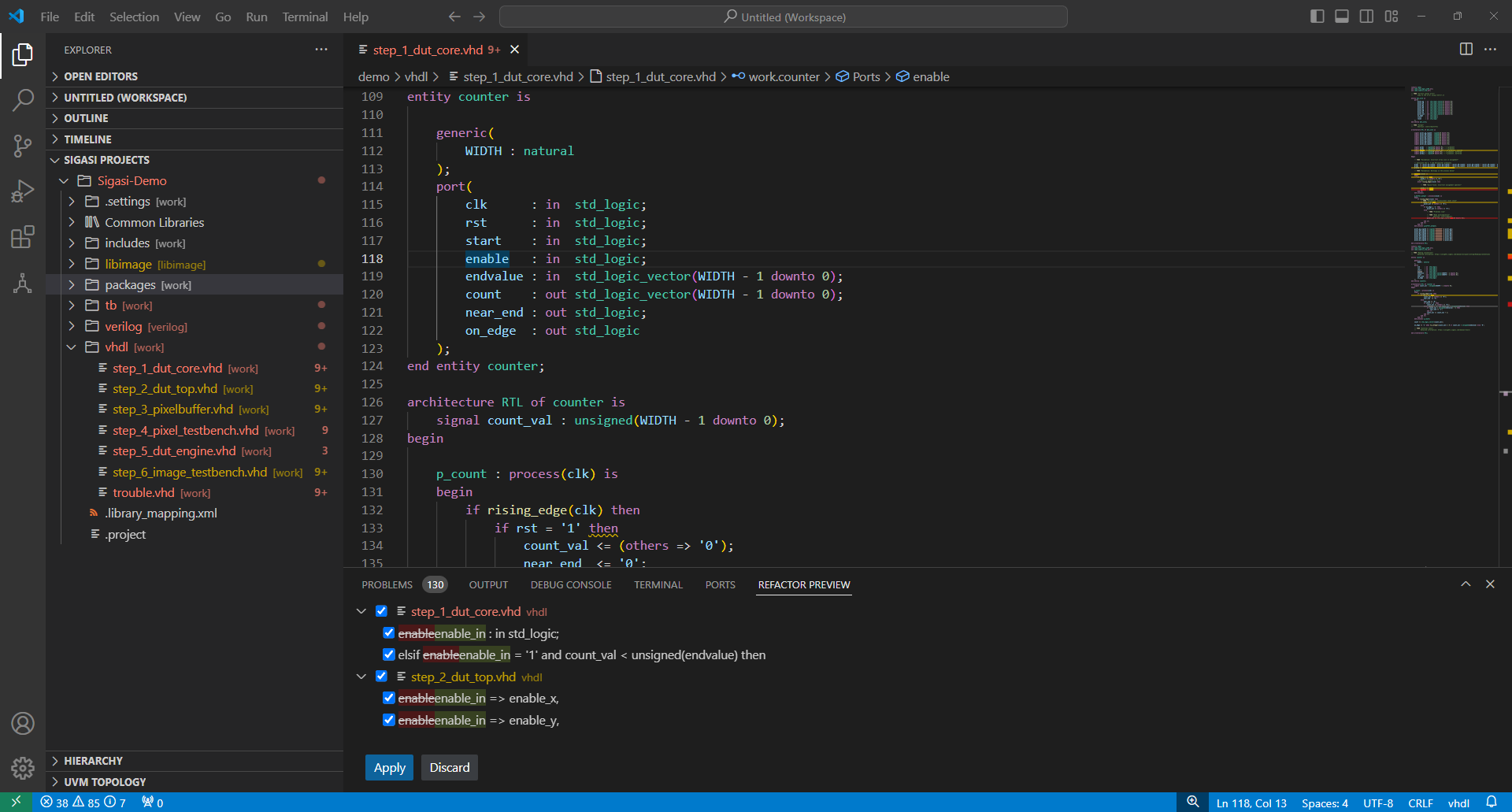

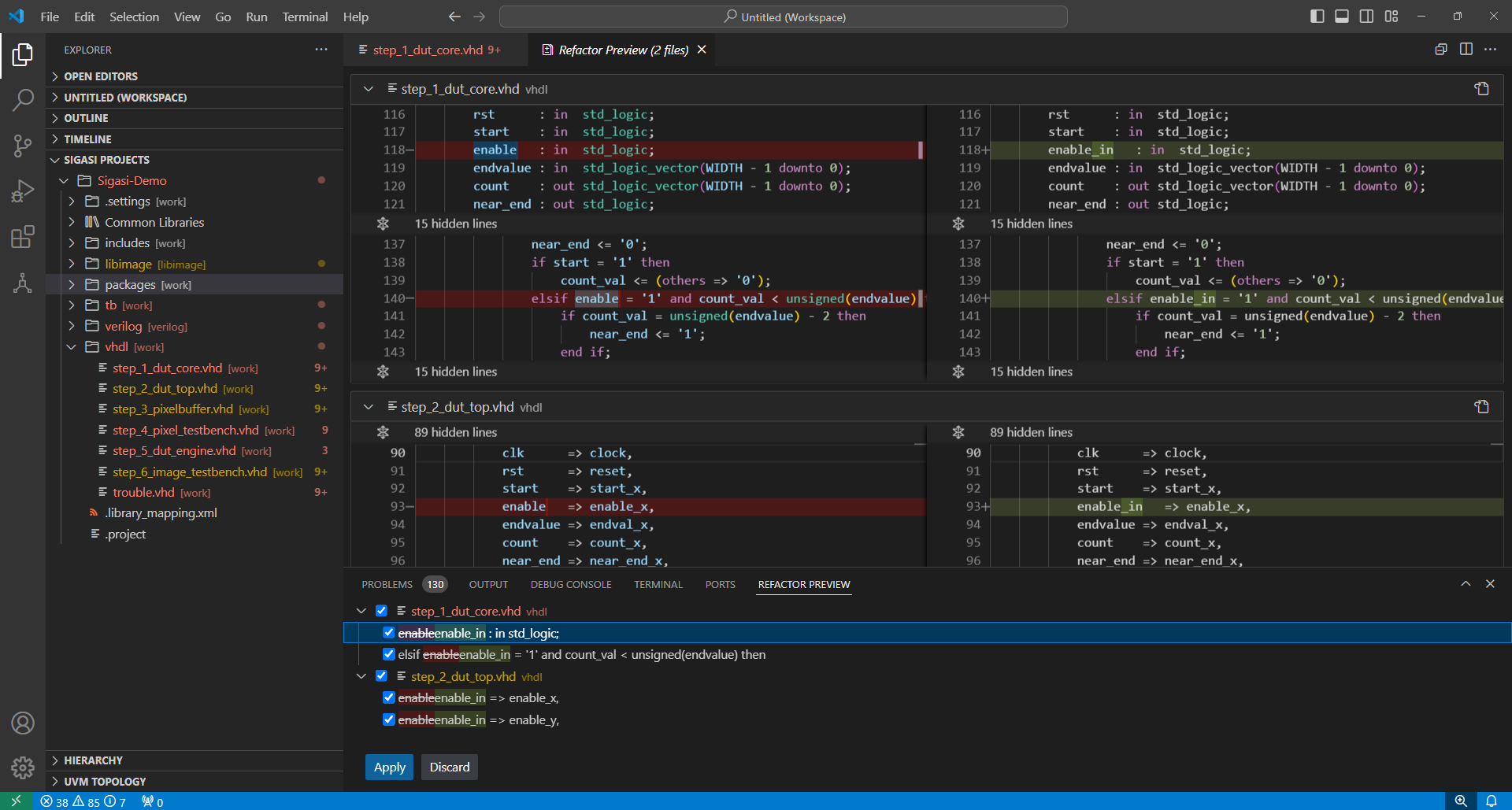

Rename Refactoring

Right-click on any identifier (VHDL or SystemVerilog) and select Rename Symbol to change the name of the associated declaration and all its references. Once you select Rename Symbol a little dialog box will pop up.

At this point, you can type the new name and press ENTER. This will rename the declaration of that symbol and all its references. Before renaming, you can also press CTRL+ENTER to see a preview before making changes across your files.

At the bottom, a Refactor Preview tab appears and lists the summary of the changes to be made. Clickig any of the items in the list visualizes all changes side-by-side.

You can then click the APPLY button to accept the changes or click the DISCARD button to cancel the renaming action. Note that this feature does not rename references in comments.

User-Defined Code Snippets

VS Code supports user-defined code snippets, as explained here . To add snippets yourself, follow the steps below.

- Open the Command Palette (Ctrl+Shift+P) and type Snippets.

- Select Snippets: Configure User Snippets.

- Type vhdl or systemverilog to open the corresponding JSON file where you can add your snippet. See the examples below.

VHDL Snippet Example

{

// Place your snippets for VHDL here.

"package declaration": {

"prefix": "package",

"body": [

"package ${1:name} is",

"\t$0",

"end package $1;"

],

"description": "Insert package declaration"

}

}

SystemVerilog Snippet Example

{

// Place your snippets for Verilog and SystemVerilog here.

"always posedge clk": {

"prefix": "always",

"body": [

"always @(posedge ${1:clk}) begin",

"\t$0",

"end"

],

"description": "Insert an always block with posedge clock"

}

}

Other Editor Features

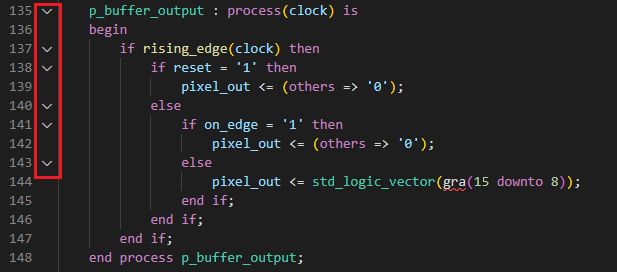

Code Folding

If you work with large files, you might want to hide certain pieces of your code. This can be done with code folding. Certain constructs, such as if-statements or process-statements, can be folded so that they are displayed as a single line in the editor view. You can do this by clicking the little arrow symbols next to the statement or declaration.

Add Parentheses or Create a String

If you select a region and press ( or [, the tool will enclose the selected region with the matching closing parenthesis, ) or ].

If you select a region and press ( or [, the tool will enclose the selected region with the matching closing parenthesis, ) or ].

This works for both regular and multi-line strings and with either single or double quotation marks.

You can configure this feature with the key editor.autoClosingQuotes.

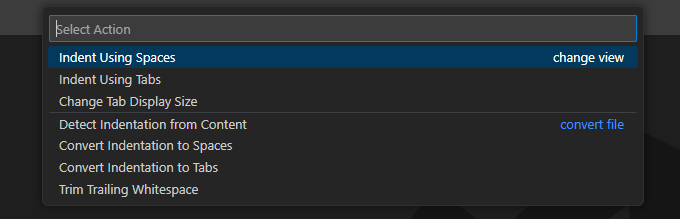

Indentation and Whitespace

You can access the spaces customization controls at the bottom-right of the VS Code window.

If you click Spaces, a dialog box appears at the top-middle of the window.

The options in this menu are only valid for the file in the editor. Before using these actions, make sure your file has been saved.

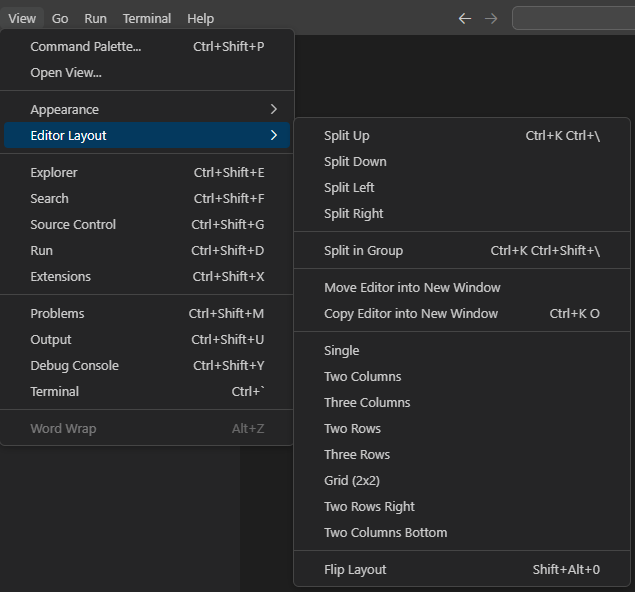

Split Editor

The VS Code editor can be split into independent viewports that access the same file buffer. To split the editor, go to View > Editor Layout and select the desired action.

There can be more than two horizontal or vertical splits within an editor.

Sticky Scroll

You can use sticky scroll to navigate through your HDL code more easily. The stickiness is based on the code folding regions.

You can configure this feature with the key editor.stickyScroll.enabled.

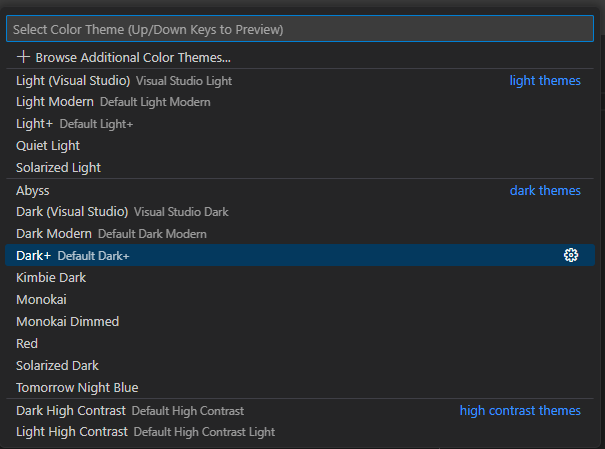

Customize Color Preferences

You can customize color preferences in SVH. Open the Command Palette via Ctrl+Shift+P, type color, and select Preferences: Color Theme from the list. You will get a list of themes from which to choose.

Side-By-Side Comparison

With SVH, you can compare two files side-by-side.

- Previous versions (local history or version control)

- Comparing two files

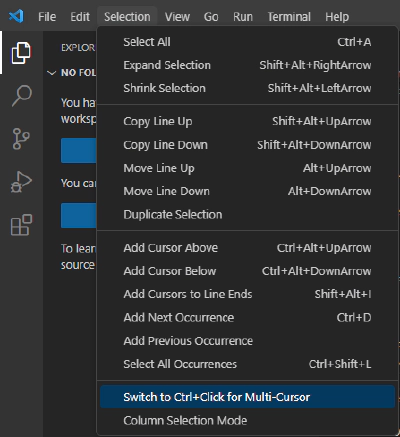

Multi-Cursor Support

In order to enable multi-cursor support, open the Command Palette via Ctrl+Shift+P, type multi, and select Toggle Multi-Cursor Modifier from the list.

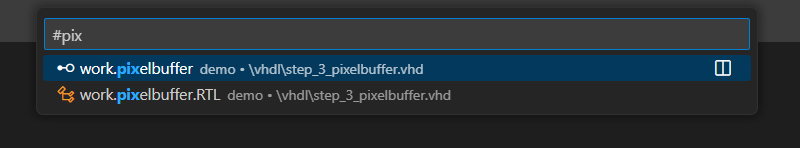

Open Design Unit

In order to open a design unit in your project, press Ctrl+P, filter the list by typing, and select the design unit that you want to open from the list.

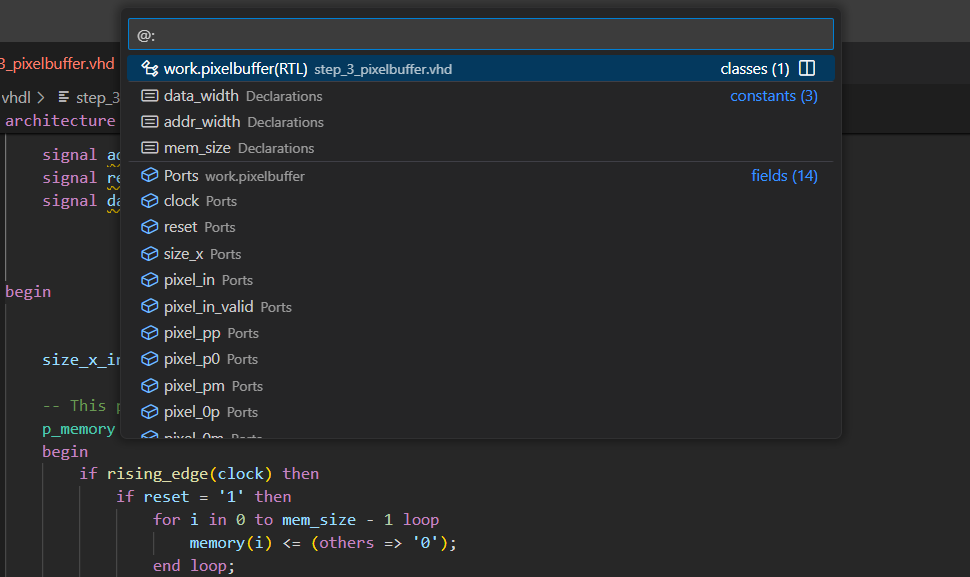

Quick Outline

For a quick outline of the objects in a file in the editor, press Ctrl+P, and type @. You can also type : when opening the Quick Outline to group the items by category.

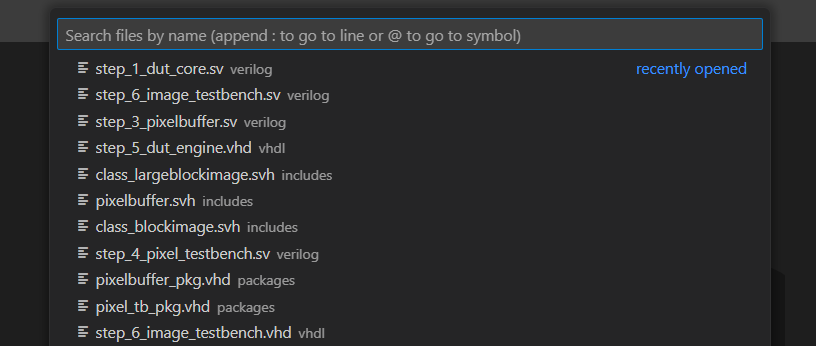

Open Resource (Go To File)

In order to open a resource, press Ctrl+P, filter the list by typing, and select the resource that you want to open from the list.

VHDL Specific

In addition to the powerful features of the VS Code editor, the SVH VHDL editor supports a number of advanced editing features that are specifically useful for VHDL editing. These are described below.

Code Highlighting

Highlighting classes for VHDL:

- Syntax: Comment, Keyword, Number, String, Task Tag

- Semantic: Constant, Port, Signal, Type, Variable, Attribute, Function, Procedure, Labels

VHDL Specific Autocompletes

Declaring a Component

If you want to create an instantiation based on a component (as opposed to a direct entity instantiation), you need to associate an entity with a component. SVH can automatically declare a component for an existing entity. In the place where you would normally enter the component name, use autocomplete instead to show the list of available entities. Upon selection, the tool will automatically complete the component declaration.

Autocomplete suggestions automatically appear and are updated as you type.

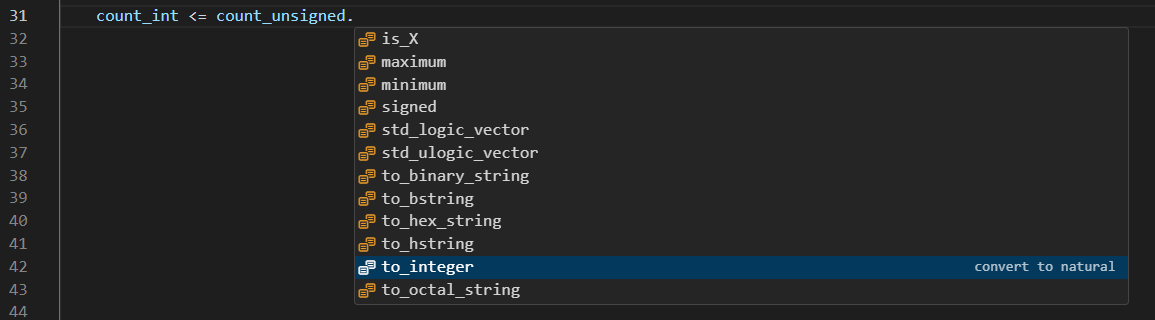

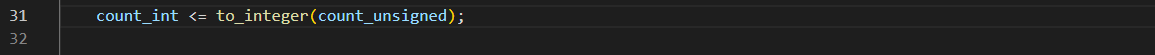

Type Conversion

In VHDL design, you need to do a lot of type conversions, and SVH’s

autocomplete functionality can help you here. Put a period (.)

after the element you want to convert and the autocomplete suggestions

will appear with descriptions like convert type.

Once you select the desired conversion function, SVH will insert the code.

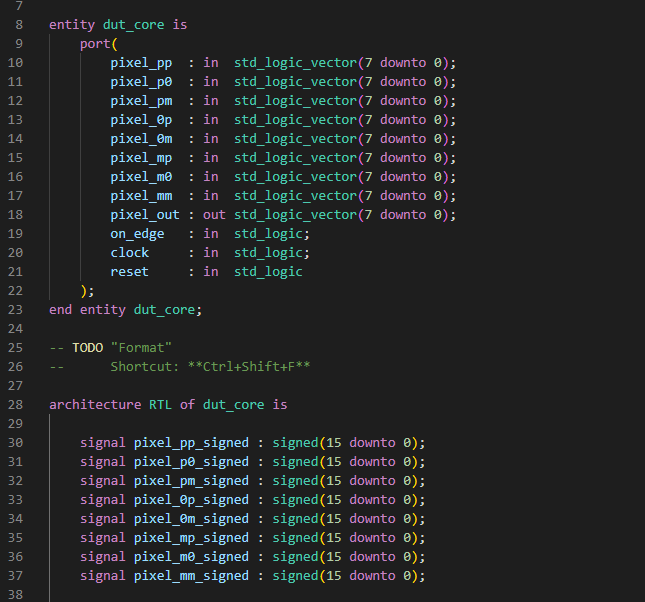

VHDL Code Formatting

Right-click in the editor and select Format Document to format your current VHDL file.

This includes:

- indentation

- spacing between keywords and references

- vertically aligning symbols like

<= - keyword casing

- comment alignment

Context-Based

SVH’s formatter is context-based and tries to respect the author’s style. So depending on your source style, the formatter might make different choices.

One example of this is the decision to format a conditional signal assignment on one or more lines. SVH decides based on the position of the first else keyword.

If you put the else keyword on the first line, the formatter will keep everything on one line. If you put the else keyword on a new line, the formatter will use multiple lines for the assignment.

demo <= (others => '0') when enable = '1'

else (others => '1') when input = '1' -- else on new line

else (others => 'X');

Note about broken code: If your VHDL source file contains syntactical errors, the formatter cannot always figure out appropriate formatting. For this reason, the formatter is programmed to stop applying (whitespace) changes beyond unsupported syntax errors.

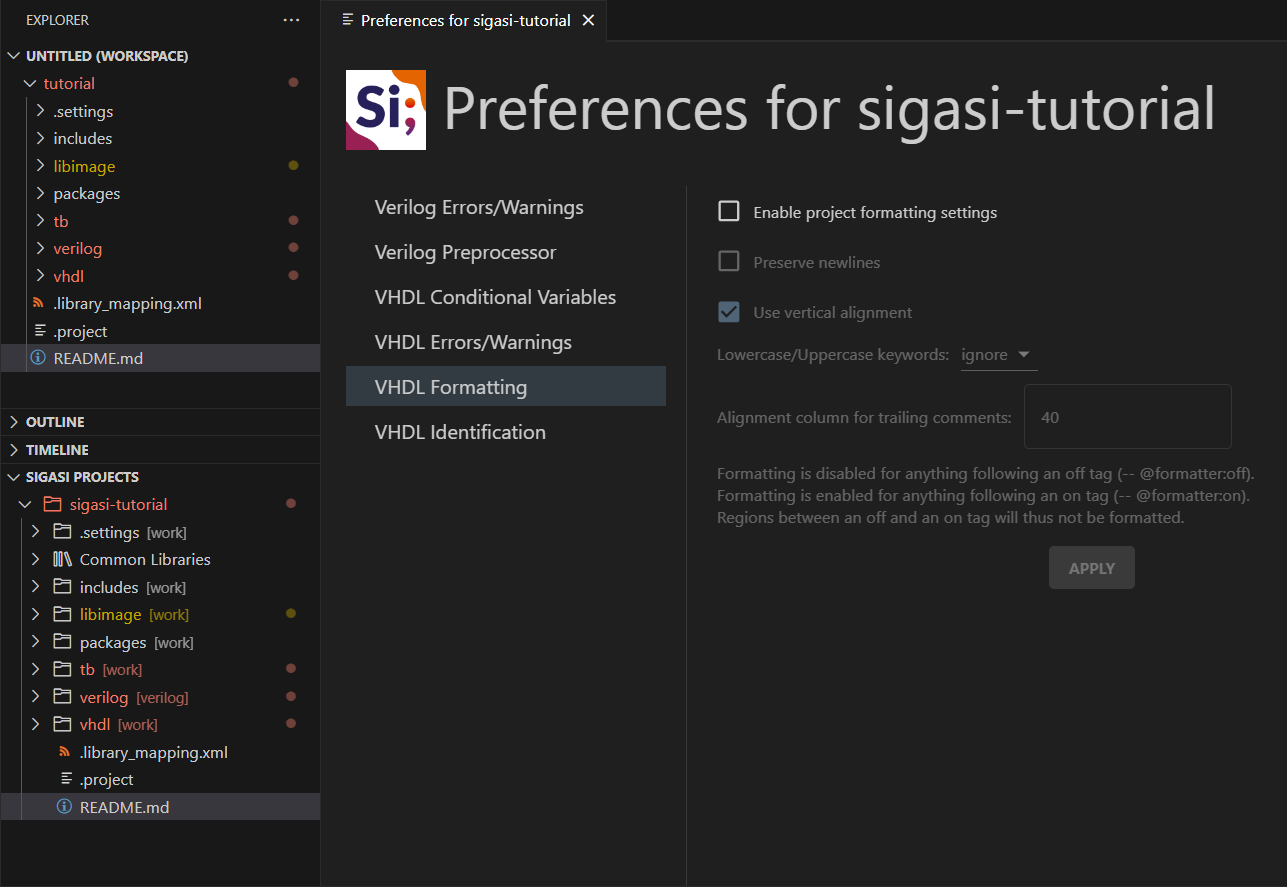

Configuration

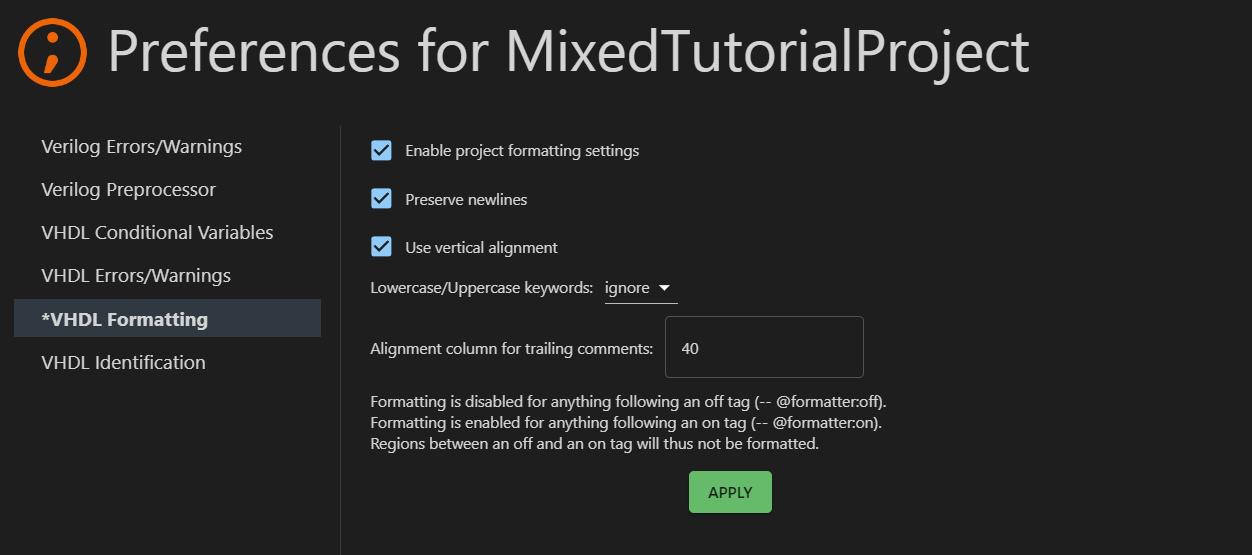

In order to set your formatting preferences, right-click the project name in the Sigasi Projects View and select Open Preference View. Then click VHDL Formatting and enable project formatting settings.

- Preserve newlines: this option configures the formatter to not add or remove any newlines in your code.

- Vertical alignment: this option configures the formatter to vertically align consecutive declarations and statements, for example

<=or:. - Lowercase/Uppercase keywords: when this option is set to

UPPERCASEthe formatter will convert all VHDL keywords to uppercase. When this option is set tolowercase, the keywords will be converted to lowercase. When this option is set toignore, the case of keywords won’t be changed by the formatter.

Note: A Sigasi Visual HDL Designer Edition license is required for this option. - Alignment column for trailing comments: this setting configures what column SVH aligns trailing comments to. The default is 40, but you can choose 0 to not align trailing comments.

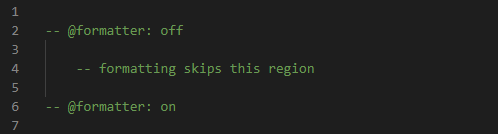

Disable Formatting in Defined Regions

You can disable the formatter for defined regions in your VHDL source files by adding off and on tags:

- off tag:

-- @formatter:off- Turns off the formatter until the end of the file or until an on tag is encountered

- on tag:

-- @formatter:on- Reenables the formatter following an off tag

Format on Save

You can use auto-formatting whenever you save a file. This feature can be enabled with the key editor.formatOnSave.

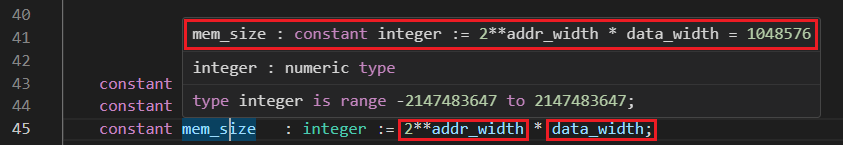

Constant Propagation

SVH propagates the values of VHDL constants to the expressions where they are used.

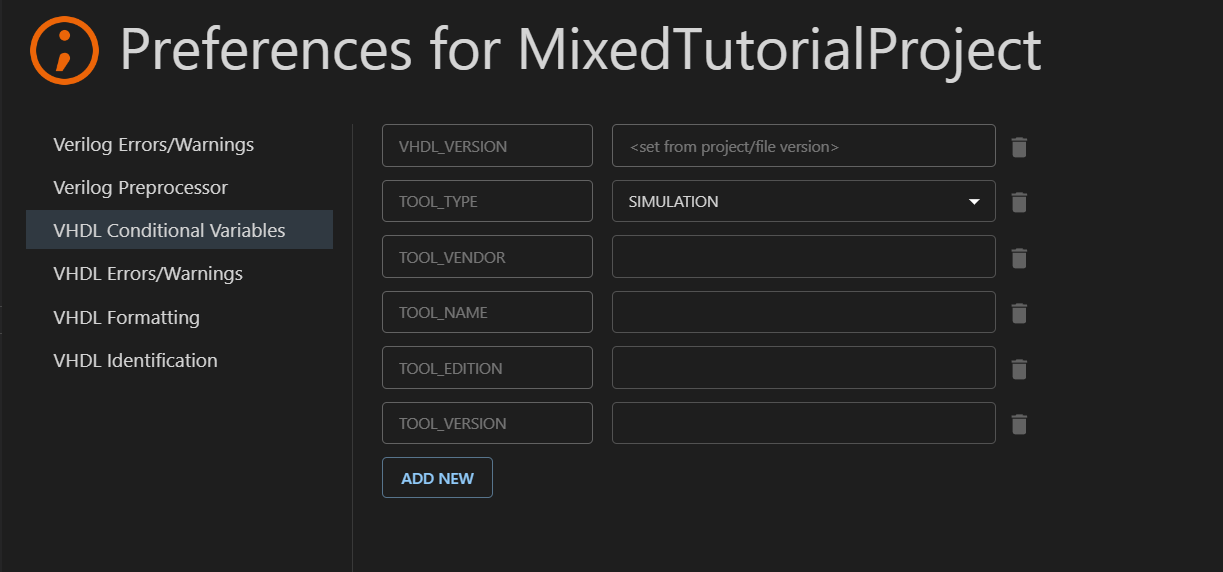

VHDL 2019 Tool Directives

VHDL 2019 tool directives are a simplified version of the preprocessor found in SystemVerilog or the C-family of languages. Tool directives allow for conditionally enabling code based on tool type, debug mode, or any other custom variable.

In order to edit VHDL tool directives, right-click the project name in the Sigasi Projects View and select Open Preference View. Then click VHDL Conditional Variables.

Note that some keys are hardcoded as required by the VHDL Language Reference Manual.

VHDL Version

To configure the VHDL version, right-click the project name in the Sigasi Projects View and select Set Language Version. In the dialog box, select Set VHDL version and then select the desired VHDL version.

The VHDL version can also be set at the folder and file level, but changing the version at the project level will override all folder and file level settings. Also note that the VHDL version of a folder or file must be greater or equal to the VHDL version of the project.

Stuttering

Stuttering is an editing technique popularized by Emacs that lets you

type certain things really fast. You activate it by tapping a certain

key twice which will expand it to something more complex. For example, press

the period key . twice, and the editor will expand it to a right

arrow =>. Stuttering works like double-clicking: if you type keys

slowly, the stuttering mechanism will not be triggered.

The following stuttering keys are available:

| Keys | Effect |

|---|---|

| ,, | <= |

| .. | => |

| ;; | := |

Stuttering is enabled by default but can be toggled using the configuration option Enable stuttering with the key sigasi.vhdl.stuttering.

Verilog and SystemVerilog Specific

In addition to the powerful features of the VS Code editor, the included SVH Verilog and SystemVerilog editor supports a number of advanced editing features that are specifically useful for SystemVerilog editing. These are described below. Currently, SVH supports Verilog 2005 (IEEE 1364-2005) and SystemVerilog 2017 (IEEE 1800-2017).

Code Highlighting

Highlighting classes for Verilog and SystemVerilog:

- Syntax: Comment, Keyword, Number, String, Task Tag, Operator

- Semantic: Assignment, Class, Covergroup, Macro, Enum, Function, Localparam, Module, Net, Wire, Parameter, Port, Type

Verilog and SystemVerilog Specific Autocompletes

Inserting an Include File

Making a typo in the file name of an `include causes swarms of errors. To prevent this, you can simply press Ctrl+Space

between the double quotation marks of an include directive. You’ll be presented with all the files reachable from

your current include path.

Verilog and SystemVerilog Code Formatting

Right-click in the editor and select Format Document to format your current Verilog or SystemVerilog file. The default formatter implementation corrects indentation only.

Verilog Version

You can choose whether *.v files are treated as Verilog (IEEE 1364-2005) or SystemVerilog (IEEE 1800-2017). *.sv files are always treated as SystemVerilog. To configure the Verilog version, right-click the project name in the Sigasi Projects View and select Set Language Version. In the dialog box, select Set Verilog version.

Include Paths and Initial Preprocessor Definitions

Sigasi attempts to resolve missing Include Paths automatically. However, we highly recommend you explicitly configure include paths to ensure the order is accurate. You can configure include paths on the Verilog Preprocessor page. Right-click the project name in the Sigasi Projects View and select Verilog Preprocessor.

Here you can set include paths. In the Initial preprocessor definitions field, you can configure definitions to be set before other files in the project are processed.

This allows you, for example, to set global defines without an explicit include statement.

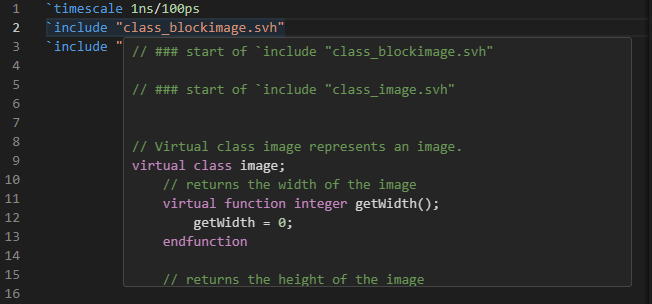

Preprocessor

When you hover over a SystemVerilog preprocessor directive (e.g. include ...), SVH shows the preprocessed text.

In the Preprocessor View, you can preview the expanded version of your preprocessed SystemVerilog source files. In order to open the Preprocessor View, right-click in the editor and select Show In > Preprocessor.

[Back to top]

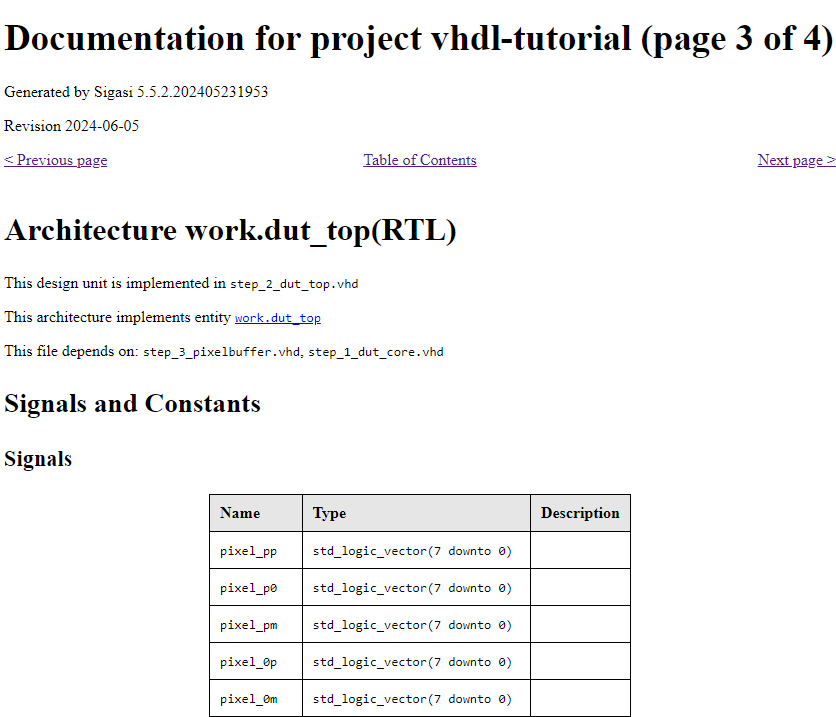

Documentation Generation

The Sigasi Visual HDL (SVH) documentation generator makes the documentation process more manageable by automatically extracting information from your HDL source files. The biggest advantage is that there is only a single source for both your design and your documentation. While this gives no guarantee that the design stays in sync with the documentation, it certainly makes it easier.

The Sigasi documentation generator has the following advantages:

- No special coding requirements: the plain comments in your code are extracted for the documentation; no need for special annotations. Sigasi uses the same comment association as the hover provider. So, to document a

port, you append a comment to a port declaration. To document anarchitecture, you put the comment just on top of the architecture. - All included. All documentation processing is done in SVH. So you do not need to install extra tools.

- Fully hyperlinked. If you export the documentation, you get a fully hyperlinked document.

- Live preview. You can see what the documentation will look like while you type your code and comments.

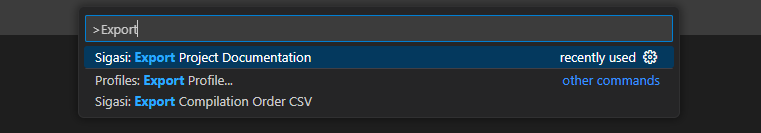

Export Documentation

[Only in Sigasi Visual HDL Enterprise Edition]To export documentation, follow the steps below:

- Open the Command Palette (Ctrl+Shift+P) and type Export

- Select Sigasi: Export Project Documentation

- Follow the wizard steps to customize your documentation

Customization

You can customize the exported documentation.

Note: Diagram rendering is not supported in Remote SSH setups in versions earlier than 5.5.0.

Selecting a Specific Top Level

You can export documentation for an entire project or a specific top level.

- When you select an entire project, the design elements will be listed alphabetically.

- When you select a specific top level, design elements will be ordered in a breadth-first order from the top down.

Resources

You have to choose between Linked resources and Embedded resources when exporting documentation.

Linked resources

Creates an HTML document with linked resources. All Block Diagrams and State Machine Diagrams are in separate files that are linked from within the HTML document. Any custom CSS file present in the project root will be referenced from the HTML document.Embedded resources

Creates an HTML document with embedded resources. All Block Diagrams and State Machine Diagrams are embedded in the HTML document. Any CSS from a custom CSS file present in the project root will be included in the HTML<head>.

Pagination

Enabling the Split pages by elements count or Split pages by design unit count will paginate the output documentation. This is useful for very large designs that produce extensive documentation of hundreds of MBs.

Summary information about the design appears on the first page and fans out to subsequent pages containing the documentation about individual design elements.

Problems Section

Enabling Include problem information or Include problem markers will add a Problems section containing all the project’s Errors, Errors and warnings, or Errors, warnings, and infos. You can also have it show suppressed problems.

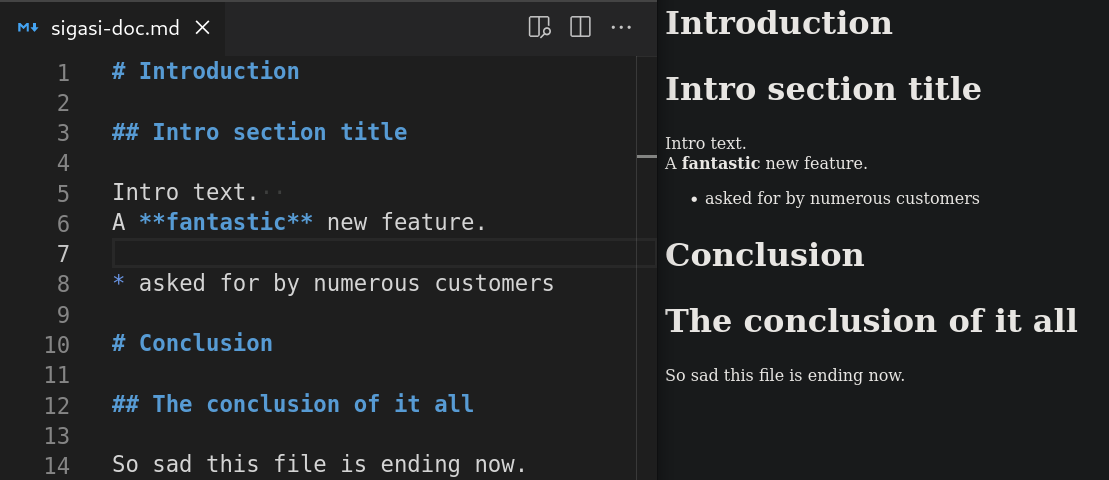

Introduction Section

If a sigasi-doc.md file is present in the root directory of your project, Sigasi will automatically include it in the exported documentation as an introductory chapter.

As usual with our documentation, this is a Markdown file. This allows you to annotate the text easily.

Further Customization

You can further process exported HTML documentation, as explained in Use a Word macro to Scale Diagrams in HTML documentation.

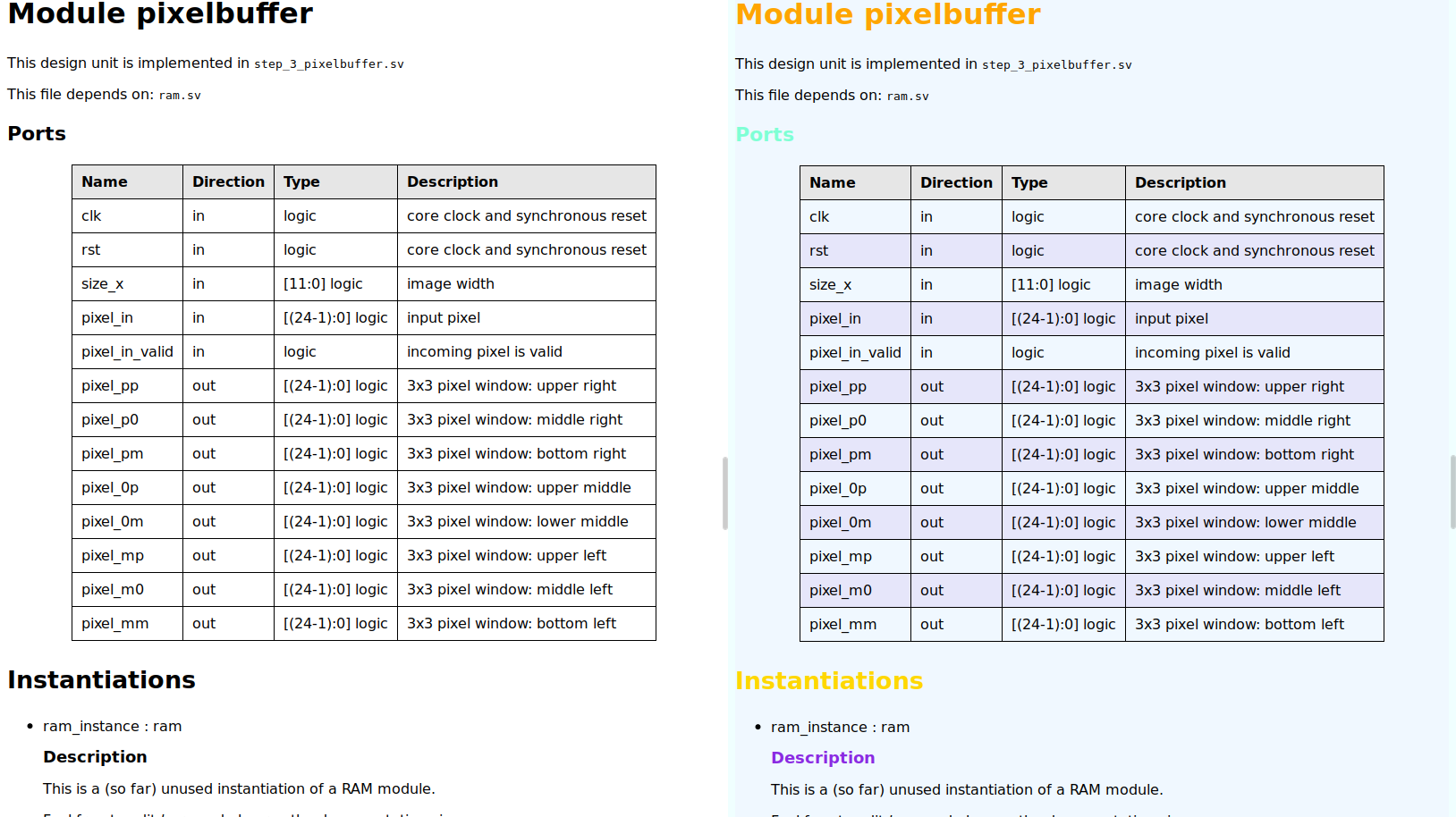

Custom CSS

If the root of your project contains a sigasi-doc.css file, this file will be used to style generated HTML documentation.

Note that only the generated HTML will be affected and not the Documentation View.

For example, you can give the background and titles different colors. You can also change the font for all or parts of the document.

body {

background-color: Azure;

font-family: sans-serif;

}

h1 { color: Tomato; }

h2 { color: Orange; }

h3 { color: Gold; }

h4 { color: Aquamarine; }

h5 { color: BlueViolet; }

Entire sections for entities, architectures, and modules can have different background colors. Likewise, process lists can have different background colors.

.entity, .module { background-color: AliceBlue; }

.architecture { background-color: Cornsilk; }

.processes { background-color: WhiteSmoke; }

You can give tables color banding (alternating row or column colors), including using different colors within sections.

tr:nth-child(even) { background-color: Lavender; }

.entity table tr:nth-child(even) { background-color: FloralWhite; }

It’s also possible to hide parts from view.

#revision { display: none; }

The difference in documentation with the CSS settings described above is shown in the screenshots below.

Comment Association

Comments in HDL code are used to add extra information or documentation to that code. SVH uses certain rules to determine which comment belongs to which code. This is important for documentation hovers, refactoring, formatting, etc. However, which comment belongs to which exact code is subjective.

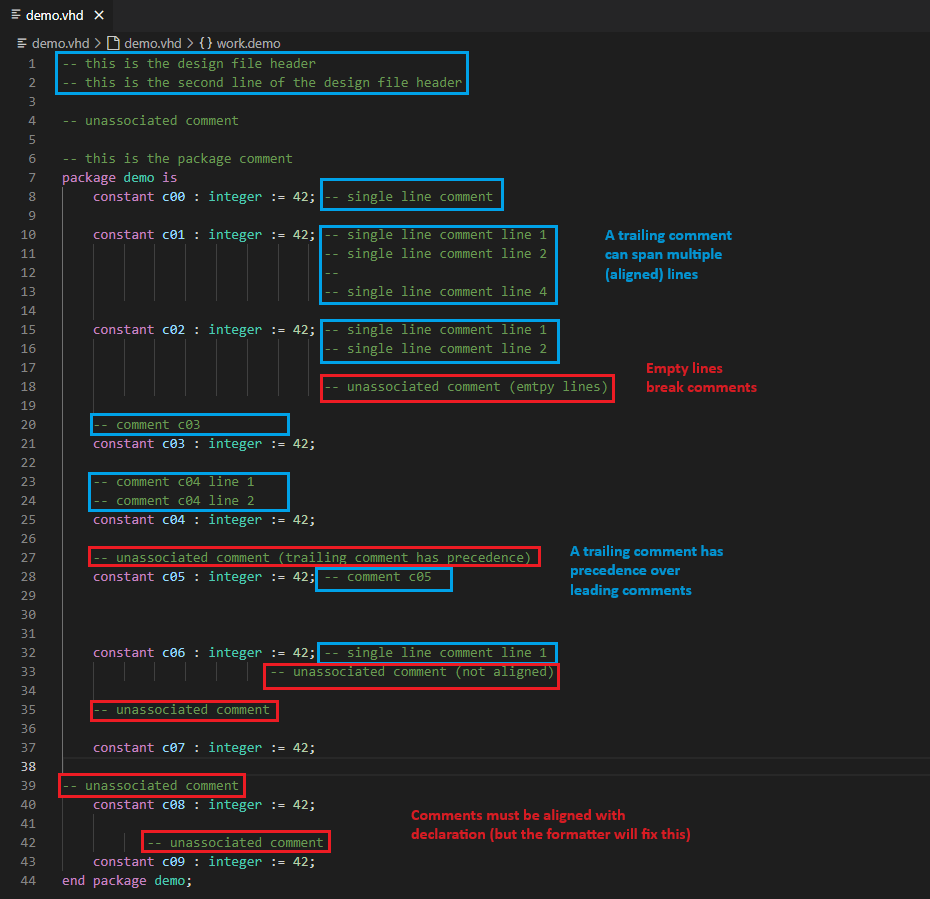

SVH associates comments with HDL declarations with the following rules:

- If there is a declaration before a comment in the same line (trailing comment), the comment is associated with this declaration. This comment can span multiple single-line comments that are aligned.

- If there is no trailing comment and there is a comment on the line above the declaration with the same indentation, the comment is associated with this declaration. This comment can span multiple lines if they all have the same indentation.

- Empty lines break comment blocks

The association rules are illustrated in the image below:

The Formatter and Structural select respect (and fix) comments according to the association rules.

Special Cases

- VHDL components and component instantiations: If a

component(or one of its ports or generics) does not have a comment itself, SVH will use the comment of the correspondingentity. This also works for component instantiations.

Comment Markup With Markdown

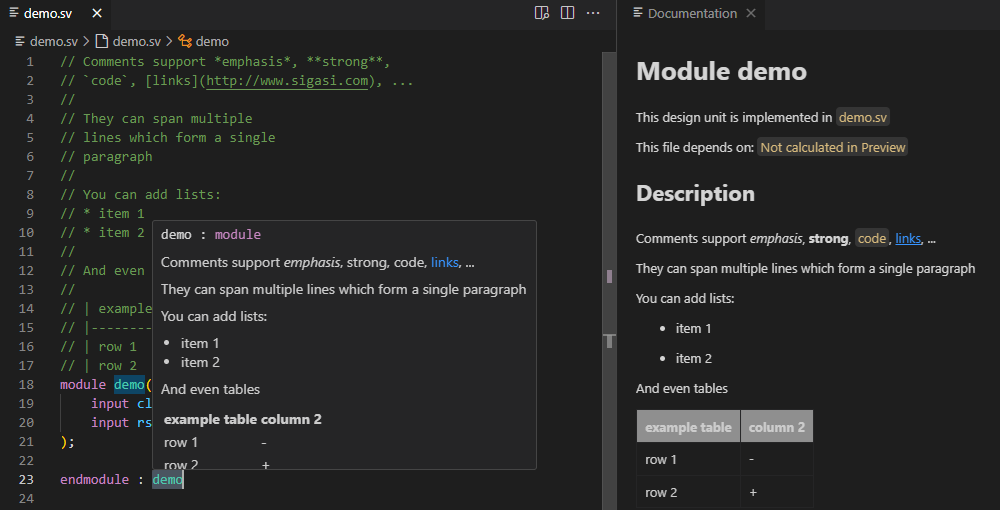

VHDL and SystemVerilog comments are processed with a Markdown processor . This allows you to add markup (e.g., bold, code, paragraphs, hyperlinks, etc.) to comments, resulting in nicer hovers and documentation.

Hovers support complete Markdown syntax. For documentation generation, the following features are supported:

- paragraphs (by adding an empty comment line)

- line breaks (by adding two trailing spaces)

- emphasis (

*emphasis*) - bold (

**bold**) - lists

- tables (with alignment)

- external links and email addresses (

<https://www.sigasi.com>,[Sigasi](https://www.sigasi.com)and<sales@sigasi.com>)

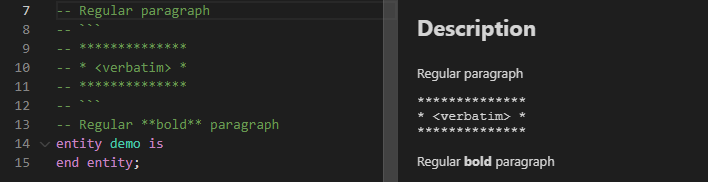

SVH supports Fenced Code blocks in comments.

This enables you to add text to documentation without Markdown rendering.

To add a comment verbatim to documentation, surround it with triple backticks: ```<verbatim comment>```

[Back to top]

Compilation Order Export

You can export a list of all HDL files in your project, sorted in the correct compilation order. You can use your own simple scripts to manipulate a list and run any EDA tool, including simulator, synthesis, and linter tools.

To export a comma separated value (CSV) list of files in your project, follow the steps below:

- Open the Command Palette (Ctrl+Shift+P) and type Export.

- Select Sigasi: Export Compilation Order CSV.

- Select the project and, optionally, a top level design unit.

As a result, a file named compilation_order.csv or toplevel_order.csv (if a top level was selected) is generated in the root of your project. The file lists the HDL files in your project in a valid compile order.

Example (for the VHDL tutorial project):

work, trouble.vhd

work, drive_rst_start.vhd

work, packages/pixel_tb_pkg.vhd

work, libimage/ram.vhd

work, libimage/image.vhd

work, step_3_pixelbuffer.vhd

work, step_5_dut_engine.vhd

work, step_1_dut_core.vhd

work, packages/pixelbuffer_pkg.vhd

work, libimage/image_serializer.vhd

work, step_2_dut_top.vhd

work, libimage/blockimage.vhd

work, step_4_pixel_testbench.vhd

work, step_6_image_testbench.vhd

The file paths are relative to your project root, except on Windows when a file is on a different drive.

[Back to top]

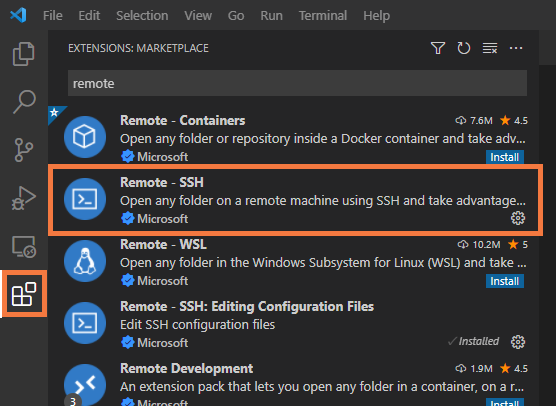

Remote Development

It is possible to run the User Interface of Visual Studio Code on one machine and do the actual development on another machine. For example, you can be working on a Windows laptop at home while the code lives on a Linux server in a datacenter at work.

To work remotely, you only need to install Visual Studio Code and the Remote SSH plugin. The plugin connects with the remote server using SSH and handles any setup required on the server. The Sigasi extension only needs to be installed on the remote server. Your code is kept on the server; there is no need to have a copy on the remote machine. Documentation is available on the Visual Studio website .

Remote Development Setup

- Download, install, and start VS Code on your workstation (the laptop in our example): https://code.visualstudio.com/download

- Navigate to extensions (Ctrl+Shift+X or the icon on the left) and install the Remote - SSH extension.

- From the Command Palette (Ctrl+Shift+P), select Remote-SSH: Connect Current Window to Host…. If you have an SSH config file, you can use an existing configuration here. Otherwise, select Add New SSH host and add the command to connect to your server. Note that you need to enter the full command line and not just the name of the server. Typically, the full command will look like

ssh username@my.compa.ny. To automate this, we recommend to use an SSH key-pair in combination with the SSH config file. - Once the connection is configured, connect to the server. In the bottom left corner of your VS Code window, you’ll find an indication of the remote connection.

- In the connected VS Code window, navigate to extensions and install the SVH extension on the remote server.

- Navigate to the Explorer (e.g. Ctrl+Shift+E) and either open an existing workspace folder or clone a repository.

- Check your Sigasi license setting. From the Command Palette (Ctrl+Shift+P), select Preferences: Open Settings (UI), and look for Sigasi: Path To License. With remote development, this is the license path on the server.

- Note that the Sigasi VS Code extension with default settings will extract a shipped JRE. If you want to use another JRE that is already installed on the server, look for Sigasi > Java: Path in the settings and enter he path to your

java(17 or higher) executable. - Now open a VHDL, Verilog or SystemVerilog file on the remote server.

Remote Development License Needs

- When using the SVH extension in combination with the Remote SSH extension, the Sigasi license should be available on the remote host.

- If you’re also using SVH locally, the license settings might be different for local and remote development. In that case, make sure to use the proper settings, depending on whether you’re developing locally or remote.

- The settings from the

Userlevel will act as the default and can be overridden for each remote by setting theRemote [<remote name>].

[Back to top]

AI Chat

SAL (Sigasi AI Layer, in case you’re wondering) is the name of the integrated AI chatbot in Sigasi Visual HDL.

There are three ways to get a conversation with SAL started.

First, by clicking the SAL icon in the Activity Bar icon.

Second, by choosing “Chat with SAL: Focus on Chat with SAL View” from the Command Palette (opened with

Ctrl-Shift-P by default).

Finally, by selecting a piece of HDL code and using the context menu SAL > Explain This Code.

Note: Through SAL, you can connect to a remote model using the OpenAI API, such as OpenAI’s GPT 4 model, or a local AI model of your choice via LMStudio.

Configuring your AI model

SAL is configured using up to four environment variables. Be sure to set them before starting Sigasi Visual HDL, so they get picked up correctly. The easiest way to get started it by connecting to the OpenAI servers, as detailed below. If you prefer to use a model made by another company, or you’re working on an airgapped machine, you’ll have to set up a local model.

Connecting to remote OpenAI services

If you have a working internet connection and an OpenAI API key,

configuring the backend for SAL is as easy as setting the environment variable SIGASI_AI_API_KEY to your API key.

By default, this will use the GPT 3.5 Turbo model.

export SIGASI_AI_API_KEY="your-openai-api-key"

You can use a different model by setting the SIGASI_AI_MODEL to e.g. gpt-4-turbo.

export SIGASI_AI_MODEL="gpt-4-turbo" # with the GPT 4 model

export SIGASI_AI_API_KEY="your-openai-api-key" # with this API key

Connecting to a local model

This guide will help you use LM Studio to host a local Large Language Model (LLM) to work with SAL. Currently, SAL supports the OpenAI integration API, and any deployed server utilizing this API can interface with SAL. You need to set the correct URL endpoint and model name, and optionally provide the API key if required by the endpoint.

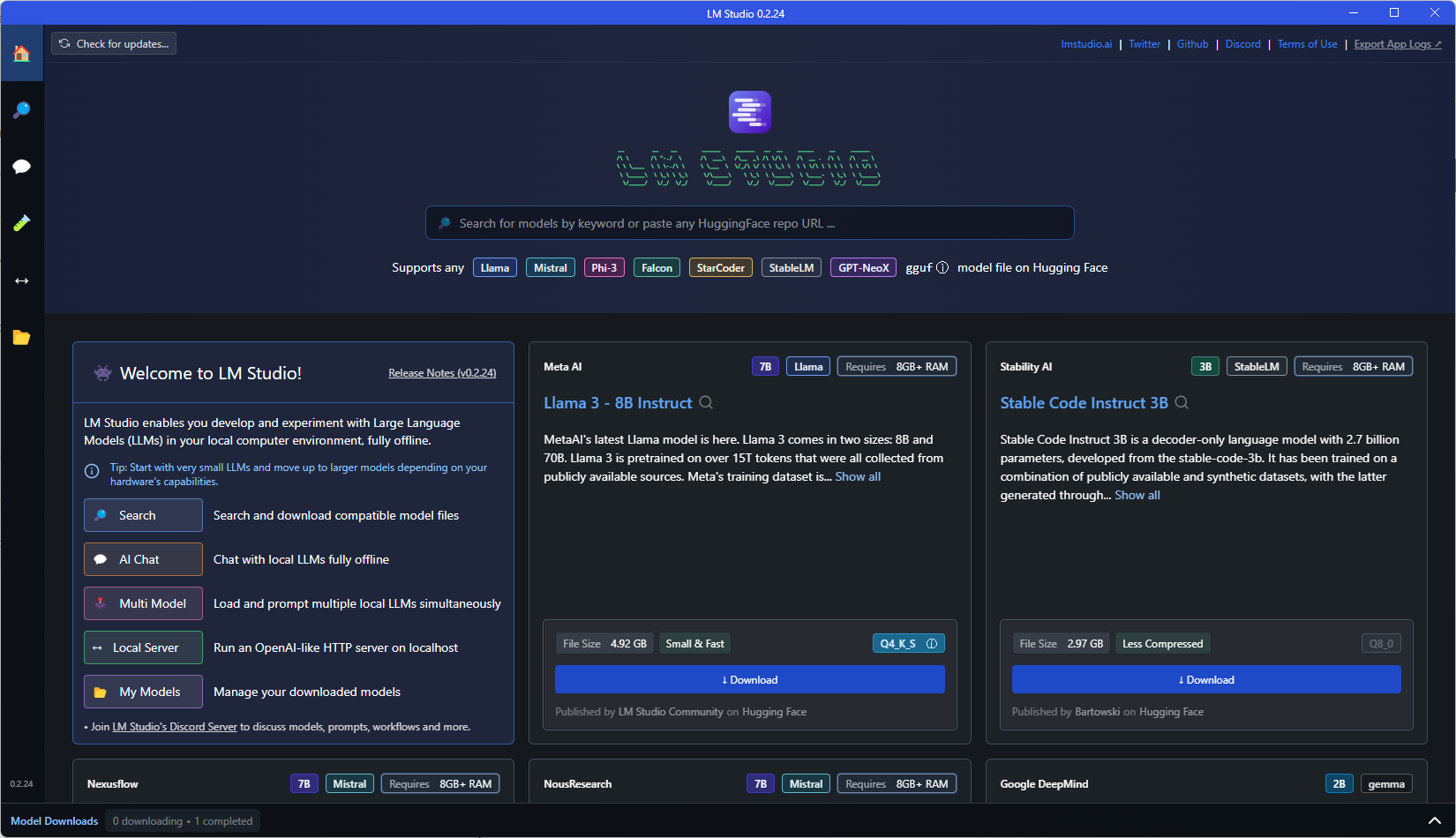

Download the latest version of LM Studio .

Open LM Studio. From the home screen, search and download the model you want to use.

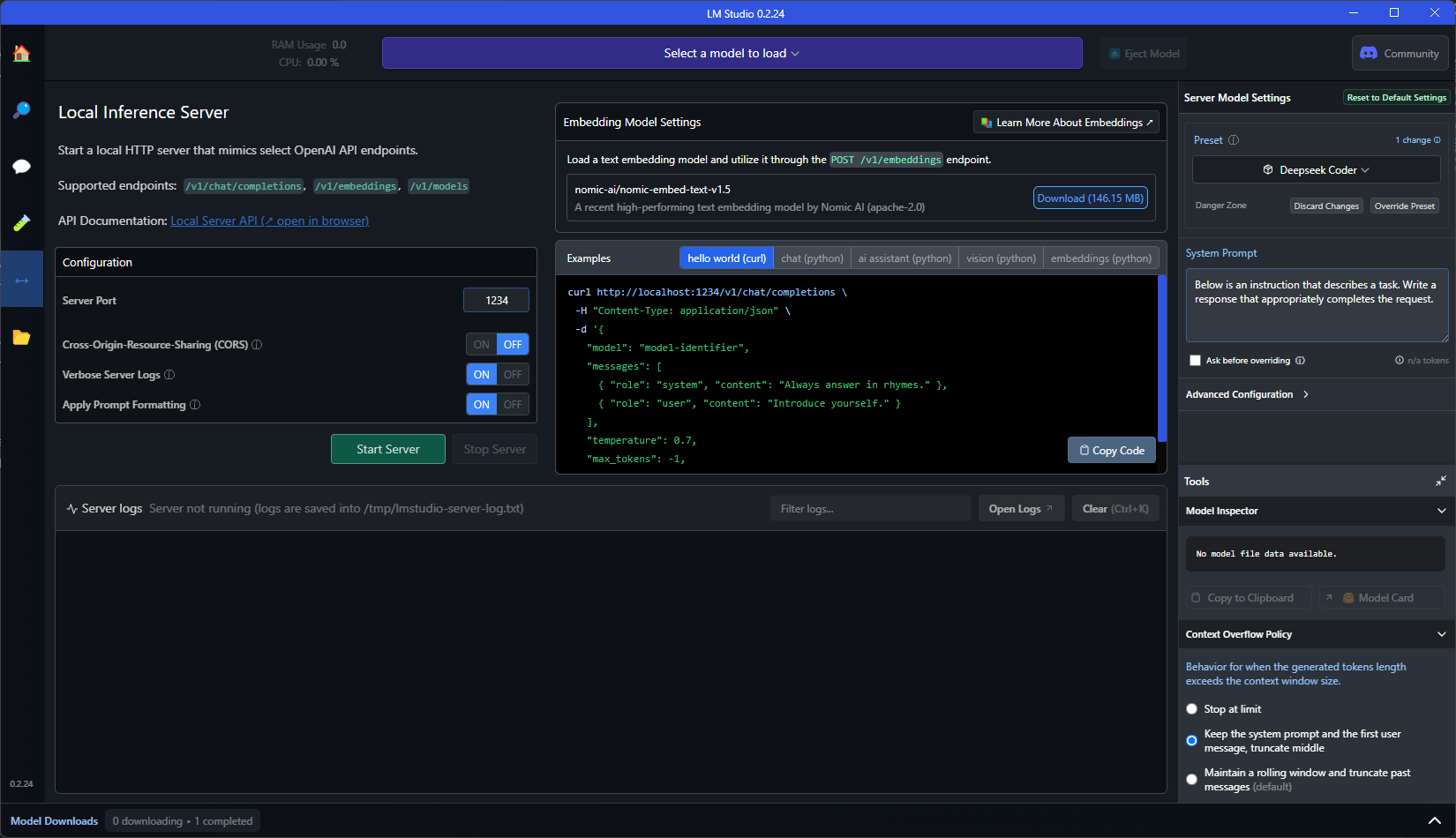

Navigate to the Local Server Window.

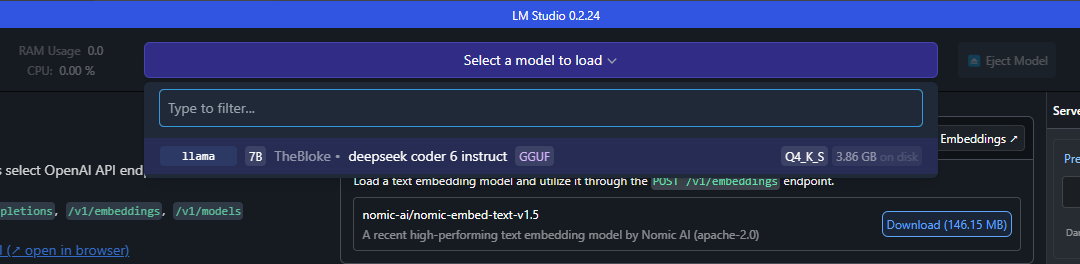

At the top of the local server screen, use the selection menu to choose the model you wish to load.

(Optional) Configure local server parameters, such as the Context overflow policy, the server port and Cross-Origin-Resource-Sharing (CORS).

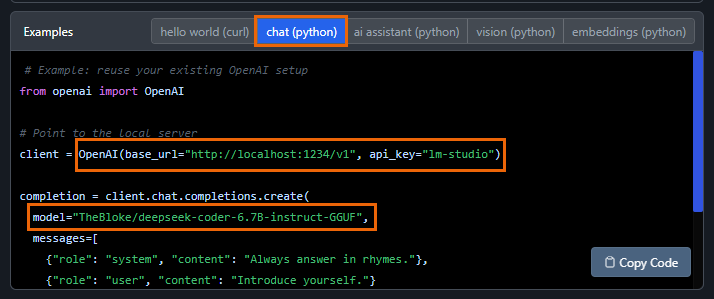

Set the environment variables for Sigasi Visual HDL. You can get the necessary configurations most easily in the Example window under chat (python).

SIGASI_AI_API_URLto the base URLSIGASI_AI_MODELto the model nameSIGASI_AI_API_KEYto the API key (if required)

In this example:

export SIGASI_AI_MODEL="TheBloke/deepseek-coder-6.7B-instruct-GGUF" export SIGASI_AI_API_URL="http://localhost:1234/v1" export SIGASI_AI_API_KEY="lm-studio"Launch Sigasi Visual HDL and start a conversation using your configured local LLM.

[Back to top]

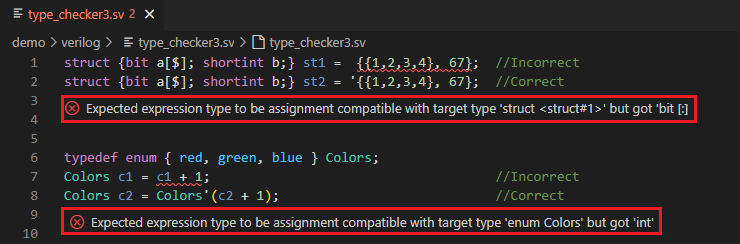

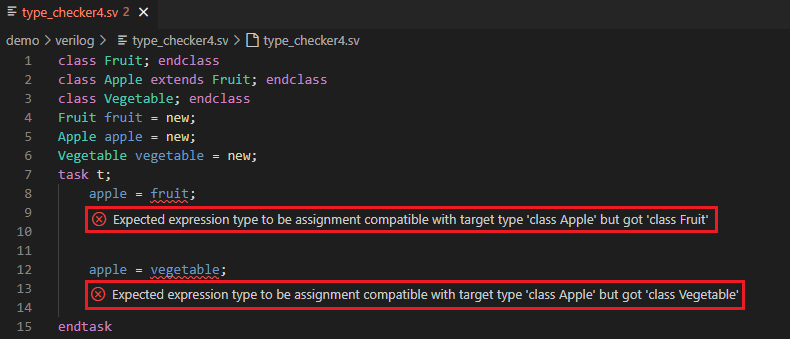

Linting and Quick Fixes

In addition to syntax validation, SVH also checks your code for semantic problems. This is often referred to as Linting or Linter checks. Some of these problems can be automatically resolved with Quick Fixes. Both syntax checking and linting happen at type-time: problems are revealed as you are typing your code.

Linting

A Code Linter is defined as a tool that finds code that is strictly correct according to the language definition, but still suspicious or problematic. Sigasi has a built-in linter, which provides info about code lint in the design.

Configuring the Linting Rules

The Sigasi linter has reasonable defaults for the configuration of reported problems, but the severity level of certain linting rules is configurable for additional flexibility. Furthermore, some linting rules, such as the VHDL maximum line width rule, are parameterized and can be tweaked to your preference.

For each linting rule, you can set the severity of non-conformities in all code or RTL-specific code. For some linting rules, more configuration options are available in the sidebar of the preference page. Look into the documentation of a specific rule for more details on its effect.

Linting rules can be configured per project, folder, or file by right-clicking a project, folder, or file in the Sigasi Projects view, selecting Open Preference View, and clicking VHDL Errors/Warnings or Verilog Errors/Warnings.

Then, enable custom validation settings to activate the rule configuration.

You will then be able to change the linting rule configurations.

All configurable linting rules will also offer configure rule Quick Fixes. These can be used to quickly open the preferences corresponding to a specific linting rule.

Suppressing Problems

You can suppress specific problems in your code by adding a @suppress comment (-- @suppress for VHDL and // @suppress for SystemVerilog) on the same line as the problem.

You can limit the suppression to a specific problem by adding a prefix of the problem message between quotes after @suppress. Sigasi also recommends adding a reason why the problem was suppressed by adding an extra comment after @suppress:

<line with problem> // @suppress "Problem message prefix" Reason why problem is suppressed

Changes through Sigasi version:

- Since Sigasi Studio 4.2 the

@suppresscomment also suppresses errors. - Since Sigasi Studio 4.3 problems have a Quick Fix to automatically add the

@suppresscomment with a matching problem message prefix. - Since Sigasi Studio 5.4 it is possible to suppress all the problems file-, library-, or project-wide through a single Quick Fix.

No Linting for Common Libraries

Common Libraries are considered production-ready libraries. Linting is skipped for all files in the Common Libraries folder.

Language-specific Linting Rules

The currently available linting rules are described in detail on the following pages.

Manual Configuration

Note: we discourage manual configuration, especially for rule parameters other than severity, because it’s easy to get the syntax wrong.

To configure the severity of rules, add a line using this template:

${rule id}/severity/${path}={error|warning|info|ignore}

To configure a parameter of a rule, add a line using this template:

${rule id}/params/${parameter}/${path}=${value}

Where

${rule id}can be the number of the rule (e.g. 140) orallto specify preferences for all rule IDs at once.Rule IDs can be found in the Errors/Warnings settings under the Project Properties and Workspace Preferences. They are also included in the list of VHDL Linting Rules and the list of Verilog/SystemVerilog Linting Rules.

Where

${path}can be<project>(literally, with brackets!) to set the severity of the entire project,/path/to/folderto set the severity of an entire folder, or/path/to/file.vhdto set the severity of a specific file.

The valid values for the parameters are documented on the individual linting rule pages. They are described according to the following rules:

{value1|value2}means that eithervalue1orvalue2must be used, e.g.truefor{true|false}orbit_vectorfor{enumeration|bit_vector|std_logic_vector}.${integer}means the value must be an integral number, e.g.5. If the number must fall within a range, it is specified in a comment.[keyword...]means the value is any number of keywords (or other strings) separated by tab characters, e.g.ENTITY PACKAGE

If any of the strings must contain a tab character or a single quote, escape it using a single quote. For example, below is a list of 2 items, the first

a<Tab>taband the seconda'quote.a' tab a''quote

${regex}means the value must be an RE2/J regular expression, e.g.0|1.

Whitespace in keys must be escaped with a backslash (\``). You can add comments using a #`.

Examples

72/severity/<project>=IGNORE

72/severity//Folder\ name/Extra\ folder=INFO

72/severity//test/top.vhd=WARNING

237/params/fsm_state_type//test/top.vhd=ARRAY_OF_LOGIC

236/params/allowed_literal_pattern/<project>=0|1

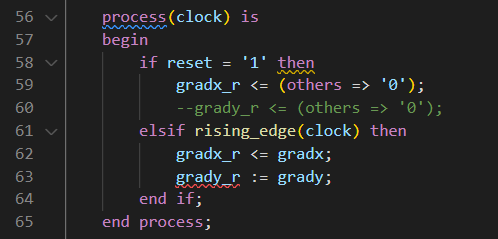

Markers

In the VS Code editor, SVH marks errors, warnings, and info with red, yellow, and blue underlines, respectively. This keeps you visually aware of the problems or info in your code.

Naming Conventions and Header Comment Checks

SVH can check whether all sorts of names in the design; entities,

instances, modules, signals, variables, etc.; follow

particular patterns. This may help designers follow their

company’s or team’s coding rules. For example, coding rules may

prescribe that signal names must have a s_ prefix, that generic

names must be written in capitals, or that variable names must use

CamelCase. A naming convention rule is empty by default, which means

that the particular rule is not checked.

In addition, Sigasi can also check for header comments of files, design units, subprograms, etc. This could, for instance, be used to check whether a copyright notice or disclaimer has been included in a file header comment.

Naming conventions configuration can be found in the Style Validation rule category.

At the top-right, you can set the severity of naming convention non-conformities. Below the severity settings, you can enter validation patterns. Patterns use the RE2/J regular expressions syntax. Note that names are not validated if the corresponding validation pattern is empty.

You can add two patterns per name: a valid pattern that the name must match (a marker will appear if it does not match) and an invalid pattern that the name must not match (a marker will appear if it does). You can set either or both patterns per name.

Similarly, you can also find header comment configuration in the Style Validation rule category.

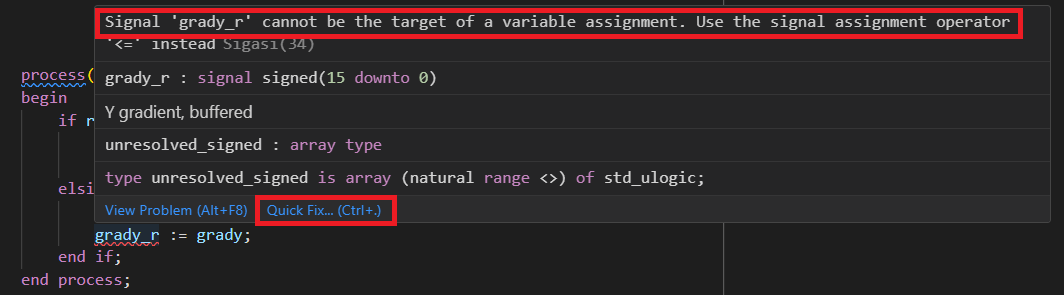

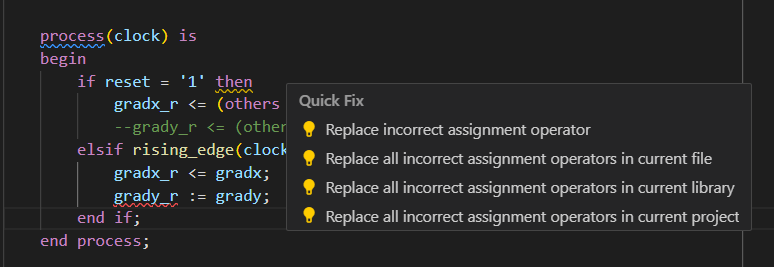

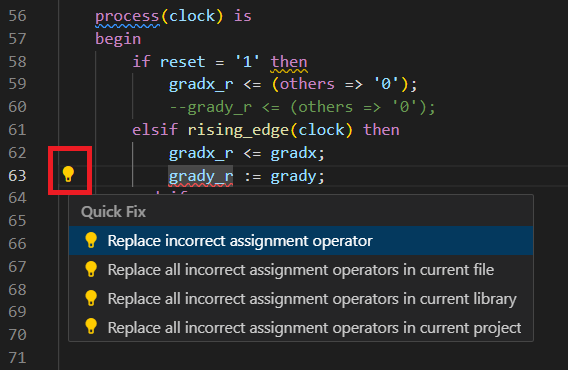

Quick Fixes

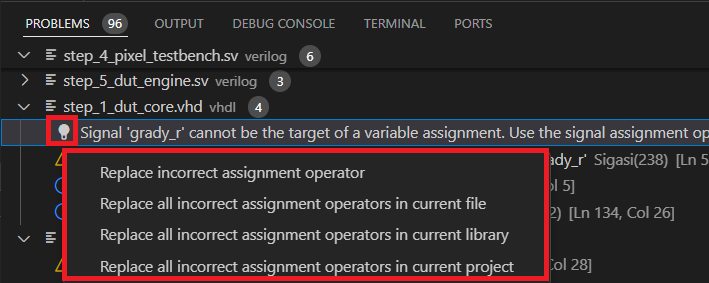

Problems that have markers can be resolved automatically through a Quick Fix. To see whether a Quick Fix is available, hover over a problem underline.

Then click Quick Fix… and select one of the Quick Fixes from the list.

You can also click on the problem marker to make a lightbulb icon appear at the beginning of that line. Clicking the lightbulb will make the Quick Fix list appear. You can then select one of the Quick Fixes from the list.

Finally, you can also trigger Quick Fixes from the Problems View by hovering over a problem and clicking the lightbulb icon that appears.

[Back to top]

Project Formatting Configuration

Project Formatting Configuration

You can configure VHDL formatting preferences for a project in Sigasi Visual HDL (SVH) to ensure consistent formatting across platforms and among users working on the same project.

Properties

Enable project formatting settings, dictates whether or not the formatting preferences specific to this project are enabledPreserve newlines, the formatter respects newlines: it does not add or remove anyUse vertical alignment, align lists such as generics or portsLowercase/Uppercase keywords, controls how the formatter transforms keywords: lowercase, UPPERCASE, or ignoreAlignment column for trailing comments, the column in the line to which the trailing comments will be aligned

[Back to top]

Setting Up a UVM Project

Sigasi Visual HDL (SVH) provides several features that help write UVM testbenches. However, you first have to set up a project with a UVM library to use these features.

This page describes how to set up a UVM project in SVH. The instructions described here are general; refer to the Project Setup section for details on project setup.

Open the folder of your UVM project and add Sigasi support to the project. The project will have a lot of errors at this point, indicating missing declarations and undefined macros.

Add the UVM sources to the project by adding a linked folder to the source folder of the reference implementation of UVM. At this point, most of the errors should be gone. If you don’t have UVM source files on your system yet, you can download them here .

Note: we highly recommend adding this linked folder to the Common Libraries folder, since sources in this folder are treated as read-only and are not checked for errors. We also recommend that every file exceptuvm.svbe excluded from being built.Finally, update the include paths, which you can easily do through a Quick Fix. There should be a number of