Sigasi 5.5 brings brand-new UVM Topology Features to Eclipse and VS Code. We are adding Quick Fixes, Class Hierarchy, Net Search, and the Documentation View to our VS Code extension. Finally, our entire product portfolio now contains CSV Compilation Order Export and Per-project Formatting Settings that can be shared across a team.

Unless explicitly marked, all the improvements below apply to Veresta , our VS Code extension , and our Eclipse offering.

TL;DR

The star of the show for the 5.5 release is UVM. We are introducing a UVM Diagram and a UVM Topology View. Together, they visualize the UVM component hierarchy, its port connections, and its virtual interfaces, allowing you to explore your UVM testbench interactively.

Furthermore, we made CSV Compilation Order Export available in Veresta and VS Code, allowing you to drive your scripts and build systems for all environments.

To improve style guide adherence and team cooperation, the formatting settings for VHDL are now available per project. You can check these files into your version control system with all the other Sigasi settings.

On the VS Code side, we have added the most requested feature: You can now automatically fix many of the problems in your design through Quick Fixes. They can even be applied to all similar problems in a file, library, or project with a single click.

Complementing the UVM views, interactively explore Verilog classes, their properties, and methods using the Class Hierarchy View. Finding all related super- or subclasses is now a breeze. Additionally, VHDL designers unlock the ability to trace nets through their designs and testbenches via the Net Search. Another new Sigasi feature in VS Code is the Documentation View, which shows a live preview of the current editor’s documentation.

Last but not least, this release sees a wide range of over 50 bug fixes and improvements.

UVM Diagram

Reveal, visualize, and explore the UVM testbench you have in mind. Intuitively discover the connections between ports, the relationships between components, and the topological arrangement using the new UVM Diagram. Navigate effortlessly between diagram and code, digging deeper into the hierarchy as needed, swiftly jumping to declarations, instantiations, and types.

Learn more for

Eclipse

Learn more for

VS Code

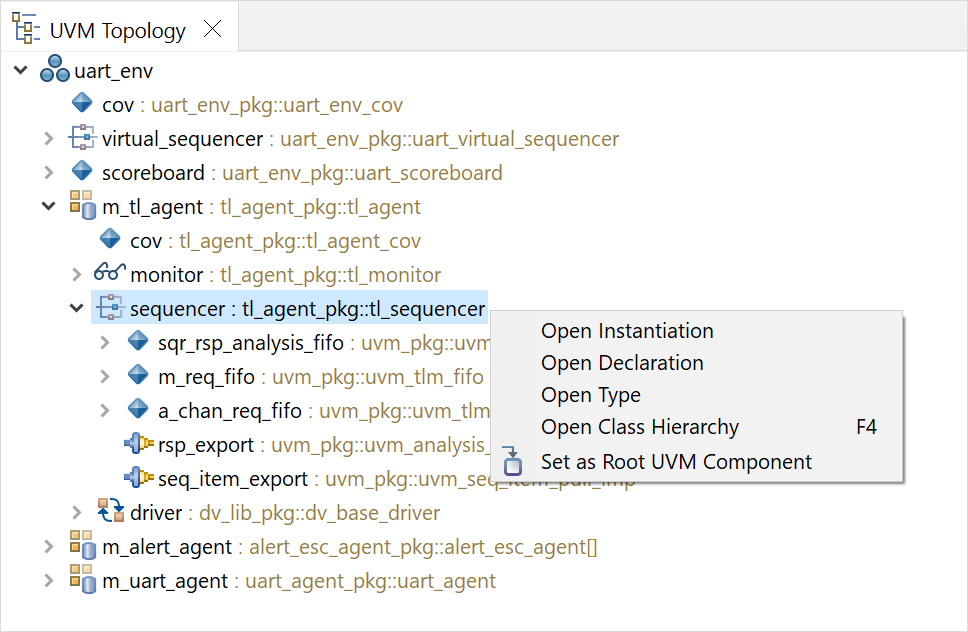

UVM Topology View

The UVM Topology View presents the UVM component’s topology as a tree. Like the UVM diagram, it offers a seamless and efficient way to explore the structure of a UVM project without having to run a simulator. This view lets you quickly locate and navigate to the components, their declarations, and their instantiations. Virtual interfaces and ports are also part of the topology view.

Learn more for

Eclipse

Learn more for

VS Code

CSV Compilation Order Export

Sigasi Studio can generate the compilation order of a project or a chosen top level to a CSV file. This feature already drives many of our Eclipse users’ build scripts and is now also available for Veresta and VS Code.

Learn more

In

Veresta, you can unlock this functionality via the compilation-order command. For example:

veresta compiliation-order --top-level="work.DUT.behavior"

Note that you require a com.sigasi.veresta.comporder license feature to use this feature. Please contact support@sigasi.com for more information.

In VS Code, the CSV export is available via Ctrl+Shift+P > Sigasi: Export Compilation Order CSV.

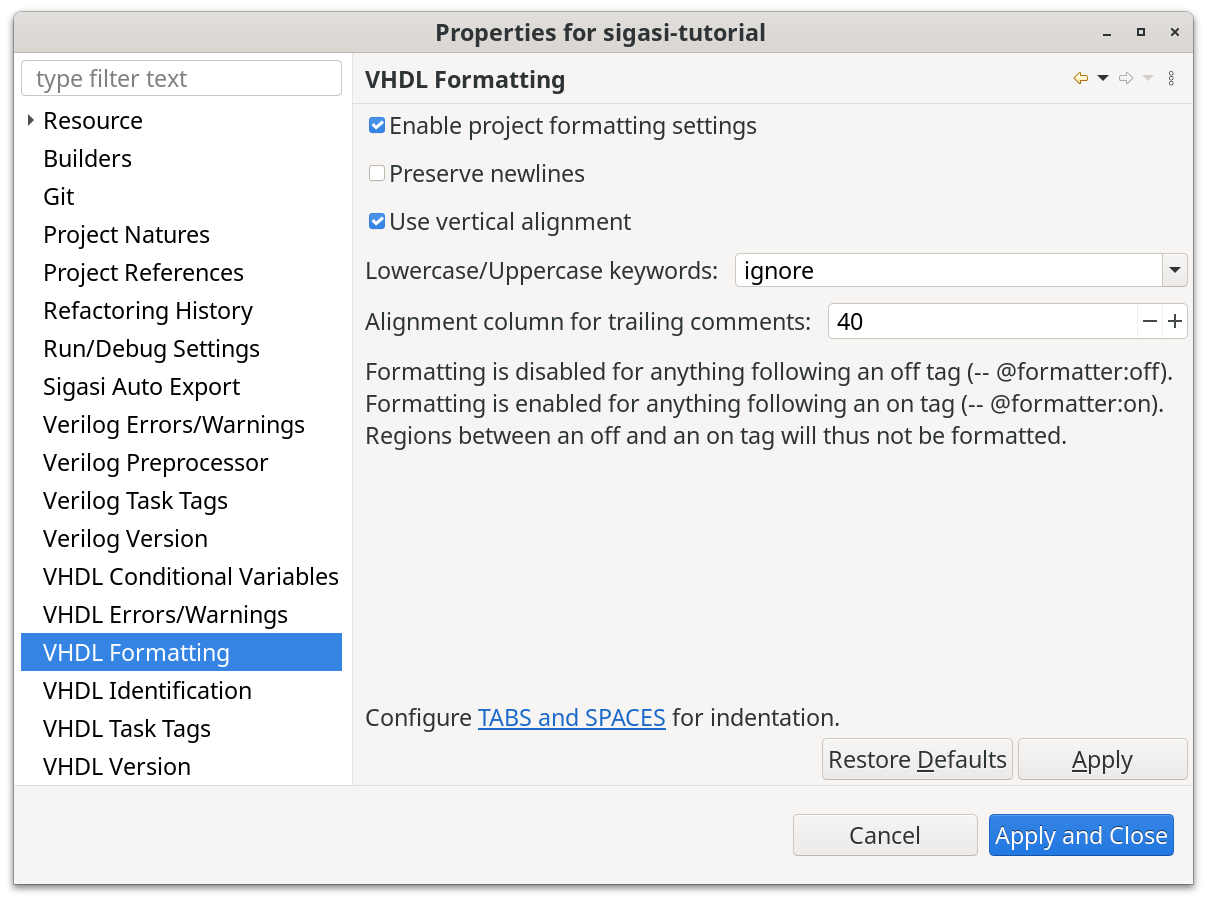

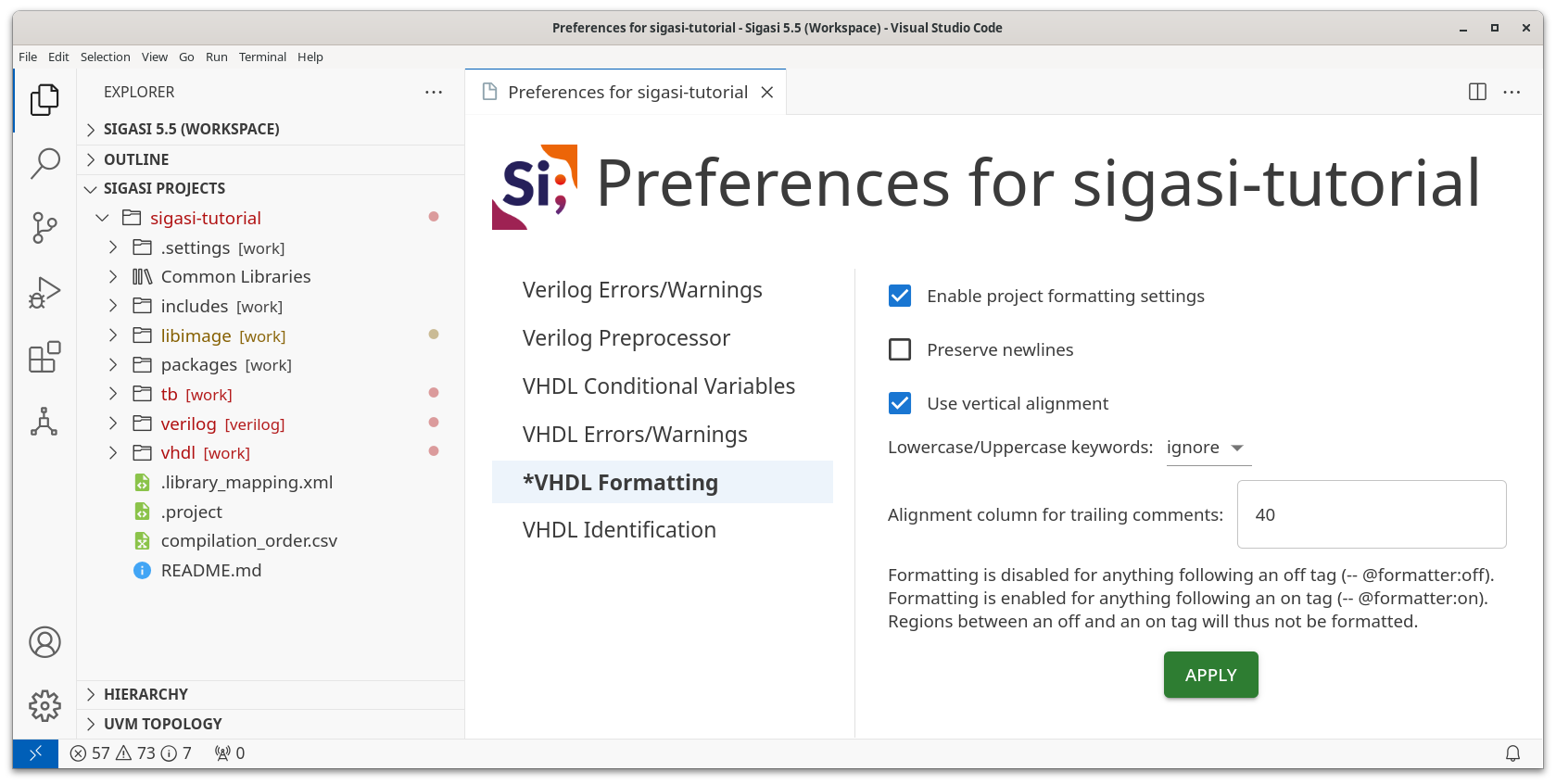

Per-project Formatting Settings

Projects often have specific style guides and formatting standards. All

VHDL formatting settings can now be configured per project. Sharing these with your team and colleagues is as easy as adding the setting files to version control. Merge conflicts due to different formatting are now a thing of the past.

Learn more for

Eclipse

Learn more for

VS Code

You can find the project formatting settings by right-clicking a project in the Project Explorer > Properties > VHDL Formatting. Ensure that the

Enable project formatting settingscheckbox is enabled and that you clickApply.You can find the project formatting settings by right-clicking a project in Sigasi Projects > Open Preference View > VHDL Formatting. Ensure that the

Enable project formatting settingscheckbox is enabled and that you clickAPPLY.

VS Code

Our VS Code extension is quickly nearing feature parity with our Eclipse offering. This release adds Quick Fixes, Class Hierarchy, Net Search, and Documentation View.

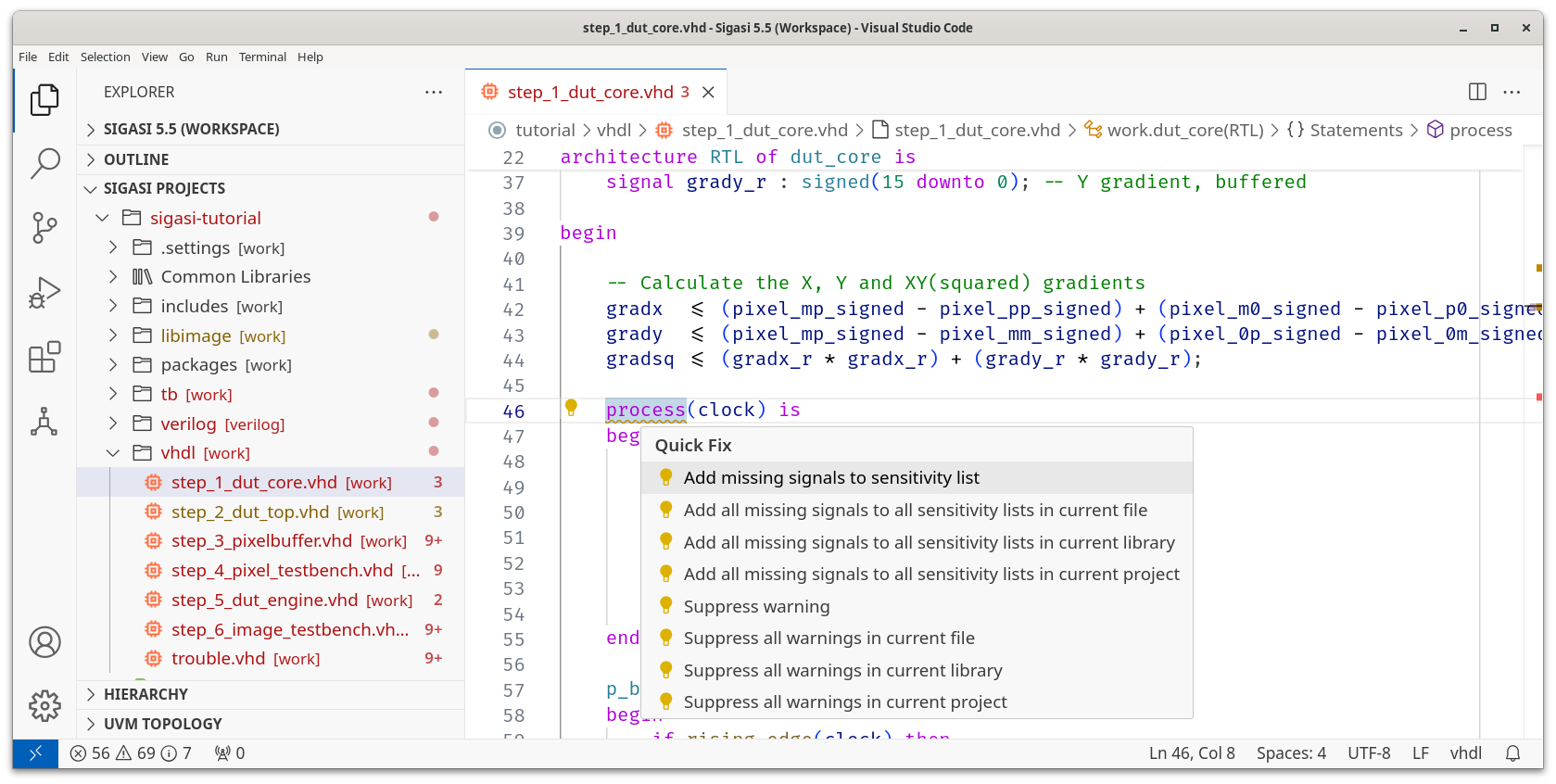

Quick Fixes

Have you ever wished Sigasi would offer to fix the errors and warnings it shows you?

Wish no more. Most of our VHDL and Verilog quick fixes are now available in VS Code and even include a Bulk Mode, allowing you to apply them to all similar problems in a file, library, or project.

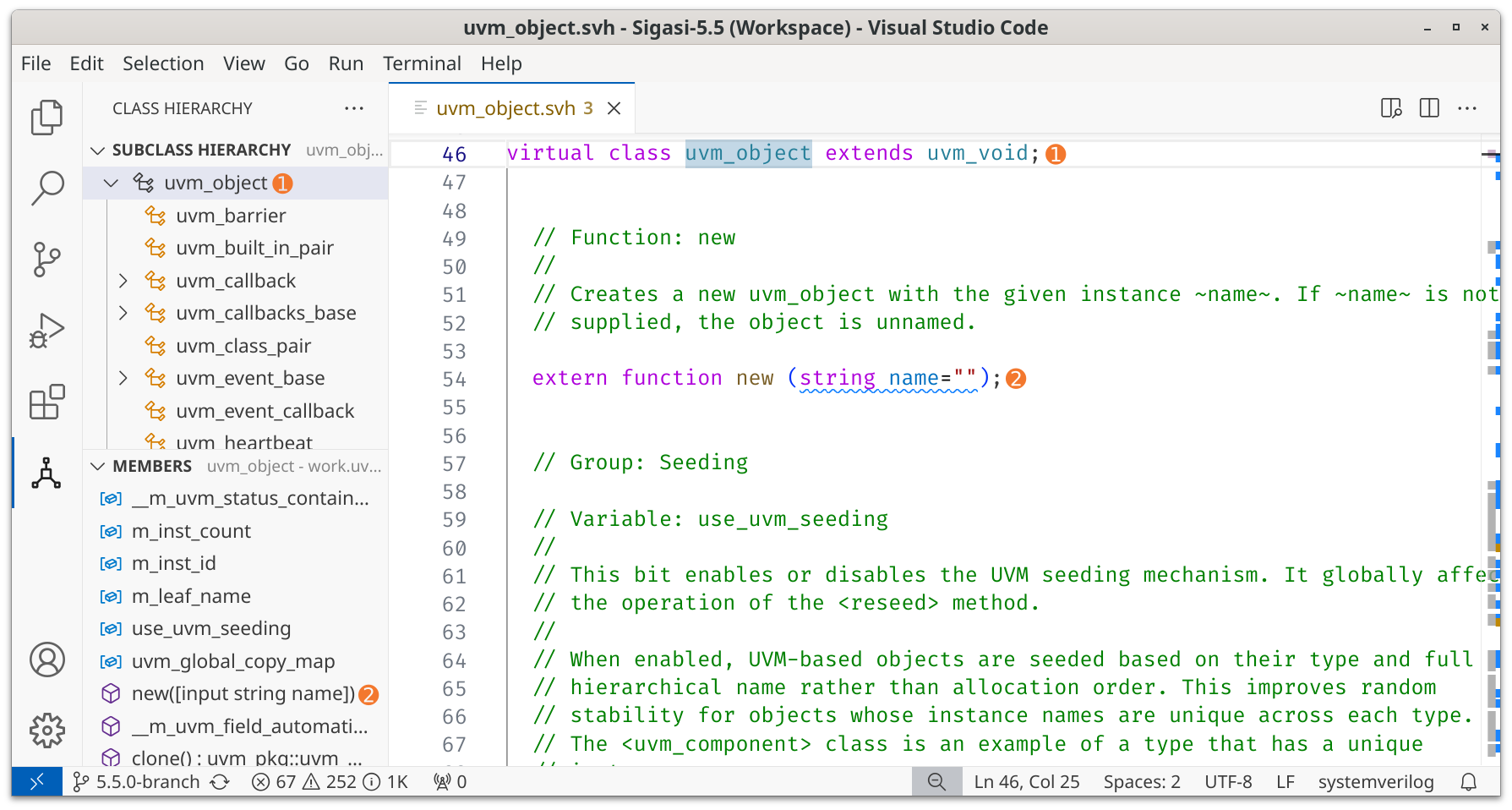

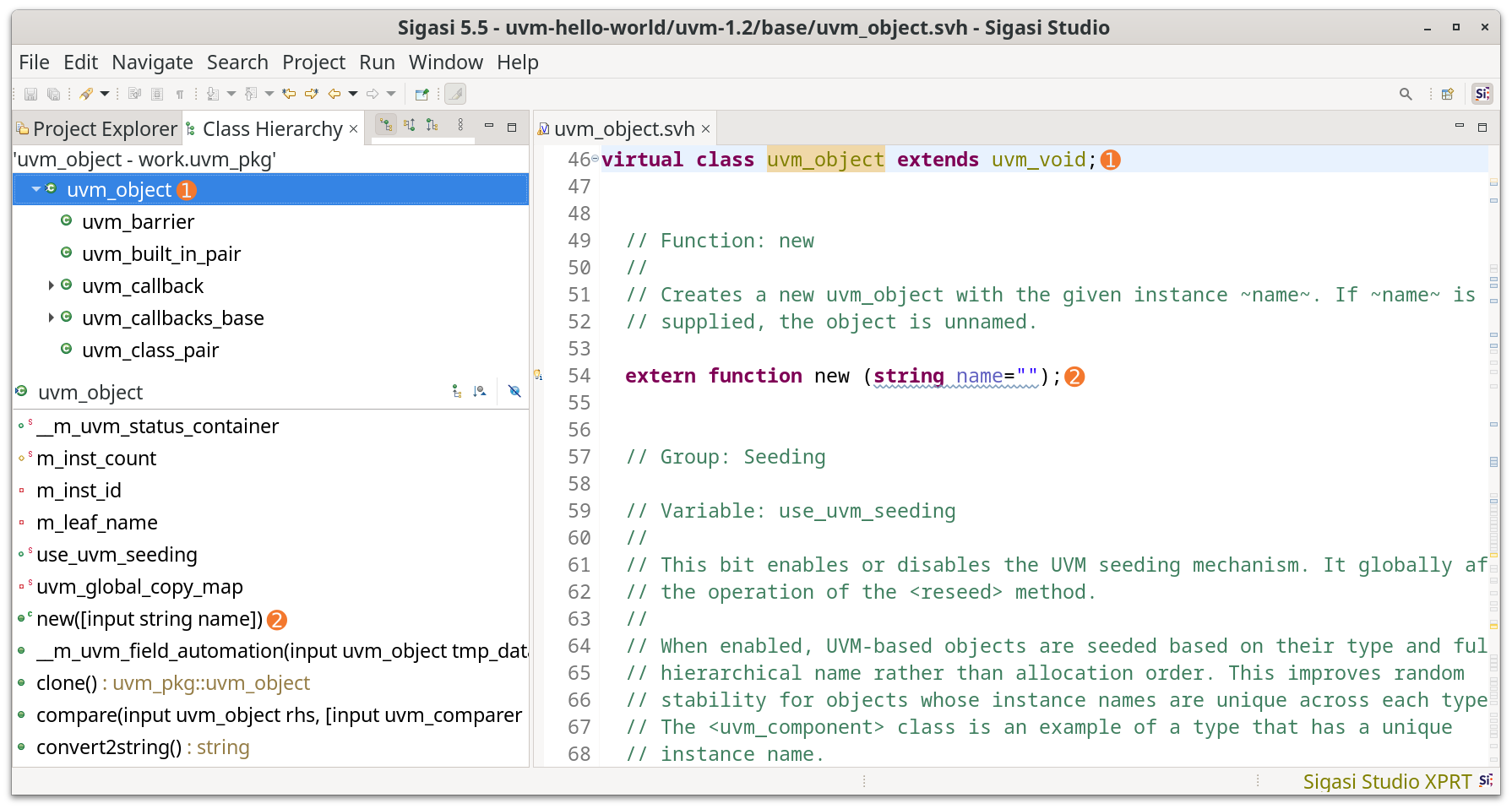

Class Hierarchy

Complementing the UVM views introduced earlier, the Class Hierarchy View, well-loved in Eclipse, enters VS Code. It displays all the super- and subclasses of a class selected with F4. The attached Members View shows all declared properties and methods.

Learn more

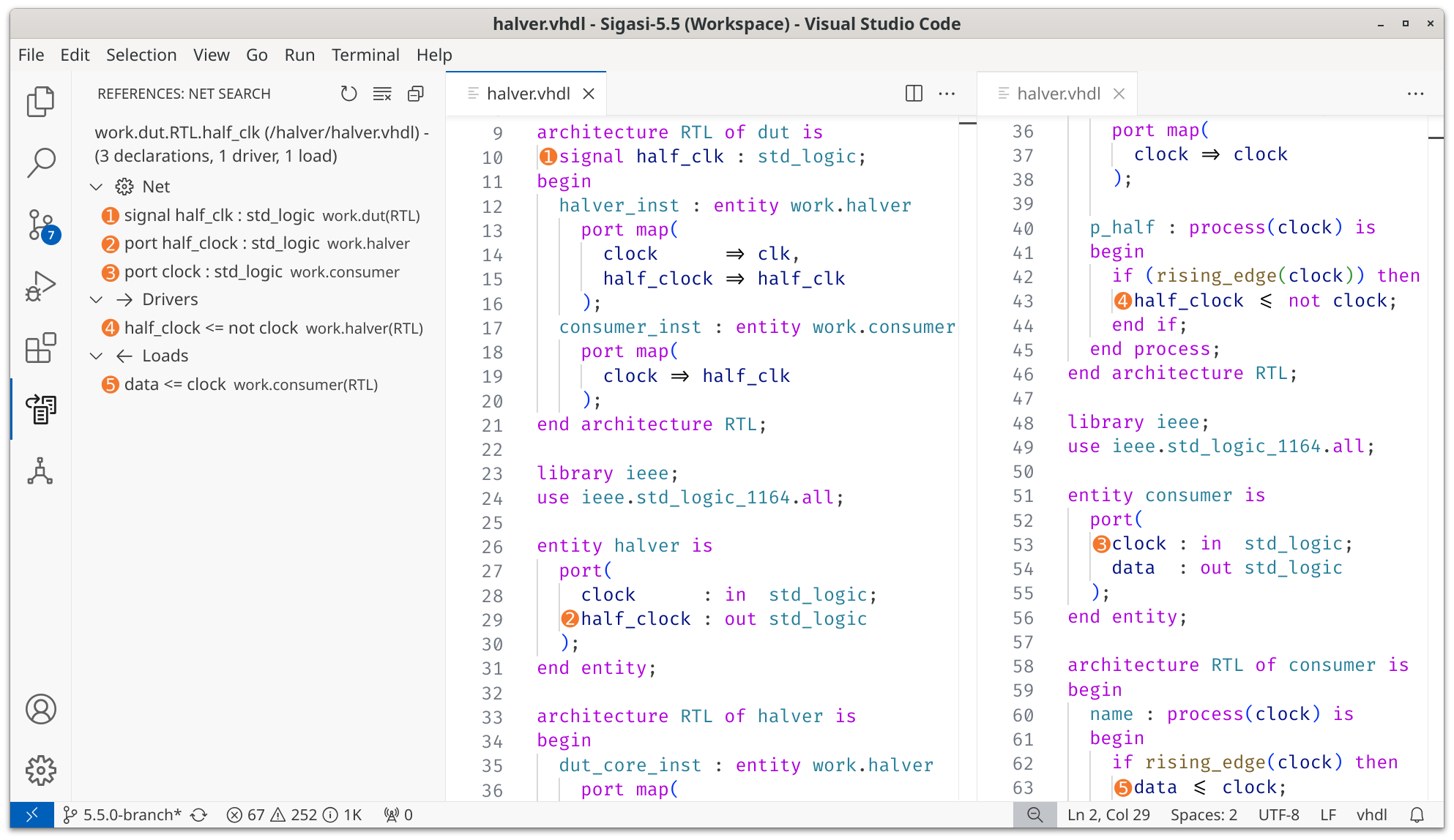

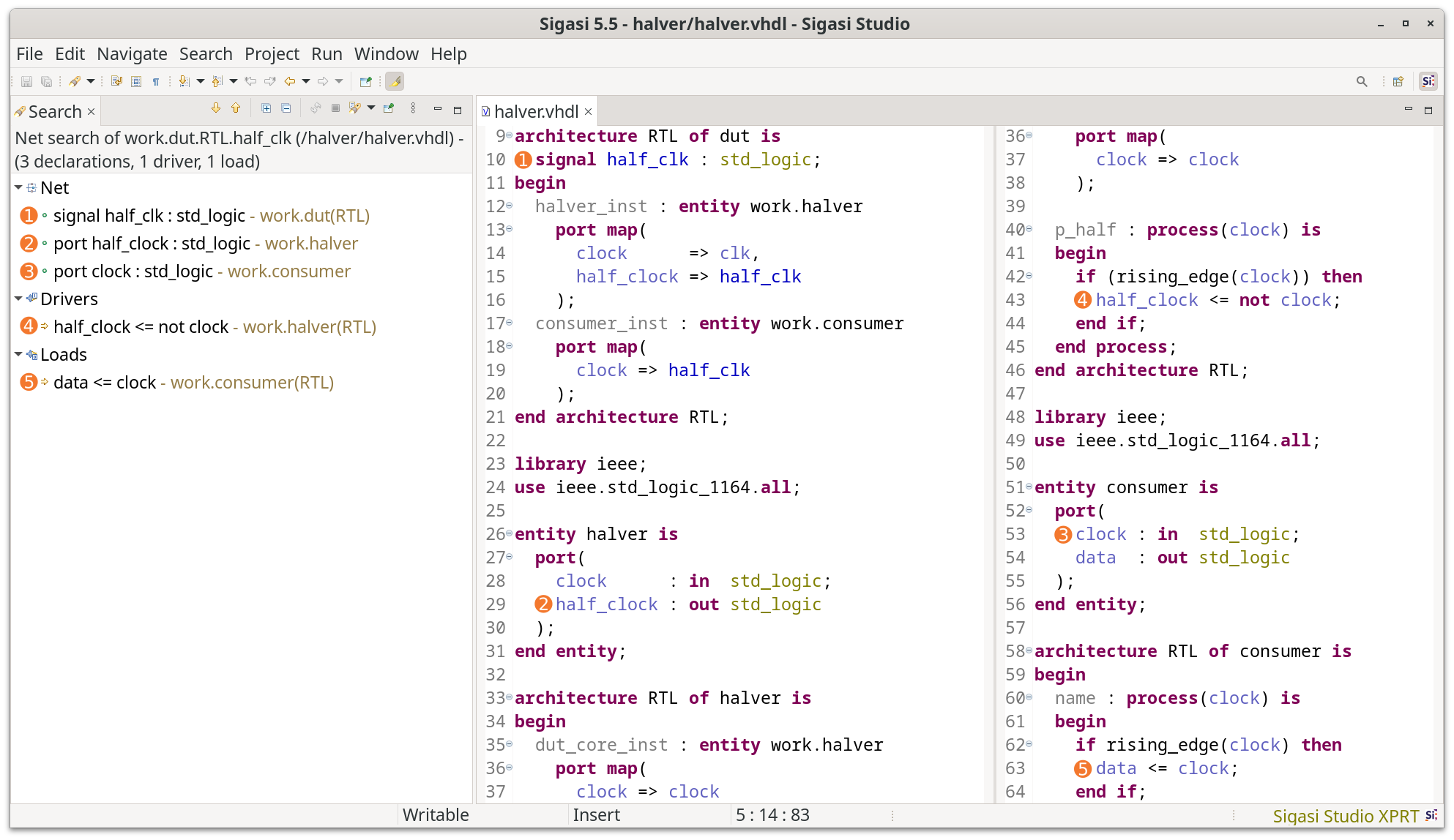

Net Search

Net Search for

VHDL is an advanced search feature to trace your nets through a design. It finds all the locations defining a signal or port for your net and the locations where the net is loaded or driven.

Learn more

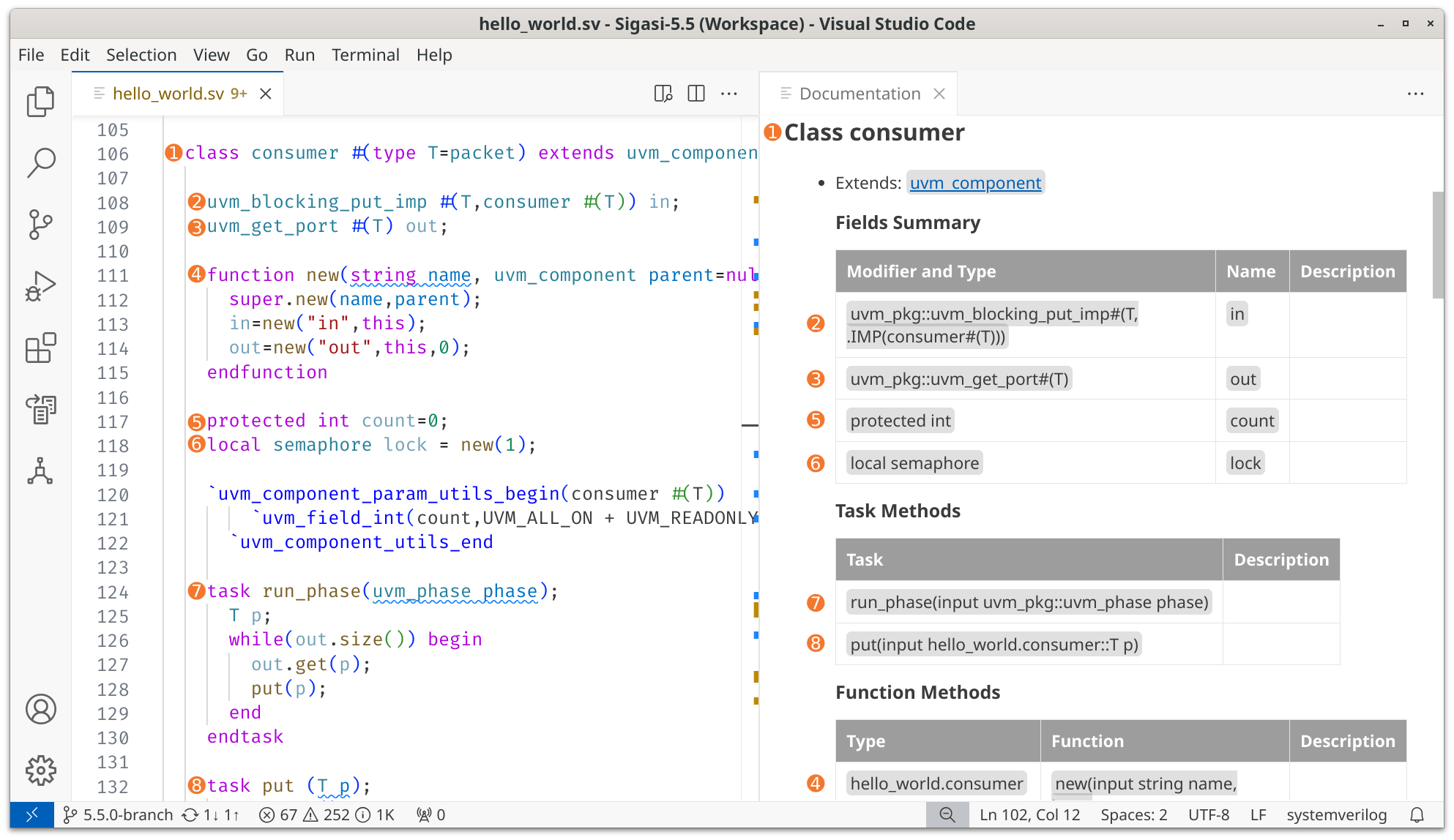

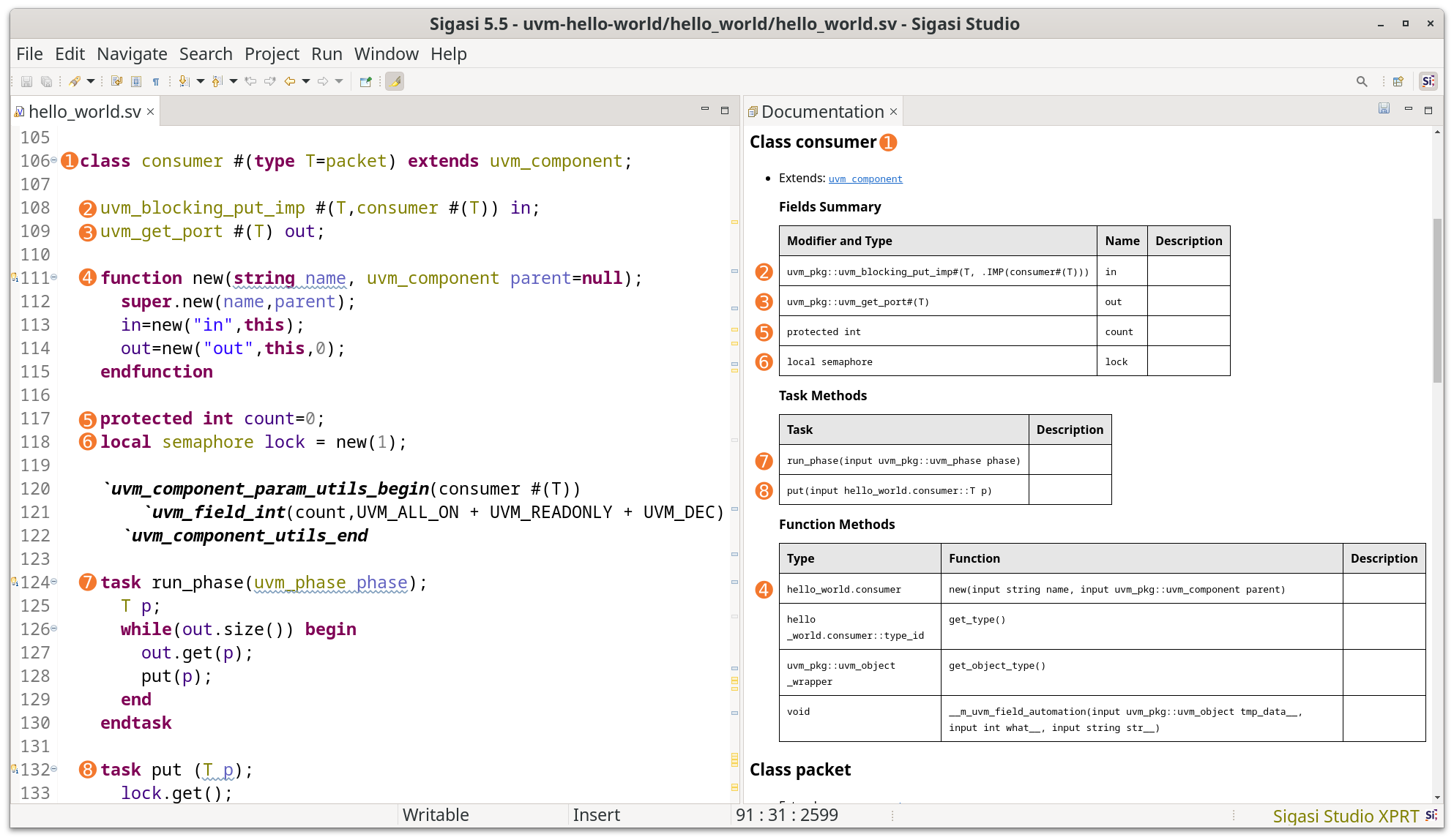

Documentation View

You might know that you can generate documentation for the entire project, but did you know you can also preview it for the file in the editor using the Documentation View? Oh yes.

Learn more

Quality of Life

- Added an option to Generate Documentation without diagrams

- Allowed selection of the outermost block in Block Diagrams

- Verilog Moved the visibility modifier (e.g.

protected) after the type in hovers and the outline - Verilog Added an

Add to Include Pathitem to the right-click menu in the Project Explorer - Verilog Added arguments to functions in the class hierarchy’s member view

- Verilog Added Automatic Include Path Selection

- Verilog Added comments on hover for builtin functions over arrays, strings, classes, and enums

- Eclipse Added clickable icons to Configure Toolchains

- VS Code Enabled diagram generation when using SSH Remote

- VS Code Added automatic expansion of the Projects View when we detect a Sigasi project

- VS Code Redesigned the Preference View to be more user-friendly

- VS Code Added VHDL Identification to the preference view

- VS Code Added a dialog to add language support when opening files of said language

Further New and Noteworthy

- Removed the Find Net menu item for locations where it is not applicable

- Changed the greenish highlighting color in diagrams to blue

- Verilog Replaced

Typeheader byModifier and Typein a class’ generatedFields Summarydocumentation - Verilog Added the

virtualproperty in labels of implicitly virtual methods - VHDL Improved error message when an entity has the same name as a library

- Eclipse Improved instructions in our

readme.txt - Veresta Added exit code

18in case compilation order export failed - VS Code VHDL Added Stuttering

- VS Code Added automatic opening of an editor when creating a new file

- VS Code Improved interaction with other plugins

- VS Code Rewrote our tutorial project to be more realistic and showcase all features

Updates and Deprecations

- Updated to Chromium 106, improving performance and stability and enabling truly headless diagram generation

Talkback Changes

- All Talkback events now include a session ID, meant to group together events coming from the same session of Sigasi Studio

Bug Fixes

- Fixed missing diagram updates

- Fixed a rare case where selected autocompletes were not applying

- Fixed a rare missing build on startup

- Verilog Fixed hierarchy for top levels contained in unmapped files

- Verilog Fixed macro expansion when an assignment pattern (

'{1,2,3}) is used as argument - Verilog Fixed missing connections in the Block Diagram for instantiations in generate blocks

- Verilog Added missing links for enums in the Class Hierarchy

- Verilog Allowed class handles in logical operators

- Verilog Removed false positive error when a

coverpointoverrides its sample methods - VHDL Fixed incorrect URL for Missing Library quick fix

- VHDL Fixed language version awareness for the Unexpected Keyword Capitalization quick fix

- VHDL Fixed missing errors on code with empty conditional bodies

- Eclipse Fixed autocomplete pop-ups on the welcome page

- Eclipse Fixed HTTP error on the Help > Contents page

- Eclipse Fixed newly added Task Tags not highlighting

- Eclipse Fixed quick fixes triggered from the problems view not applying

- Eclipse Fixed rare missing autocomplete at the end of files

- Veresta Fixed error message when using non-existent

locationURIs in the.projectfile - Veresta Fixed

--include-problemsnot including problems - VS Code Fixed background for individual items in the Dependencies View

- VS Code Fixed editor closing when moving the file to a different directory

- VS Code Fixed false positive errors and warnings in

Common Librariesand unmapped files - VS Code Fixed missing updates to diagrams when dragging a file on top of them

- VS Code Fixed missing hover for Verilog modules and ports instantiated in VHDL code

- VS Code Fixed missing borders on highlighted components in diagrams

- VS Code Fixed project initialization to add all necessary build commands to the

.projectfile

Thank you for all the bug reports and for enabling Talkback. All your reports have helped us fix many issues that would otherwise have gone unnoticed.

Sigasi Studio 5.5.1 Point Release

On April 17, we released Sigasi Studio 5.5.1. This release contains the following changes and bug fixes:

- Veresta Added the

--talkbackoption - VS Code Verilog Fixed a bug where Open symbol by name opened the wrong file

- VS Code Improved performance for Open symbol by name

- VS Code Fixed navigation of tree views when using a space or special character in file paths

Sigasi Studio 5.5.2 Point Release

On May 28, we released Sigasi Studio 5.5.2. This release contains the following changes and bug fixes:

- Fixed a specific bug regarding the treatment of the

icharacter on the Turkish locale - Eclipse Fixed missing errors when their messages are too long

- Eclipse Fixed a rare crash when using the diagrams on machines using X

Sigasi Studio 5.5.3 Point Release

On June 19, we released Sigasi Studio 5.5.3. This release contains the following changes:

- VS Code Deprecated the

Sigasi for VHDL & SystemVerilogextension in favor of the brand new Sigasi Visual HDL extension. We recommend updating sooner rather than later. - VS Code Added a deprecation warning and guidance on how to upgrade

Sigasi Studio 5.5.4 Point Release

On July 16, we released Sigasi Studio 5.5.4. This release contains the following change:

- VS Code Fixed typos

System Requirements

- Sigasi Studio standalone supports:

- Windows 10 or Windows 11 64-bit

- RedHat Enterprise Linux RHEL 7.9 64-bit or newer, including RHEL 8 and 9

- Sigasi Studio depends on

libXss.so, which is obtainable by installinglibXScrnSaver - Sigasi Studio depends on

webkit2gtk4.0, which is installable through your package manager of choice - Note that Sigasi 5.5 is the last version to officially support the soon-to-be end-of-life RHEL 7

- Sigasi Studio depends on

- You can find more information on supported Linux Operating Systems on the Eclipse website

- Sigasi Studio as a plugin in your Eclipse installation:

- Eclipse IDE 2021-03 up to and including Eclipse IDE 2023-03

- Java JRE 11 or 17

- Sigasi Studio extension for VS Code:

- Windows 10 or Windows 11 64-bit

- RedHat Enterprise Linux RHEL 8 or 9 64-bit

- VS Code >= 1.77 and < 2.0

- Java JRE 11 or 17 (shipped with the extension)

- Veresta

- Windows 10 or Windows 11 64-bit

- RedHat Enterprise Linux RHEL 7.9 64-bit or newer, including RHEL 8 and 9

- Note that Sigasi 5.5 is the last version to officially support the soon-to-be end-of-life RHEL 7

- Java JRE 11 or 17 (shipped with Veresta)

We recommend having at least 4GB of memory and about 1GB of free disk space available for Sigasi Studio.