Sigasi 5.4 introduces many new UVM linting rules, simpler linting rule configuration, as well as VS Code diagrams and documentation generation.

As usual, Veresta and our VS Code extension benefit from all the changes not explicitly marked as Eclipse.

TL;DR

The Sigasi 5.4 release introduces a range of new XPRT linting rules specifically for UVM. For a limited time, we would like to offer our Sigasi Studio XL

license users a chance to enjoy these UVM linting rules through our new

✨ XPRT preview.

As of the 5.5 version, these features will be available only to Sigasi Studio XPRT users.

Want to know more about our UVM features, or would you like to upgrade your license? Contact us.

To complement these UVM linting rules, we added a bonus general Verilog linting to prohibit certain macros.

Meanwhile, we gave VHDL a highly configurable linting rule to flag missing labels.

Keeping with the theme of linting rules, their configuration just got simpler and safer in Eclipse. The preference page contains a search field to quickly find the rule to configure. Parameter values are now validated when configuring rules. On top of that, you will find the multi-text editor is more streamlined.

Eclipse is not the only IDE favored in this release; VS Code has received many new features, too. It gained linting rule configurability through a new preference page, though, more importantly, we added full diagram support and documentation generation for our VS Code users, too.

Finally, this release sees a wide range of over 60 bug fixes and improvements.

P.S.: For consistency and ease of use, we updated some default linting rule severities. As a result, you might see a different number of linting violations at differing severity levels in your projects after upgrading to Sigasi 5.4. Learn more

UVM Linting Rules

Note that these rules are temporarily available to Sigasi Studio XL users in this 5.4 release through ✨ XPRT preview. As of 5.5, they will only be available to Sigasi Studio XPRT license holders.

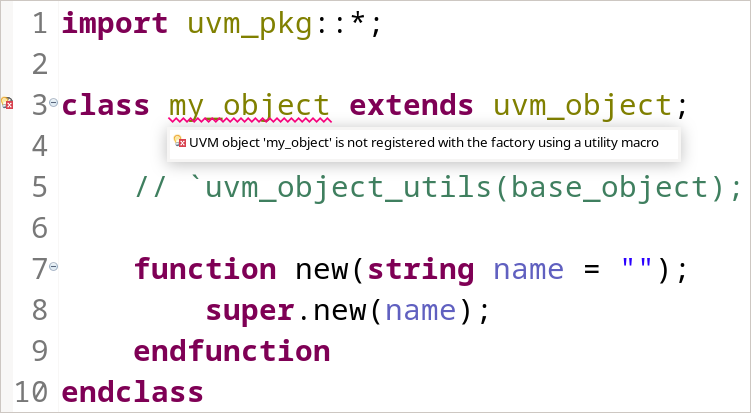

Unregistered UVM Object

To fully utilize UVM’s functionality, objects and components need to be registered with the factory through one of the utility macros.

This rule can be configured to allow unregistered virtual UVM objects.

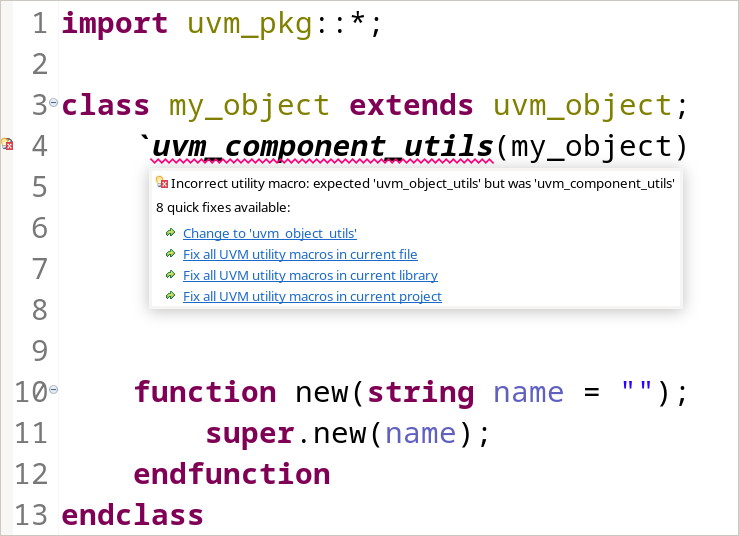

Incorrect Utility Macro

UVM objects are registered through uvm_object_utils. However, UVM components have to be registered using uvm_component_utils.

my_object is a uvm_object so it requires uvm_object_utils. There is a Quick Fix for these kinds of small oversights.

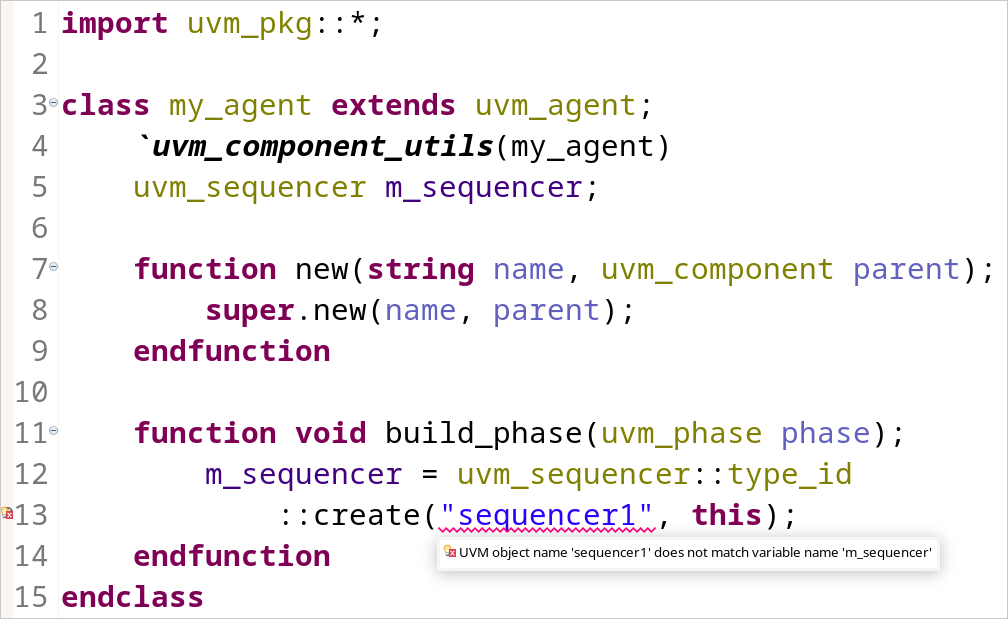

UVM Object Name Does Not Match Variable Name

To facilitate debugging, the variable name in a create method should equal the UVM object name.

In this instance, the variable name m_sequencer does not match the object’s name “sequencer1”. Such a mismatch can be confusing, especially when debugging.

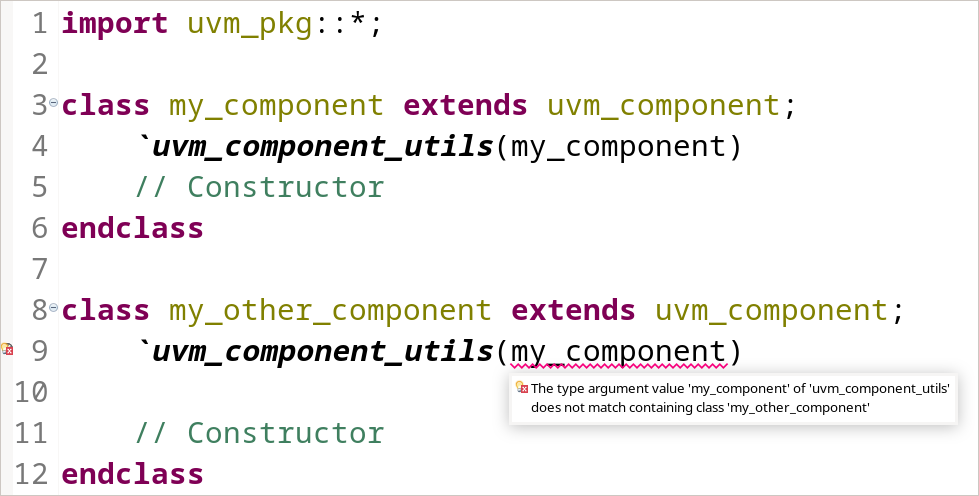

Type Argument Value Does Not Match Containing Class

Some UVM macros require the first argument to equal the containing class.

Due to copy-pasting code from my_component to my_other component, the incorrect class is passed to the uvm_component_utils macro.

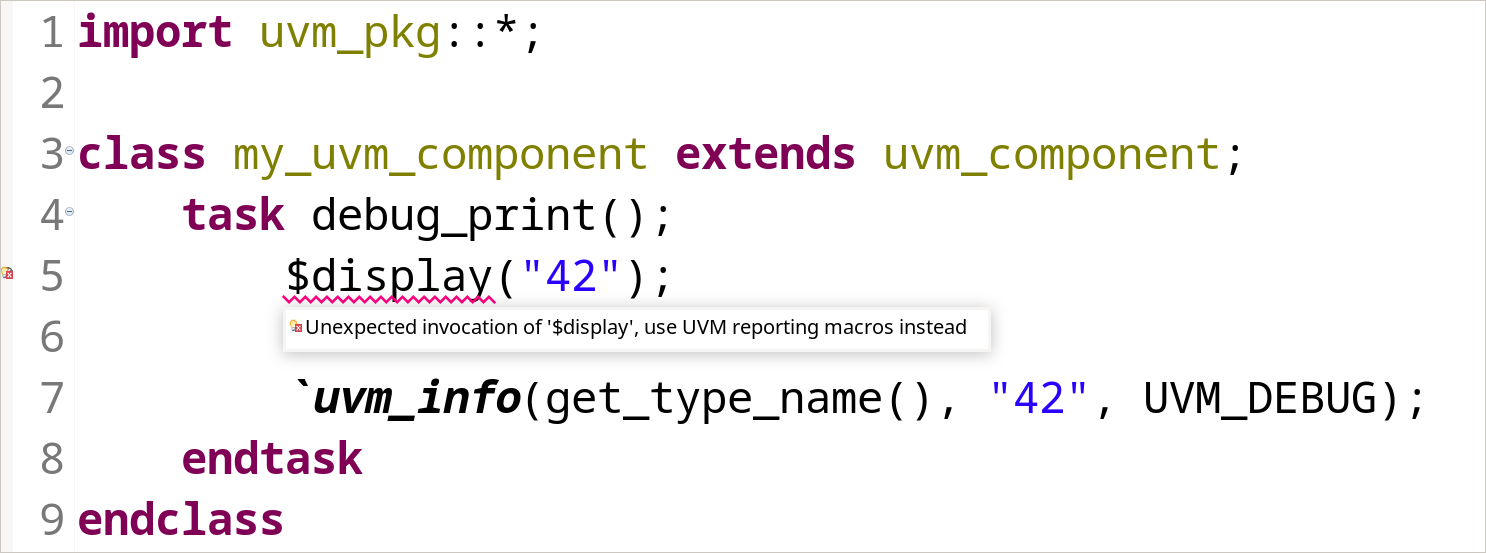

Unexpected Output System Task

To prevent overloading your simulations, you should use UVM’s granular logging.

$display will indiscriminately log at all times, while `uvm_info allows for control over the logging verbosity.

This rule can be configured to report file output system tasks such as $fdisplay and $fwrite too.

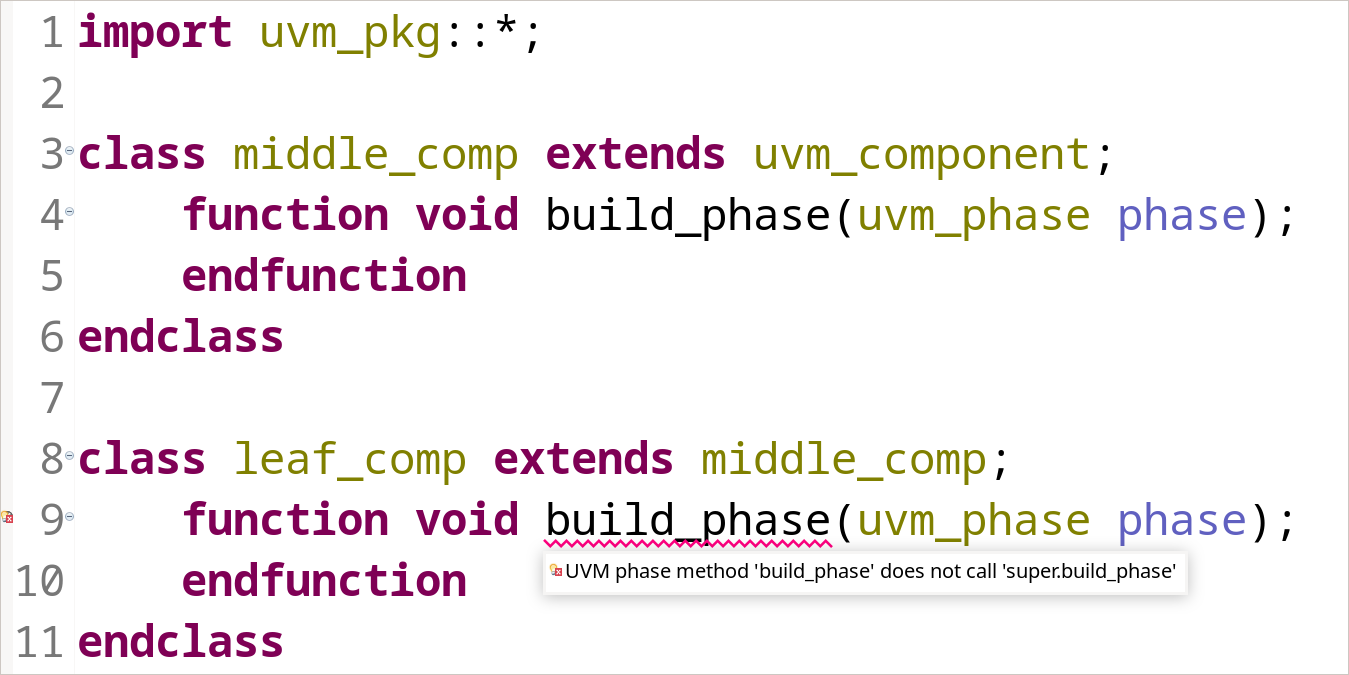

UVM Phase Method Does Not Call Superclass Method

Whenever you subclass a user-defined class, the superclass’ phase method should be called when they are overridden.

leaf_comp::build_phase overrides middle_comp::build_phase, and thus the former should call the latter.

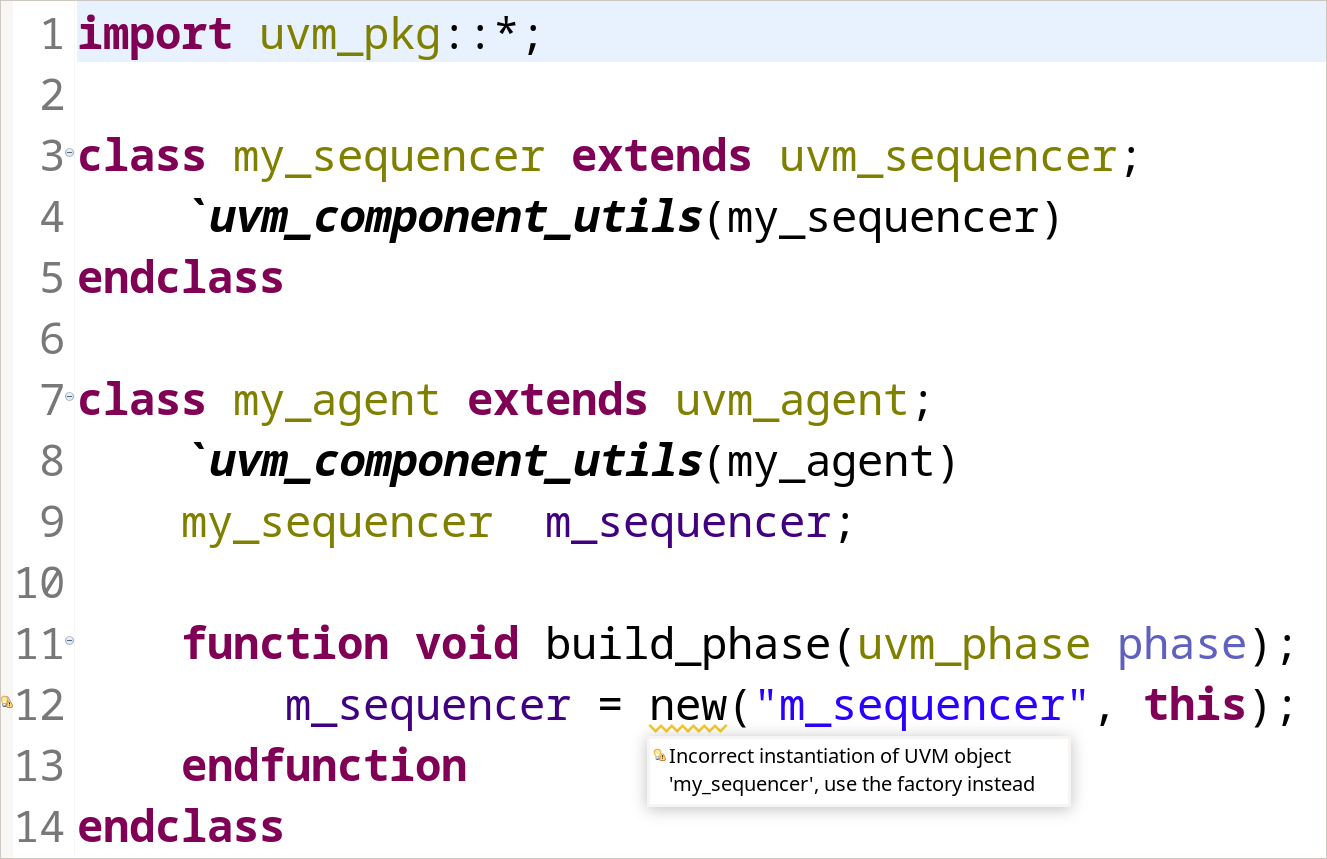

Incorrect Instantiation of UVM Object

new(), UVM objects and components must be instantiated by the factory to allow UVM to use overloaded types.Incorrect Override of UVM Object

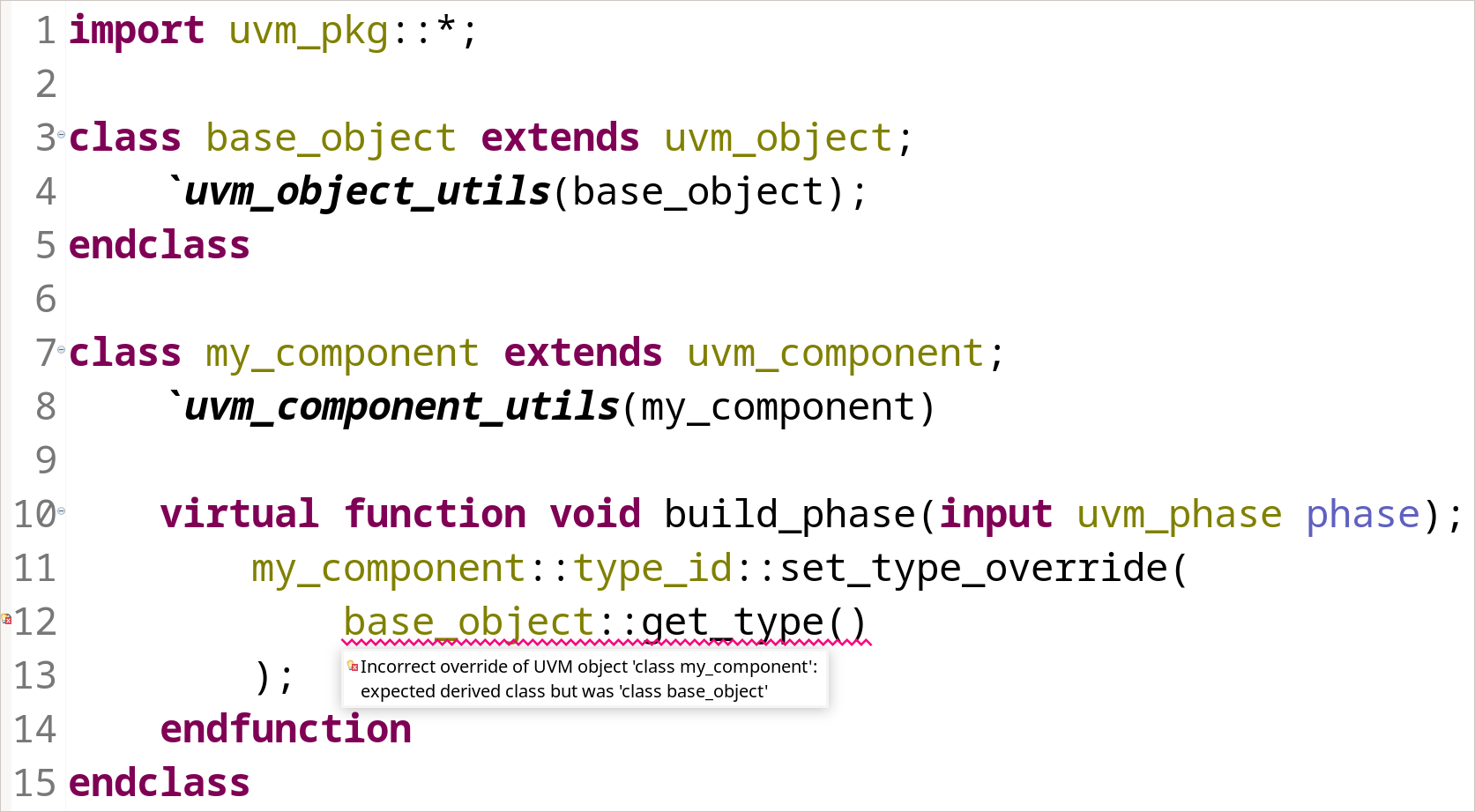

When overriding UVM objects or components, the overriding type needs to be a subclass of the overridden type.

In this case, my_component is not a subclass of base_object.

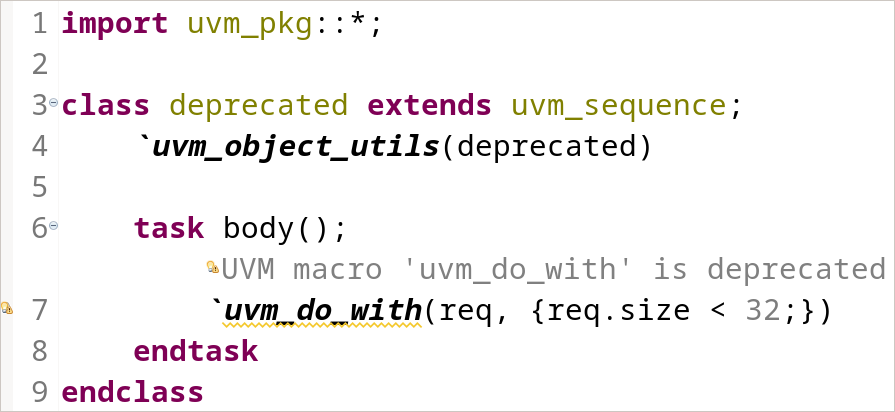

Deprecated UVM API

With the many UVM versions come many deprecations.

For example, the uvm_do_with macro was deprecated in UVM 1.2 and was subsequently removed in UVM 2017.

This rule can be configured to target a specific UVM version, allowing you to gradually prepare for UVM upgrades.

Incorrect Constructor for UVM Object or Component

UVM mandates that a UVM component has a constructor with a string name and uvm_component parent argument. The implicit constructor does not have these.

A similar constraint is validated for UVM objects.

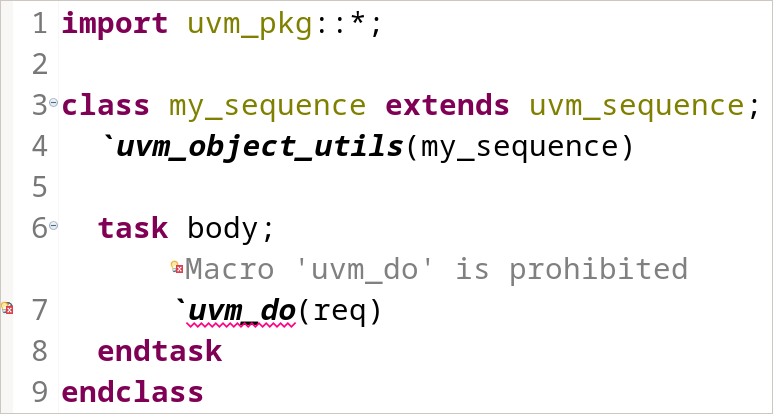

Bonus: Prohibited Macro

In UVM and Verilog in general, some macros are often discouraged, whether because of deprecation, coding style, or company guidelines. It is now possible to flag such prohibited macros in Sigasi.

In UVM, for example, you can choose to create transactions manually. Prohibiting `uvm_do would then be a good idea.

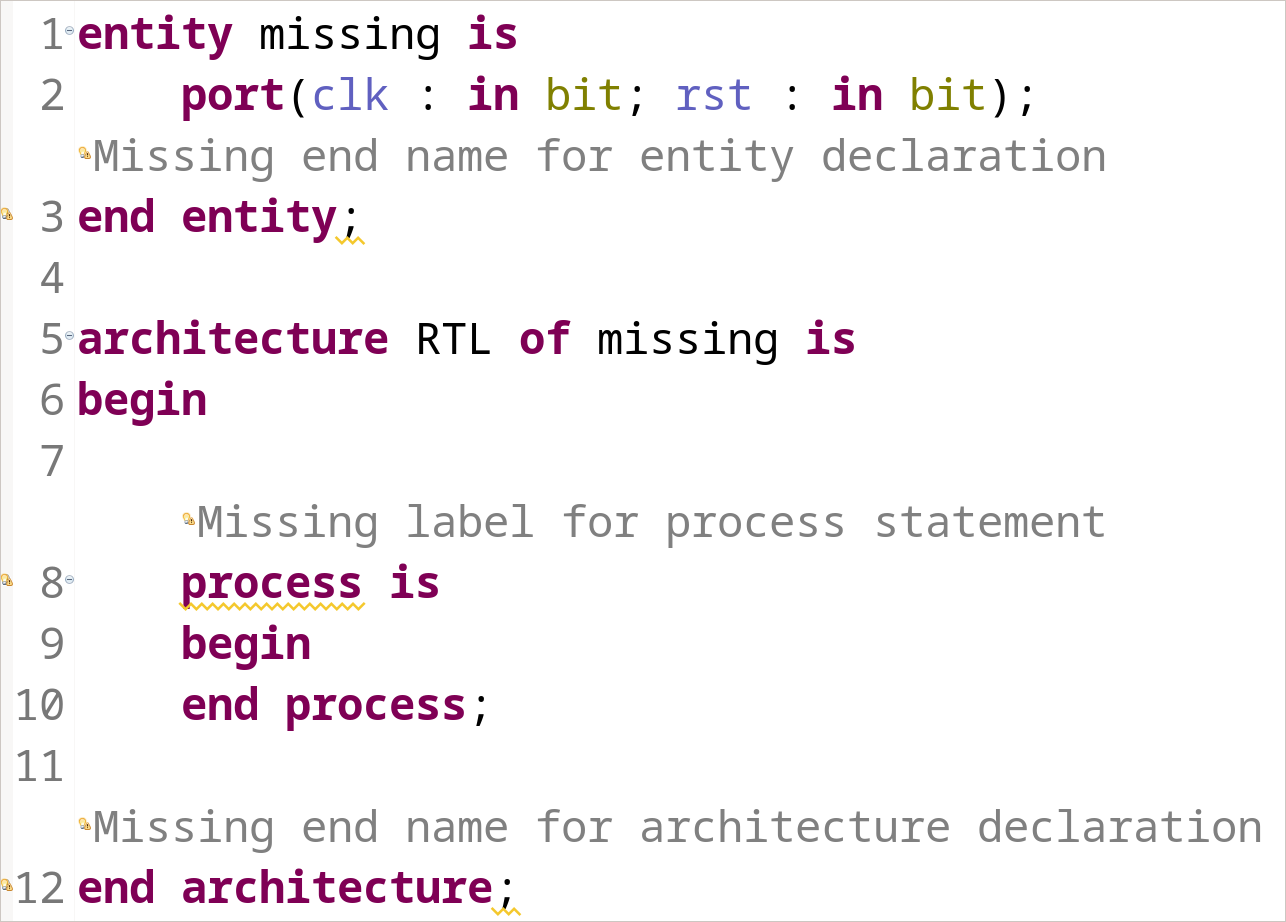

Missing Label

In VHDL, coding guidelines often enforce the use of labels for certain constructs.

This highly configurable linting rule allows you to do just that. You can differentiate between labels, end labels, names, and end names where applicable.

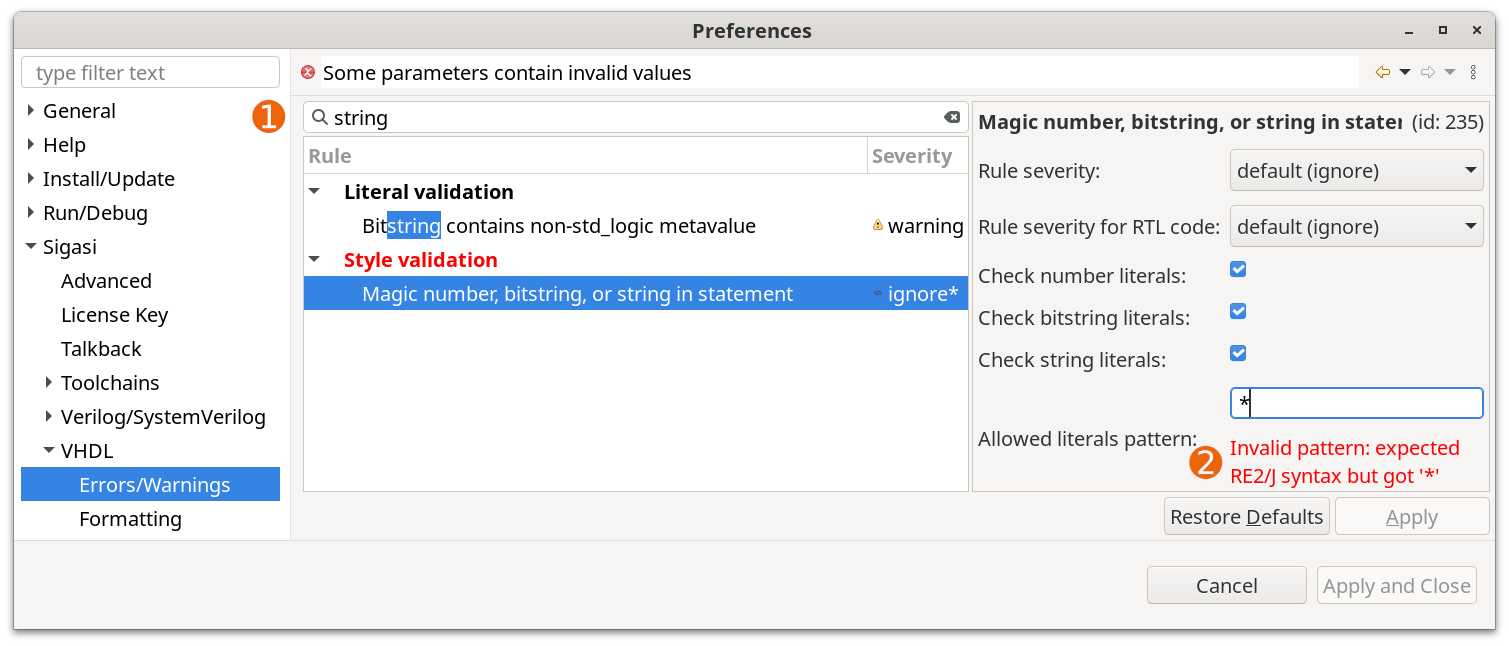

Simpler Linting Rule Configuration

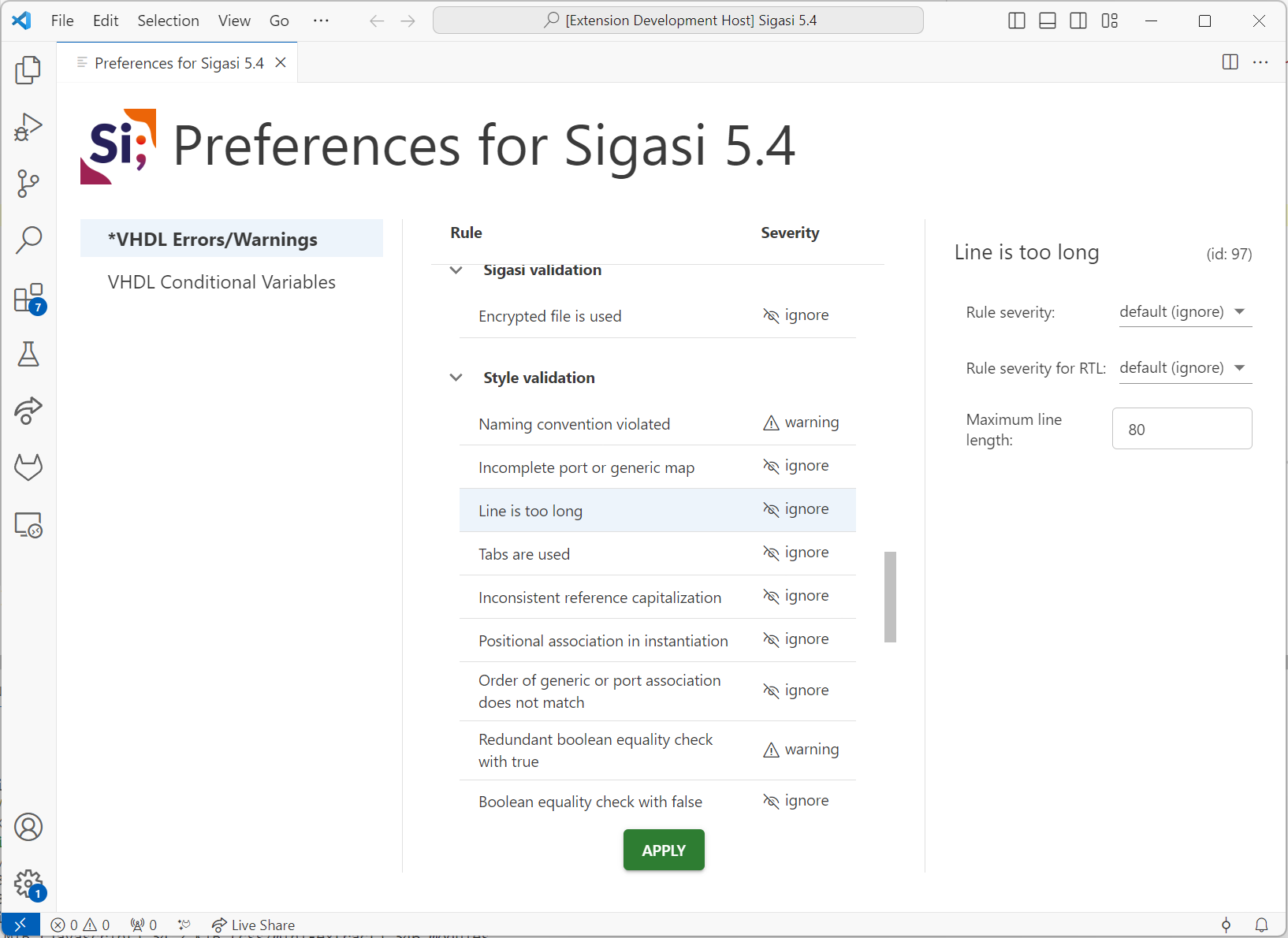

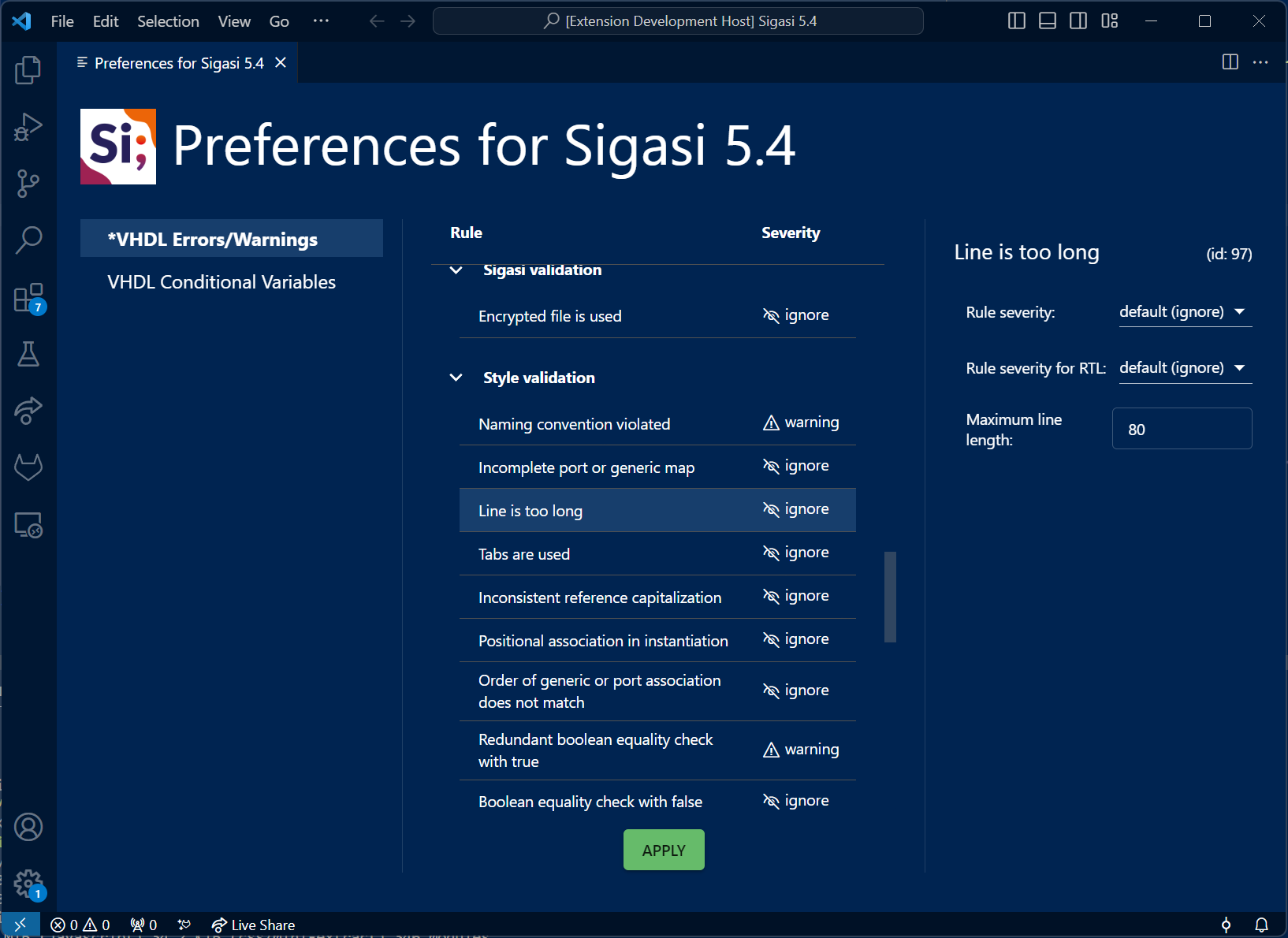

In this release, we made linting rule configuration simpler through changes to the preference page.

- ➊ Added a search bar

- ➋ Added validation for all rule configuration values

- Improved usability of the multi-text input fields

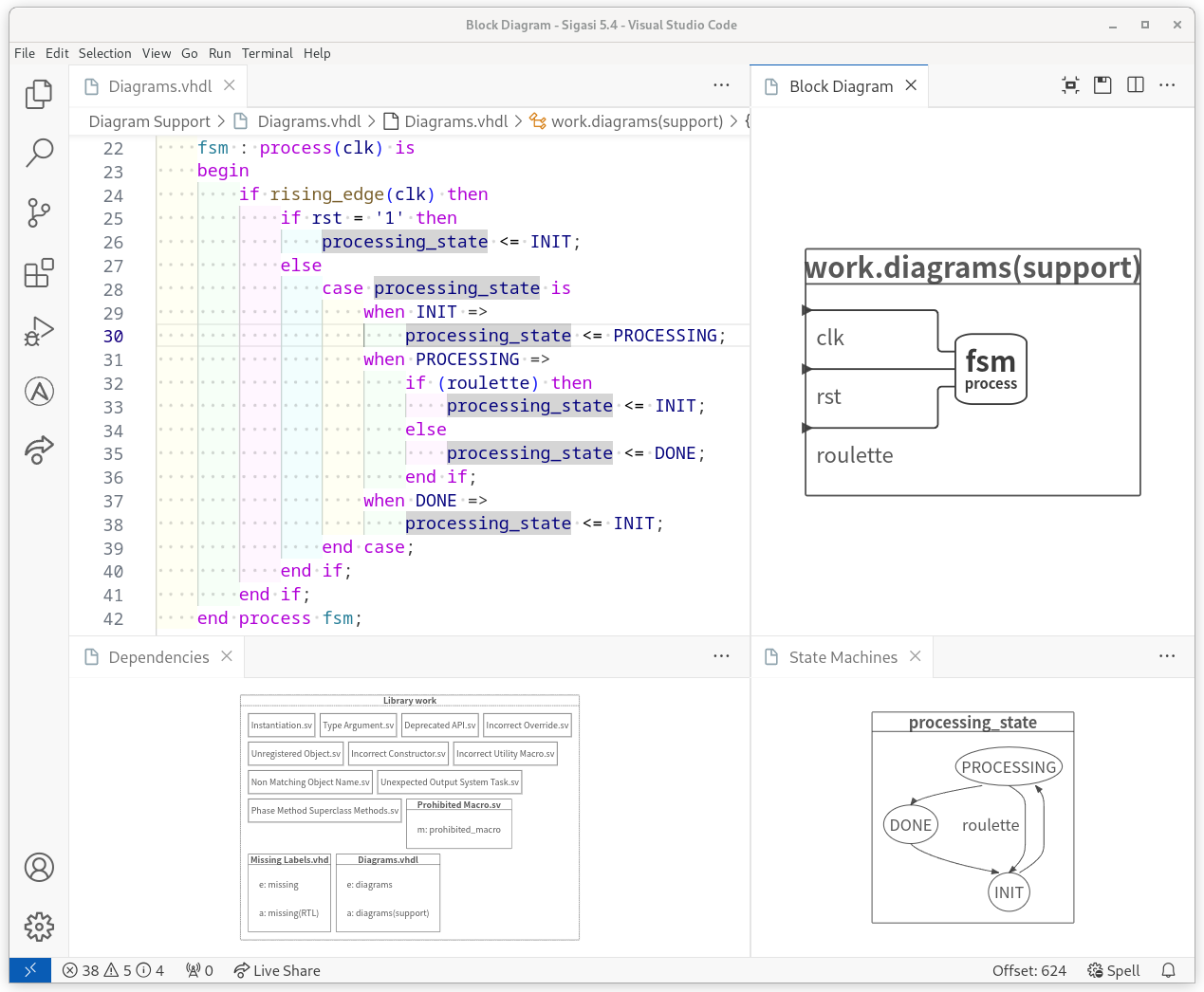

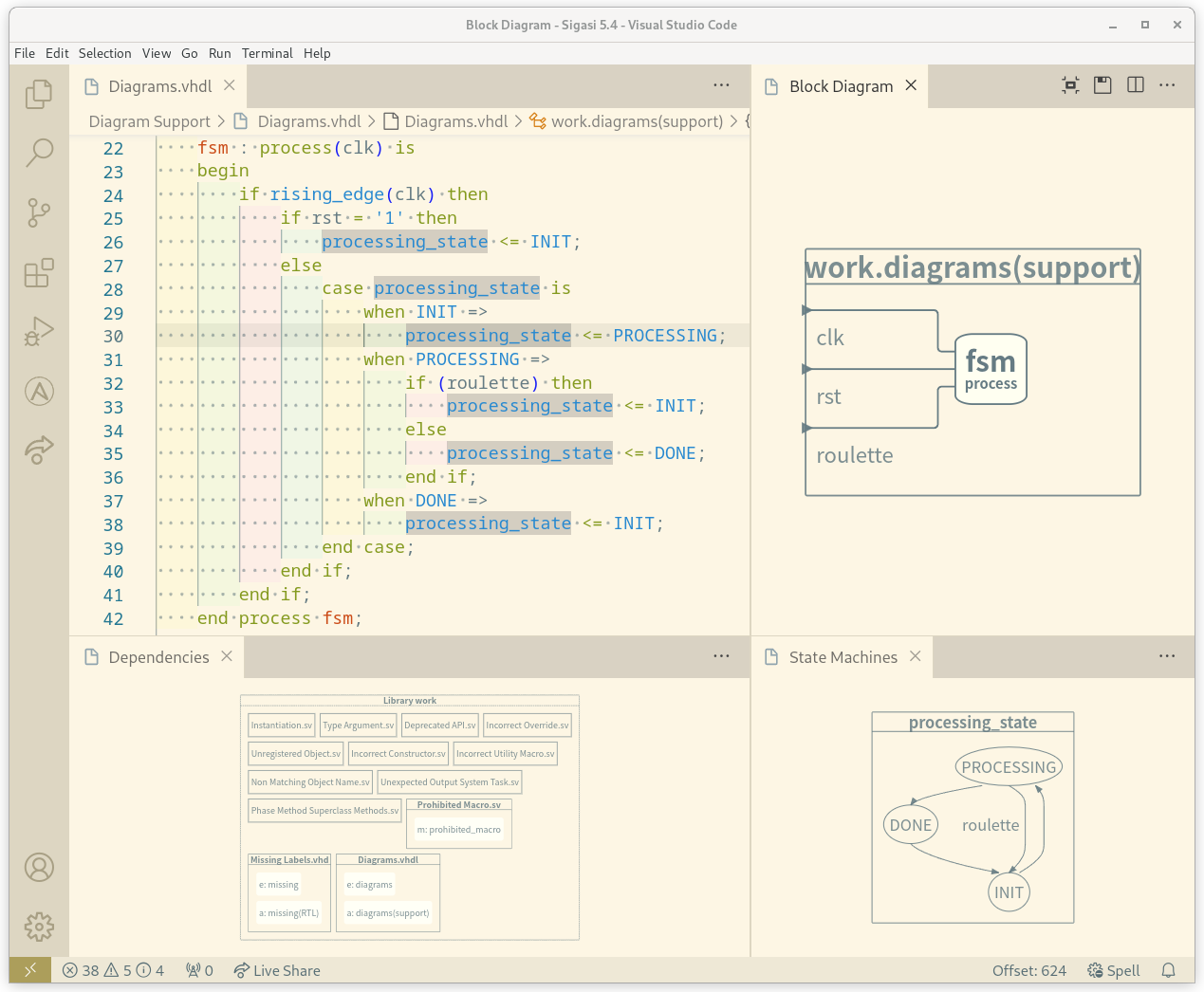

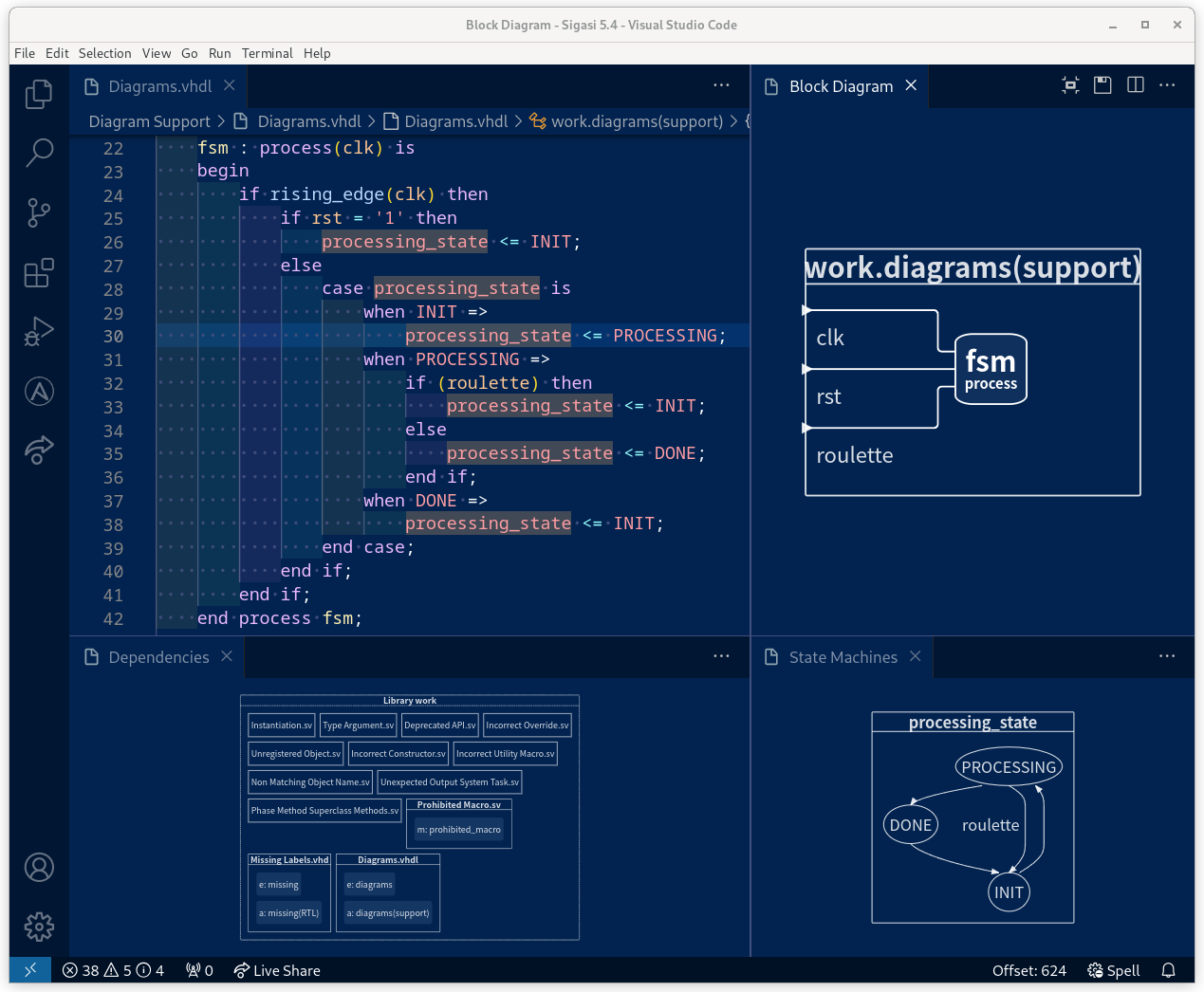

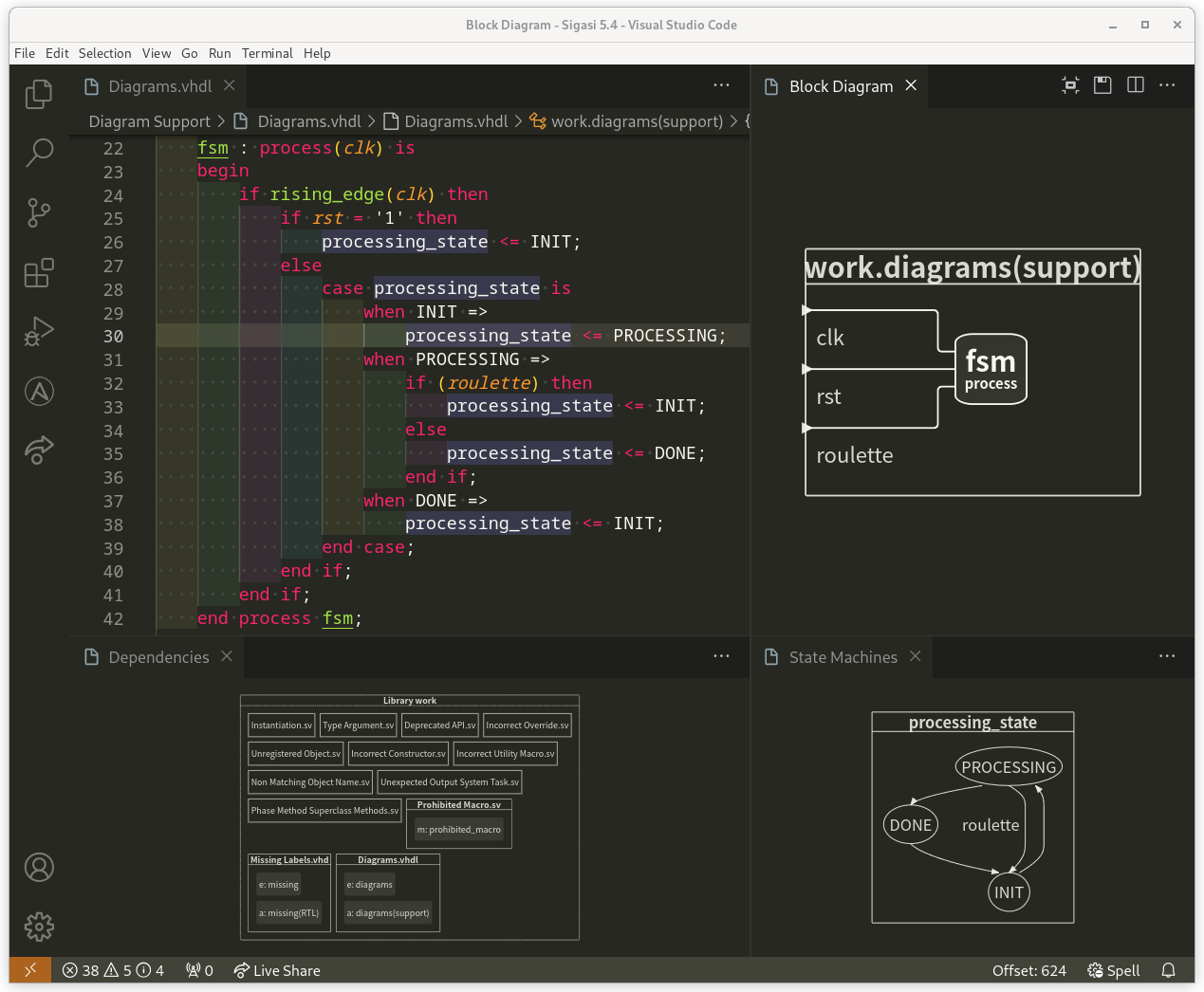

VS Code Sneak Peek

Our VS Code extension is picking up steam. This release adds full diagram support, documentation generation, and linting rule configurability. Read up on all the new changes in the changelog .

Full Diagram Support

All the diagrams in Sigasi Studio for Eclipse are now available in VS Code: Block Diagram, State Machines, and Dependencies. Learn more

Note that a Sigasi Studio XPRT license is required for these.

Documentation Generation

With diagram support added, generating and exporting the documentation from VS Code is also possible.

Learn more

Linting Rule Configuration

All Sigasi linting rules are now fully configurable per file, folder, or project.

Learn more

Quality of Life

- Lowered priority for formatter tags autocomplete suggestions

- VHDL Fixed Auto Indentation following function prototype declarations and assignment statements with

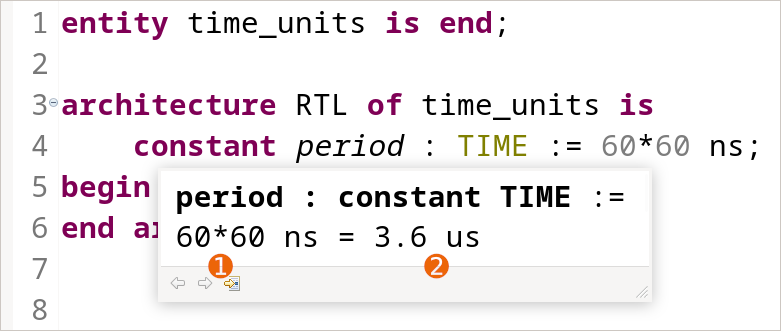

whenclauses - VHDL Show units of measurement in a well-known unit instead of using the smallest one, e.g.,

10000 fs→10 ps - VHDL Added formula ➊ and solution ➋ to hovers when constant propagation is applied

- Improved Hierarchy View

- VHDL Removed redundant

No constants/genericsnodes - VHDL Added missing labels for positional generic associations in instantiations

- Verilog Added missing branches for conditional statements

- Verilog Added missing labels for assignments to arrays

- Eclipse Adopted a new icon

to differentiate from the Class Hierarchy View

to differentiate from the Class Hierarchy View

- VHDL Removed redundant

- Verilog

Eclipse Improved Class Hierarchy View

- Added differentiating icons for variables, tasks, classes, constructors, enums, and more

- Added a visual indication of member visibility and whether a member is static or overridden

- Eclipse Fixed issue with inconsistent sizing of hovers on Linux

- Eclipse Improved the initial selection of export wizards

- Eclipse Improved the available information on the License Preference Page

- Eclipse Pick up renamed VUnit tests when rerunning a test suite

Further New and Noteworthy

- Added Quick Fixes to suppress problems file-, library-, or project-wide

- Added automatic building following a change to the contents of the

.settingsfolder - Extended the Verilog Keywords in VHDL linting rule with entity ports and generics

- VHDL Added vertical alignment to Template Autocomplete suggestions

- VHDL Added support for VHDL 2019 attributes

- VHDL Added constant propagation in hovers and linting rules for the

'reverse_rangeattribute - Verilog Improved preprocessor syntax error messages

- Verilog Added formatting rules for

typedefconstraint- anonymous

program randsequencerandcaseprimitivemoduleparameterscovergroup

- Eclipse

Add to buildadds the selected resource to the parent library instead ofwork - Eclipse Improved VUnit support

- Added link to VUnit documentation in its preference page

- Support using a

run.pywithin the Common Libraries folder - The VUnit JSON library is now automatically linked when it is used in the

run.py

- Eclipse Handle extended identifiers (

\RT L\and\sv$module) in the Sigasi CSV Auto Export - Eclipse Added the

${sigasi_toplevel:alt}variable - Eclipse Capitalized menu items consistently

- Eclipse Started using Cadence XCelium binaries instead of the deprecated Cadence NCsim ones when Cadence is selected as Toolchain

Updates and Deprecations

- Removed the

Naming convention configuration uses syntax which is deprecatedvalidation - Eclipse JustJ - Sigasi Studio ships with JustJ JRE 17.0.9.

Updated Linting Rule Severity

Some VHDL linting rules had their default severity adjusted. If you did not specify a custom severity for them, you might see fewer (or more) problems in existing projects.

| Rule | Old | New |

|---|---|---|

| Deprecated IEEE Packages and Non-Standard Packages | warning | info |

| Space Before the Physical Unit | warning | info |

| Incomplete Port Maps and Generic Maps | warning | ignore |

| Capitalization of Identifiers | warning | ignore |

| Positional Association in Instantiations | warning | ignore |

| Order of Associations | warning | ignore |

| Type validation | warning | error |

| Unconstrained Signal or Variable of Integer Type | ignore | warning for RTL |

Talkback Changes

- Added the Sigasi version to every Talkback message

Bug Fixes

- Fixed the up and down icons in the Net Search in the presence of duplicate nodes

- Improved Block Diagram View

- Fixed missing update when changing only a port direction

- Fixed missing connections after collapsing a block

- VHDL Added a

Pcharacter in the otherwise empty block of unnamed processes

- Improved the Dependencies View

- Removed self-references

- Fixed the initial state of the

Show all files in projectbutton

- Improved Autocomplete

- VHDL Fixed empty argument names and types in procedure suggestions

- VHDL Removed invalid entity instantiation suggestions

- VHDL Fixed missing autocomplete in the

configurationconstruct - Verilog Fixed rare missing preprocessor autocomplete

- Eclipse Fixed overriding of the selected text when holding Ctrl while applying an autocomplete suggestion

- Improved Formatting

- VHDL Added missing formatting for parameter types

- Verilog Fixed leading whitespace during formatting of included files

- Verilog Fixed rare case where formatting produced invalid code

- VHDL Improved Quick Fixes

- Fixed the addition of a trailing comma when applying the

Add missing associationsQuick Fix - Fixed the addition of an empty line when applying the

Missing generic mapQuick Fix - Fixed rare cases where the

Add missing associationsQuick Fix was not applied

- Fixed the addition of a trailing comma when applying the

- VHDL Fixed false positive

No matching subprogramwhen using VHDL 2008 or 2019 - Verilog Fixed highlighting of backticks in preprocessor directives

- Verilog Added missing links (Ctrl+click) when two conditional blocks have the same label

- Verilog Removed duplicate naming convention warning when using enum element ranges e.g.

enum {A[0:100]} e - Verilog Eclipse Fixed missing updates to the Class Hierarchy

- Eclipse Fixed qualified name in the Find References title

- Eclipse Fixed missing updates to the Libraries View

- Eclipse Fixed incorrect project name shown in the Project Explorer

- Eclipse Renamed references from

Intel Quartus IItoIntel Quartus - Eclipse Fixed severity editing on the linting rule preference page on the Turkish locale

- Eclipse Fixed small inconsistencies in the tutorial project

Thank you for all the bug reports and for enabling Talkback. All your reports have helped us fix many issues that would otherwise have gone unnoticed.

Sigasi Studio 5.4.1 Point Release

On December 22, we released Sigasi Studio 5.4.1. This release contains the following changes and bug fixes:

- Fixed context menus not filtering their menu items

- VHDL Fixed Project Formatting in combination with Formatter Tags

Sigasi Studio 5.4.2 Point Release

On February 13, we released Sigasi Studio 5.4.2. This release contains the following changes and bug fixes:

- Verilog Fixed missing naming convention warning on generate blocks

System Requirements

- Sigasi Studio standalone is supported on:

- Windows 10 or Windows 11 64-bit

- RedHat Enterprise Linux RHEL 7.9 64-bit or newer, including RHEL 8 and 9

- Sigasi Studio depends on

libXss.sowhich can be obtained by installinglibXScrnSaver - Sigasi Studio depends on

webkit2gtk4.0which can be installed through your package manager of choice

- Sigasi Studio depends on

- More information on supported Linux OSes can be found on the Eclipse website

- Sigasi Studio as a plugin in your Eclipse installation:

- Eclipse IDE 2021-03 up to and including Eclipse IDE 2023-03

- Java JRE 11 or 17

- Sigasi Studio extension for VS Code:

- Windows 10 or Windows 11 64-bit

- RedHat Enterprise Linux RHEL 8 or 9 64-bit

- VS Code >= 1.77 and < 2.0

- Java JRE 11 or 17 (shipped with the extension)

- Veresta

- Windows 10 or Windows 11 64-bit

- RedHat Enterprise Linux RHEL 7.9 64-bit or newer, including RHEL 8 and 9

- Java JRE 11 or 17 (shipped with Veresta)

We recommend having at least 4GB of memory and about 1GB of free disk space available for Sigasi Studio.