Sigasi Studio 5.3 introduces many new DO-254 compatible VHDL design linting rules, more ways to check coding guidelines and naming conventions, means to differentiate between RTL and non-RTL code, as well as new Verilog vector linting rules and enhanced support for SystemVerilog parameterized classes.

As per usual, Veresta and our VS Code extension benefit from all of the changes not explicitly marked as Eclipse. Additionally, Veresta 5.3 brings project documentation generation to your CI/CD environment.

TL;DR

Sigasi 5.3 introduces many new VHDL style rules to implement your project-specific coding guidelines and naming conventions. You can now enforce coding conventions such as line length, prohibited language features, consistent vector directions, keyword capitalization, and many more. Furthermore, we are adding new naming conventions for constructs such as input/output/inout ports, enumeration literals, functions, and procedures. These can be configured with new visually pleasing preference pages. These allow you to configure different severities for RTL code and non-RTL code. Finally, we have split off header comment pattern matching into separate preferences, e.g., for entities, packages, and function header comments.

Aside from the style rules mentioned above, five VHDL design linting rules make their entrance:

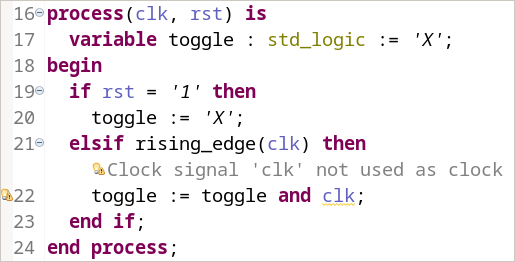

- Clock signal not used as clock

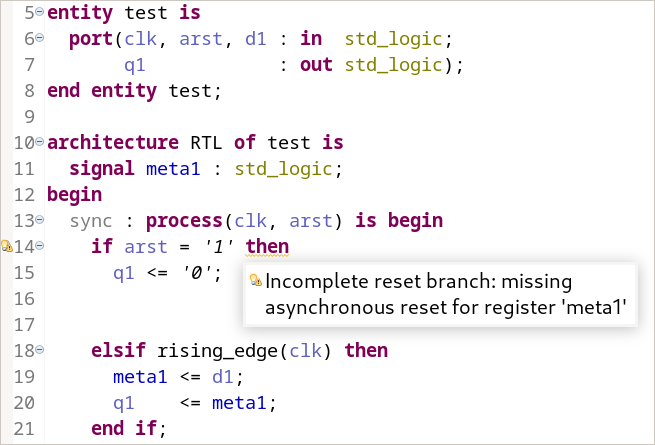

- Incomplete reset branch

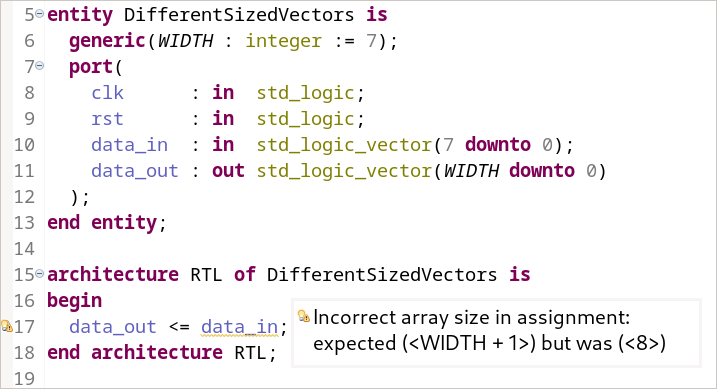

- Comparison of vectors with different sizes

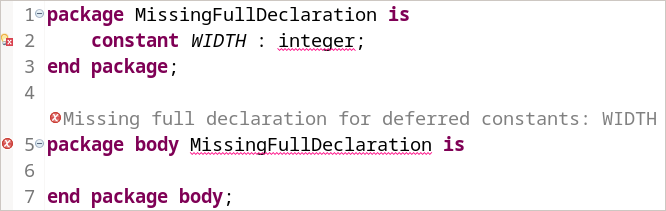

- Missing full constant declaration

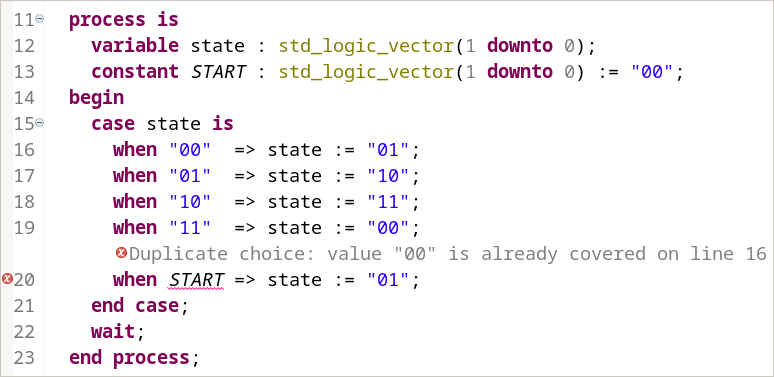

- Duplicate choices in case statements

Many of these new design and style linting rules apply to the DO-254 standard. Sigasi 5.3 is an essential tool for working towards a fully compliant DO-254 design process.

Beyond VHDL, there are two new Verilog linting rules regarding vector usage:

- Implicit vector to boolean conversion

- Vector as edge event expression

SystemVerilog designers will be pleased to learn that Sigasi’s support for parameterized classes was greatly improved in this release, too. Navigating complex class hierarchies is a breeze and meaningful feedback is provided at type-time.

Autocomplete for all languages has received a speedup of up to 50% for large projects and a more complete list of suggestions is offered.

As announced in the previous releases, we have removed the support for the Graphics Configuration Language.

Finally, this release is once again packed with many bug fixes and small improvements.

VHDL Linting Rules

Sigasi 5.3 offers more than 250 VHDL linting rules.

New Preference Pages

All of these new preference pages are available in Eclipse.

Linting Configuration

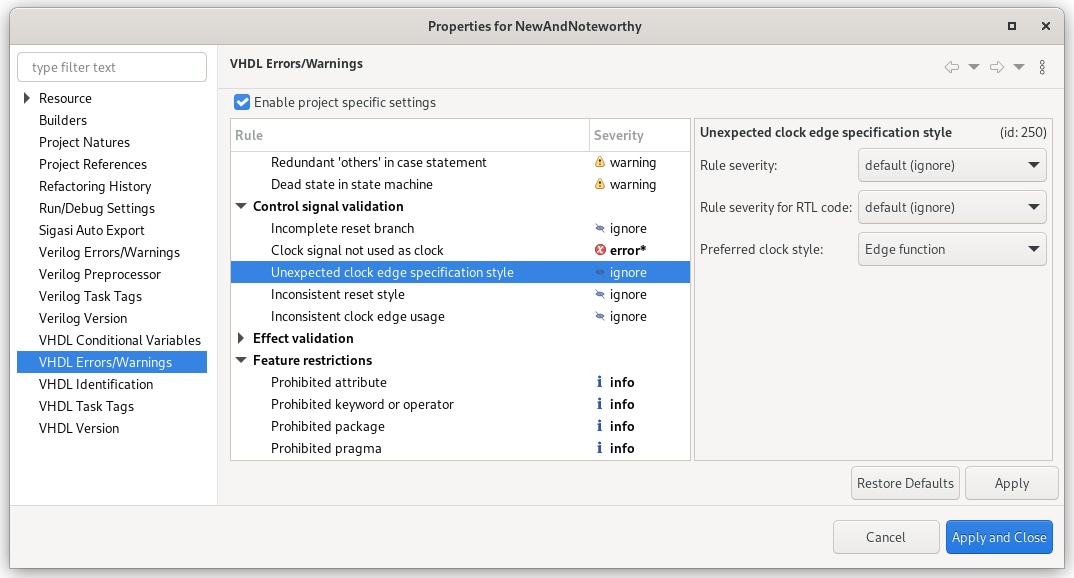

Before we jump into all the VHDL linting rules, let us first show you how to configure them using the redesigned linting rule preference page (Right-click project > Properties > Verilog/VHDL Errors/Warnings).

- New foldable families allow for easy grouping of linting rules and editing their severities

- Improved descriptions of all linting rules

- Icons now visually highlight the currently configured severity

- Many linting rules have parameters that can be tweaked in this view

- Linting rule severities can be set separately for RTL and non-RTL code

VHDL Identification

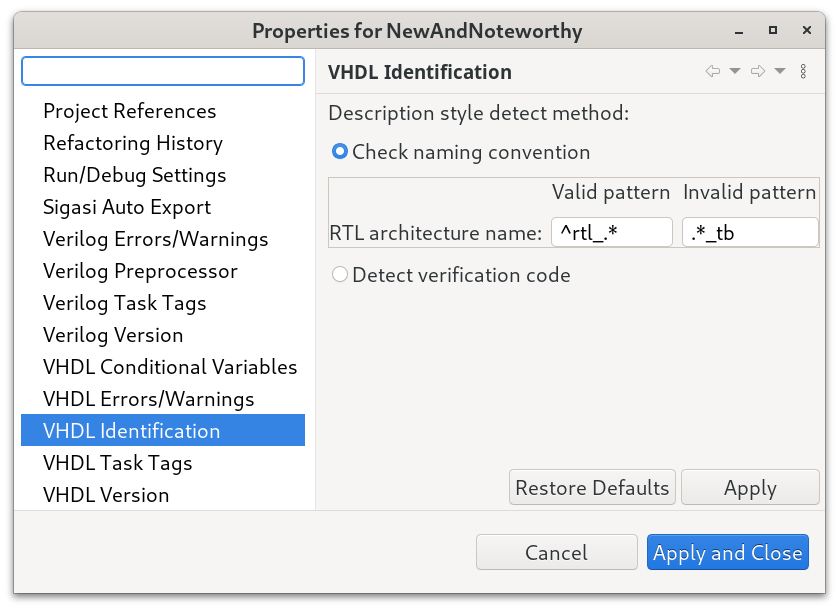

The RTL code detection mechanism can be configured per project by going to Right-click project > Properties > VHDL Identification.

- Via a naming convention for an RTL architecture

- By detecting verification code

This allows you to set different linting rule severities for RTL and non-RTL code.

Learn moreNaming Conventions

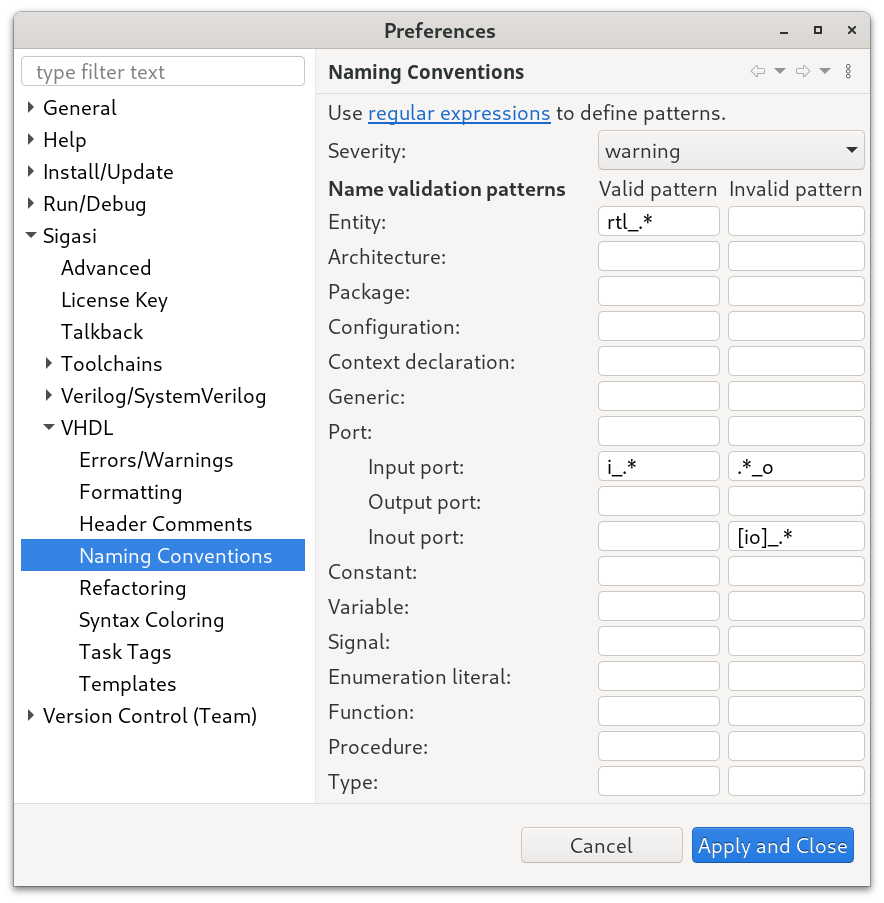

We have extended the Naming Conventions preference page at Window > Preferences > Sigasi > VHDL > Naming Conventions. Naming conventions can now also be configured using an invalid pattern and many additional naming conventions are available.

Learn moreComment Headers

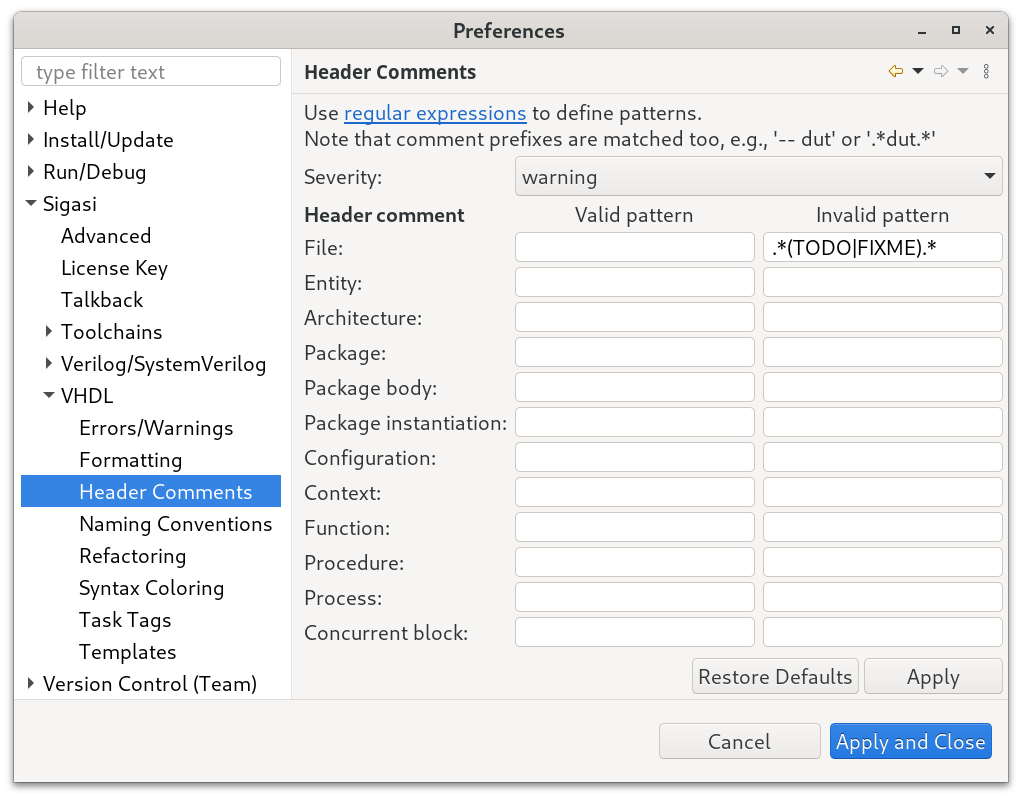

The Comment Header configuration moved from the naming conventions to a new preference page at Window > Preferences > Sigasi > VHDL > Header Comments. Aside from files, headers describing constructs such as entities, packages, and functions can now also be validated.

Learn moreDesign Linting Rules

These rules check for potential design flaws and coding errors. They are enabled by default, but you can usually edit their severity and parameters through your project preferences: Right-click project > Properties > VHDL Errors/Warnings.

Clock Signal Not Used as Clock

Incomplete Reset Branch

Comparison of Vectors with Different Size

Missing Full Constant Declaration

Case Alternative Contains Duplicate Choices

Style Rules

Style rules check a certain coding style. Since they are a question of taste, they are set to

![]()

ignore by default. You can enable them in your project preferences: Right-click project > Properties > VHDL Errors/Warnings.

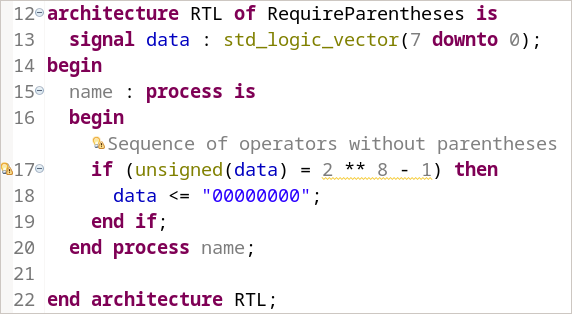

Sequence of Operators without Parentheses

While it is not necessary to add parentheses, they can clarify evaluation order in expressions with operators of different associativity.

You might wonder, is it 2 ** (8 - 1) or (2 ** 8) - 1? (Narrator: It is the latter)

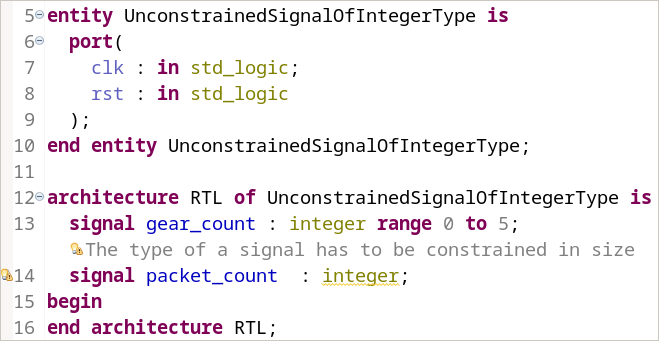

Unconstrained Signal or Variable of Integer Type

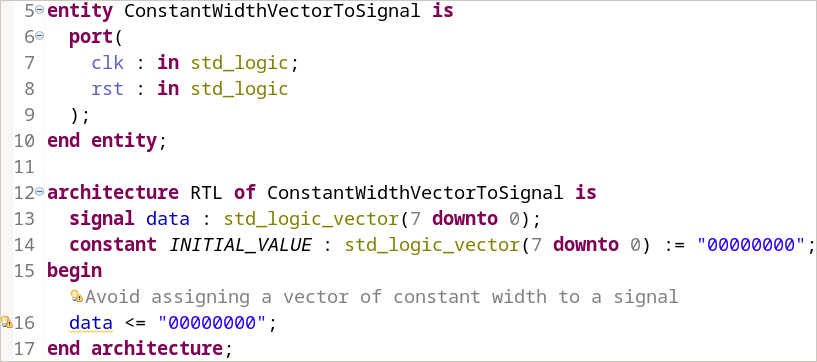

Constant Width Vector Assigned to Signal

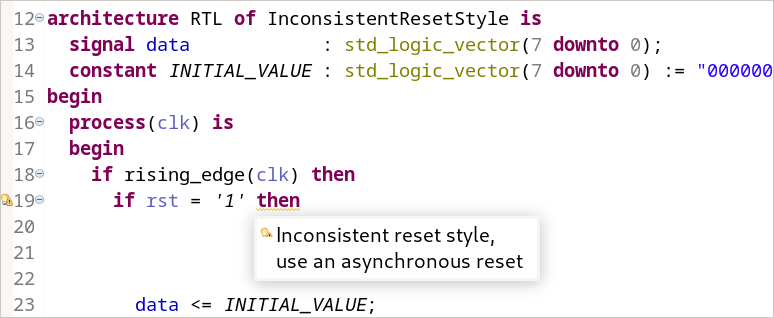

(others -> '0')) prevent potential maintainability hurdles.Inconsistent Reset Style

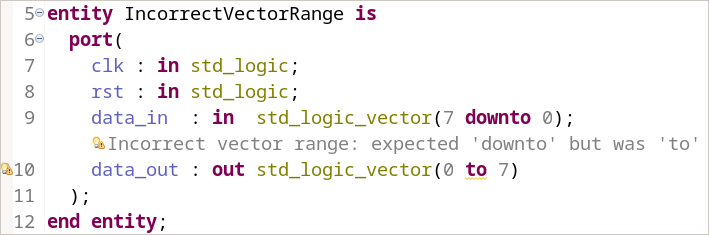

Incorrect Vector Range Direction

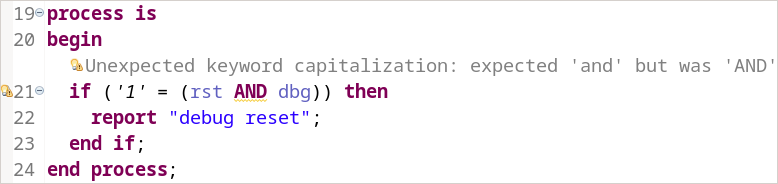

downto) as this causes the leftmost bit to be the most significant and the rightmost to be least significant; this is what the VHDL standard library’s arithmetic operators assume as well.Unexpected Keyword Capitalization

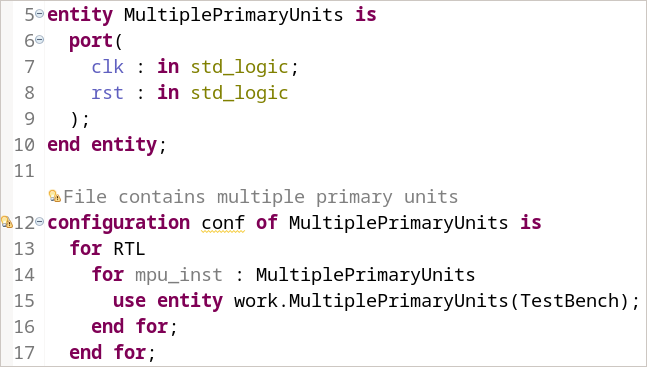

File Contains Multiple Primary Units

For clarity, you may want to have each primary unit described in its own file. A primary unit is one of the following

- entity

- configuration

- package

- package instantiation

- context

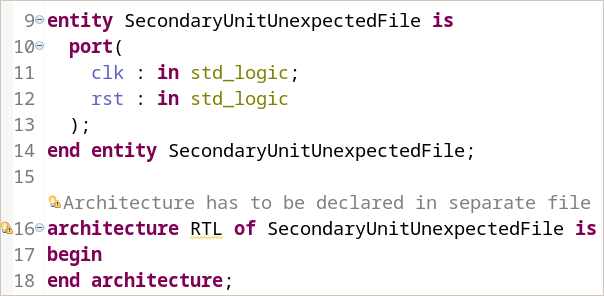

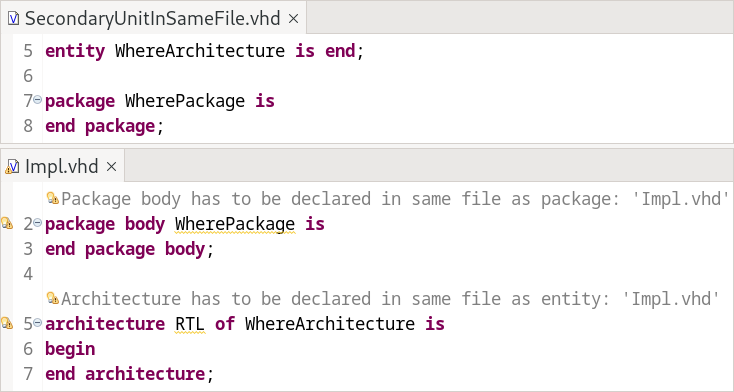

Secondary Unit in Unexpected File: Separate File from Primary Unit

Secondary Unit in Unexpected File: Same File as Primary Unit

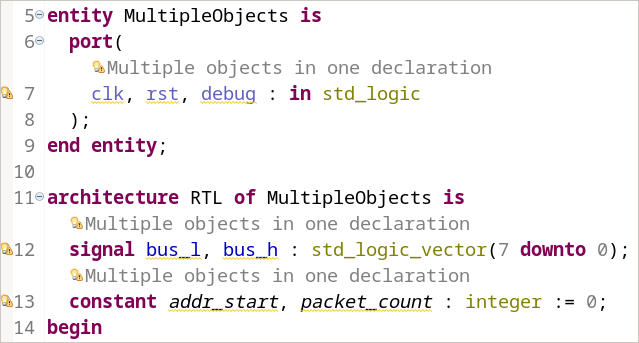

Multiple Objects in One Declaration

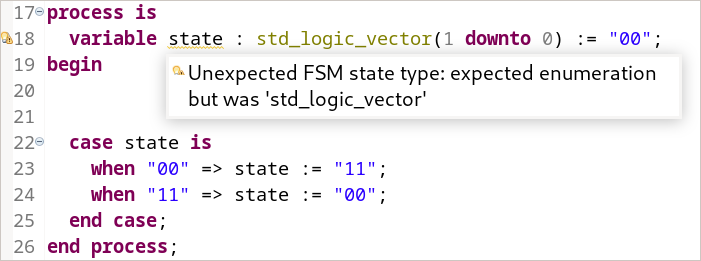

Unexpected FSM State Type

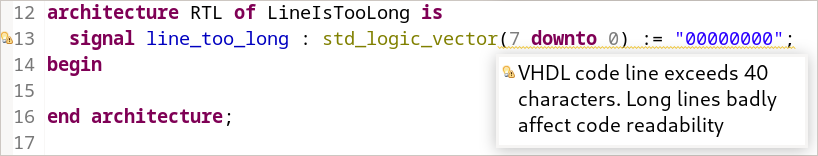

Line is Too Long

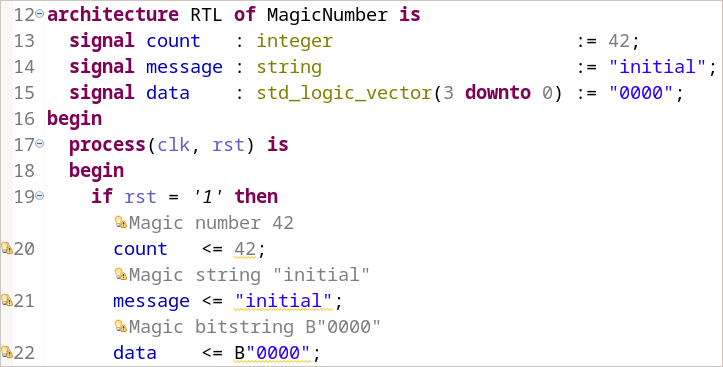

Magic Number, Bitstring, or String in Statement

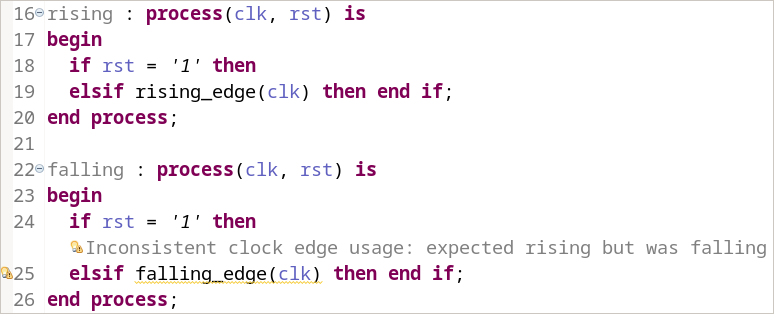

Inconsistent Clock Edge Usage

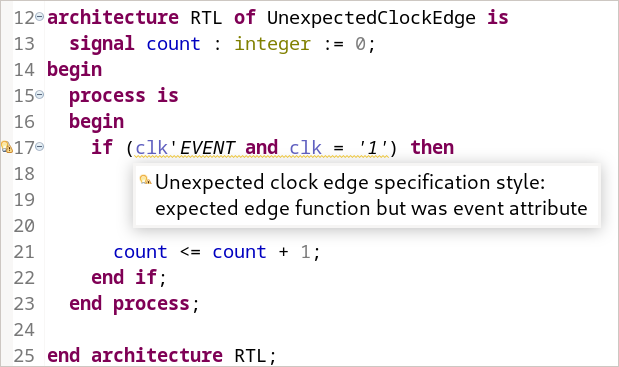

Unexpected Clock Edge Specification Style

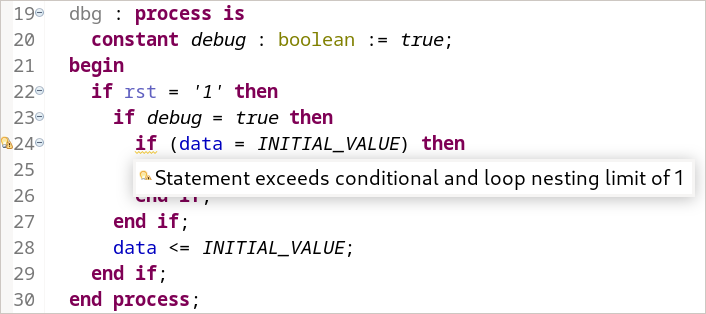

rising_edge and falling_edge) or event attributes (not clk'STABLE or clk'EVENT) and checking the clock signal level. We recommend using edge functions; however, whether you use the recommended style or not, you may find it beneficial to use a consistent style for readability. The preferred style can be configured.Deep Nesting of Conditional and Loop Statements

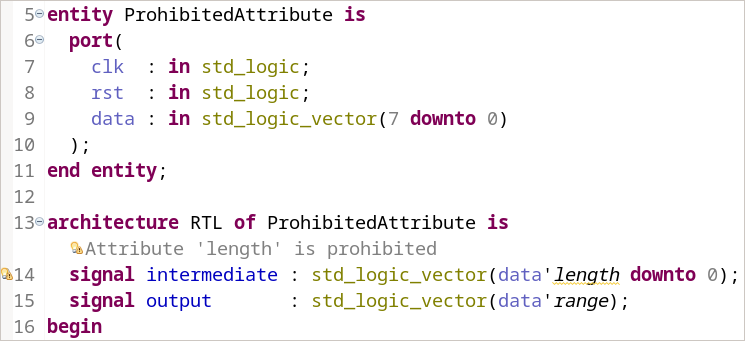

Prohibited Attribute

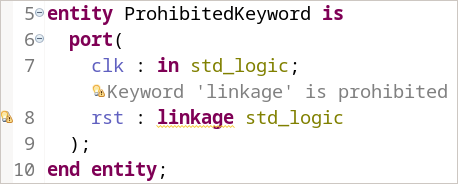

Prohibited Keyword or Operator

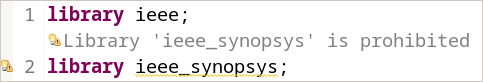

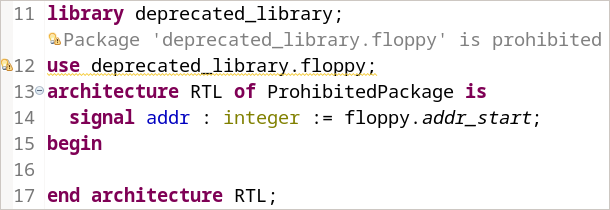

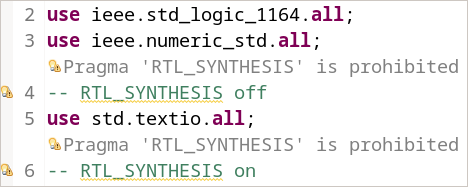

Prohibited Library

Prohibited Package

Prohibited Pragma

Verilog Linting Rules

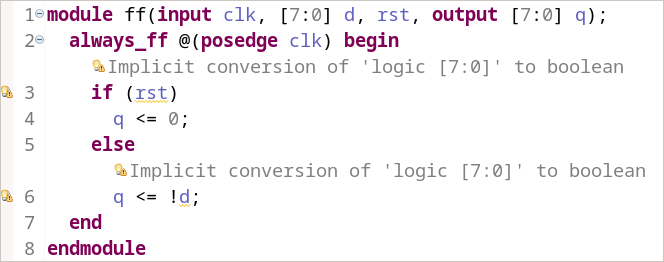

Implicit Vector to Boolean Conversion

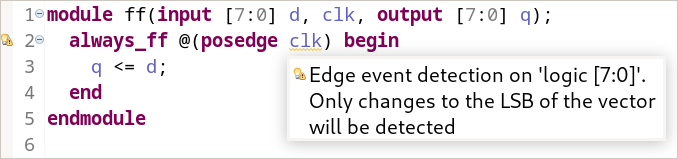

if statement is implicitly converted to a boolean by comparing it to 0. This is a valid code style, but it could also have happened accidentally. In this case, rst was accidentally assigned the type logic [7:0] instead of logic.Vector as Edge Event Expression

clk was accidentally declared with the type logic [7:0] instead of logic.Further New and Noteworthy

- Eclipse Added feedback to unsuccessful project imports

- Eclipse Improved highlighting for multiline strings and numbers

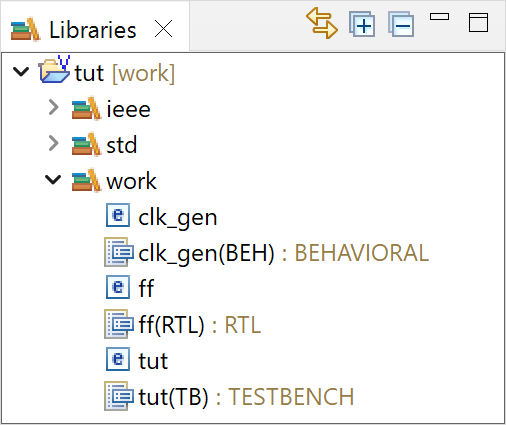

- Eclipse The Libraries View now shows whether code is RTL, behavioral, or a testbench

- Eclipse VHDL Allow configuring separate severities for RTL and non-RTL

- Verilog The Multiple Statements per Line linting rule’s severity is now configurable

Quality of Life

- Eclipse Removed viewport scrolling on format, greatly reducing interruptions caused by formatting

- Eclipse Improved consistency of menu items

- Eclipse Added keybindings to the Keys preference page allowing them to be rebound. This regards keybindings like Quick Outline (Ctrl+O) and Class Hierarchy (F4).

- Eclipse Verilog Enum members are grouped in the Class Hierarchy member pane

- Verilog Improved autocomplete performance by up to 50% for large projects

- Verilog Improved formatting when using includes and macro invocations

- Verilog Improved formatting inside of included files

- Verilog Improved Smart Indent when using interfaces as module ports

- Verilog The File Contains Multiple Design Units linting rule is only reported on the second design unit, greatly reducing noise

- VHDL Added missing squiggly line for the Process with Missing Sensitivity List and Wait Statements linting rule

Updates and Deprecations

- As announced in the previous releases, we have removed the support for the Graphics Configuration Language.

Bug Fixes

- Fixed formatting when zero width no-break spaces are used

- Eclipse Fixed prefix highlighting in autocomplete suggestions

- Eclipse Fixed editor <-> Hierarchy View cursor synchronization when duplicate entries are present

- Eclipse Fixed missing autocomplete when specific syntax errors are present

- Eclipse Fixed missing date for User-defined Autocomplete Templates using custom date formats

- Eclipse

Verilog Fixed missing autocomplete when typing

$with the autocomplete dialog open - Eclipse Verilog Fixed missing Block Diagram elements for complex assign statements

- Eclipse Verilog Fixed editor <-> Preprocessor View cursor synchronization when double or triple-click selecting

- Verilog Fixed the Add Declaration Quick Fix when used in if statements

- Verilog Fixed missing autocompletes following a function invocation

- Verilog Fixed missing autocompletes on large projects

- Verilog Fixed incorrect hover when using include files

- Verilog Allow interface classes in SystemVerilog packages

- Verilog Predefined SystemVerilog macros (e.g.,

`SV_COV_NOCOV) are recognized in unmapped files - VHDL Fixed false positive dead code error

- VHDL Fixed the label of entity and component autocomplete instantiations when the Formatting > Lowercase/Uppercase keywords preference is enabled

- VHDL Fixed missing autocomplete in empty package

- VHDL Fixed missing first character following a Type Conversion Autocomplete

Thank you for all the bug reports and for enabling Talkback. All your reports have helped us fix many issues that would otherwise have gone unnoticed.

Sigasi Studio 5.3.1 Point Release

On October 10, we released Sigasi Studio 5.3.1. This release contains the following changes and bug fixes:

- More resilient processing of

.projectfiles - Parameters in the

.prefsfiles are case-insensitive - Eclipse Fixed

Errors/Warningspage not opening when creating a builder

Sigasi Studio 5.3.2 Point Release

On October 23, we released Sigasi Studio 5.3.2. This release contains the following bug fix:

- Eclipse Fixed blank webviews on Windows

Sigasi Studio 5.3.3 Point Release

On November 28, we released Sigasi Studio 5.3.3. This release contains the following new feature:

- Eclipse Sigasi Studio on Windows starts without first showing a Microsoft Defender SmartScreen warning

System Requirements

- Sigasi Studio standalone is supported on:

- Windows 10 or Windows 11 64-bit

- RedHat Enterprise Linux RHEL 7.9 64-bit or newer, including RHEL 8 and 9

- Sigasi Studio depends on

libXss.sowhich can be obtained by installinglibXScrnSaver - Sigasi Studio depends on

webkit2gtk4.0which can be installed through your package manager of choice

- Sigasi Studio depends on

- More information on supported Linux OSes can be found on the Eclipse website

- Sigasi Studio as a plugin in your Eclipse installation:

- Eclipse IDE 2021-03 up to and including Eclipse IDE 2023-03

- Java JRE 11 or 17

- Sigasi Studio extension for VS Code:

- Windows 10 or Windows 11 64-bit

- RedHat Enterprise Linux RHEL 8 or 9 64-bit

- VS Code >= 1.77 and < 2.0

- Java JRE 11 or 17 (shipped with the extension)

- Veresta

- Windows 10 or Windows 11 64-bit

- RedHat Enterprise Linux RHEL 7.9 64-bit or newer, including RHEL 8 and 9

- Java JRE 11 or 17 (shipped with Veresta)

We recommend having at least 4GB of memory and about 1GB of free disk space available for Sigasi Studio.