For Verilog and SystemVerilog, Sigasi Studio 5.2 reintroduces rename, includes many new linting rules, and improves type checking by adding more contexts and rules.

As per usual, Veresta and our VS Code extension benefit from all of the changes not explicitly marked as Eclipse. VS Code specific changes can be examined in its changelog .

Smart Rename Refactoring

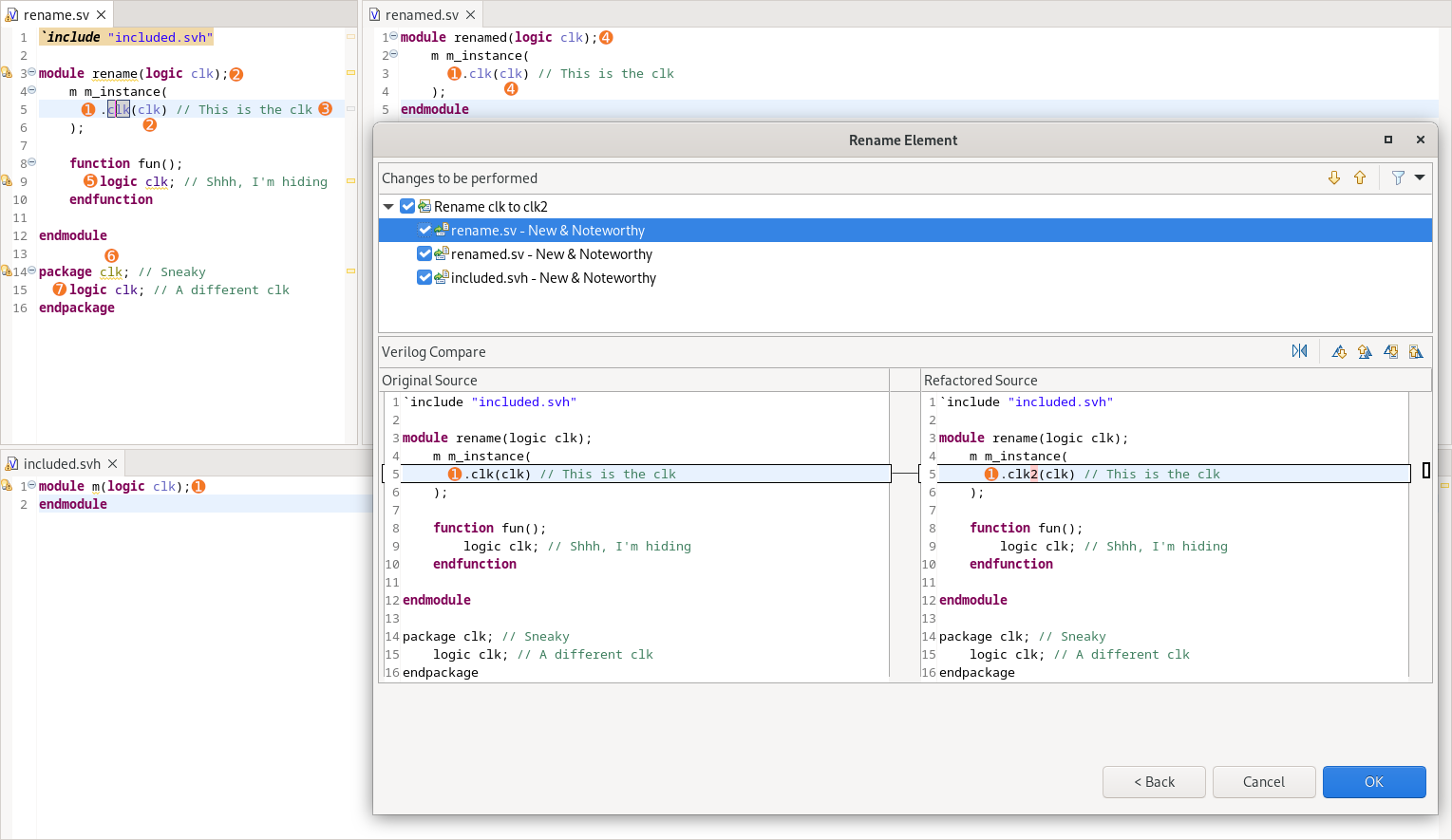

Naming things is hard and we often get it wrong the first time. Maybe we have ignored a naming convention or we think of a better term later in the design. Whatever the reason, we often want to rename variables, functions, methods, or other elements over the entire design. Enter Sigasi’s new and improved Rename Refactoring.

Sigasi understands hardware design and knows which identifiers link to which. It knows not to look in comments or inapplicable preprocessor code. By combining this information with our strong Find References feature, we can safely carry out a rename over thousands of files, without introducing syntactic or semantic errors.

The image above illustrates the difficulty of renaming. Clicking the image enlarges it.

Situations ➋-➐ are all locations where a clk identifier is used. However, in these cases, the clk identifier is actually referring to unrelated objects like ports in different modules, comments, local nets, or packages. Sigasi’s rename refactoring only modifies the relevant usages of clk in ➊ and leaves the others untouched.

New Verilog and SystemVerilog Linting Rules

Like all languages, Verilog and SystemVerilog contain some areas that are more error-prone or harder to reason about than others. For this release, we worked on a few of these: compliance with language specifications, unused declarations, copy-and-paste slip-ups, and confusion in design hierarchy.

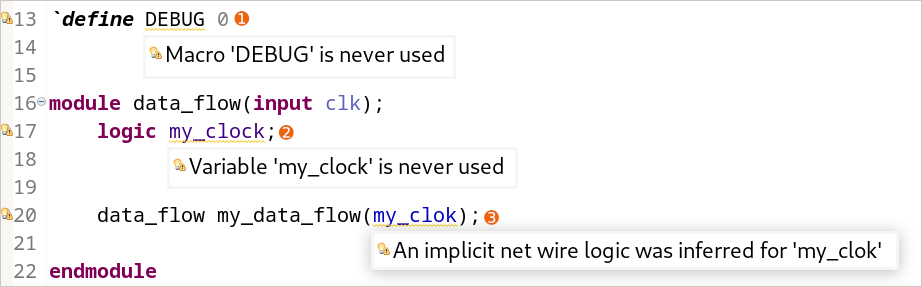

Unused Declarations

Even with helpful features like Occurrence Highlighting, Semantic Highlighting, and Find References, interruptions in the data flow can be hard to spot. Sometimes, we rename something manually, other times, we remove a declaration, and occasionally we might make a typo. In all of these cases, we can end up with unused (macro) declarations or references to declarations that no longer exist. For the latter, Verilog and SystemVerilog try to be helpful by creating an implicit net. However, this is seldom what the designer intended.

- We were debugging earlier but forgot to remove the now unused macro declaration

`DEBUG. Learn more - We create a separate net to connect to a module instance in ➌. Learn more

- The net defined in ➋ is used to connect up a module instantiation, but we made a typo. An implicit net is created for the misspelled

my_clok. Learn more

Compliance with Language Specification

The Verilog and SystemVerilog specification allow and forbid certain constructs. Some of the allowed constructs have dubious value. Sigasi helps write correct and unambiguous code, avoiding pitfalls and corner cases along the way.

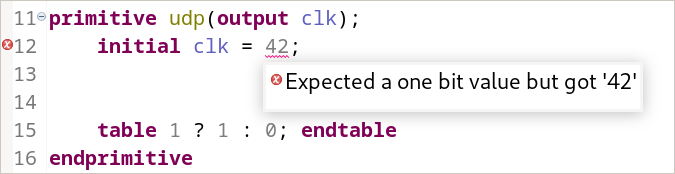

Multi-bit initial values for UDPs

The initial values for a user-defined primitive must all be single-bit. Assigning a multi-bit value is not allowed in Verilog and SystemVerilog.

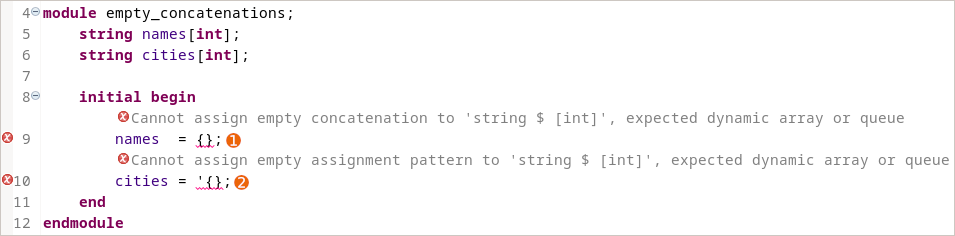

Empty Concatenation and Assignment Pattern

Only queues and dynamic arrays can be initialized by an empty concatenation or an empty assignment pattern.

- Initializing an associative array by using a concatenation is not allowed. Learn more

- An assignment pattern can only be used for initialization if the number of elements in the pattern matches the number of elements in the target. Learn more

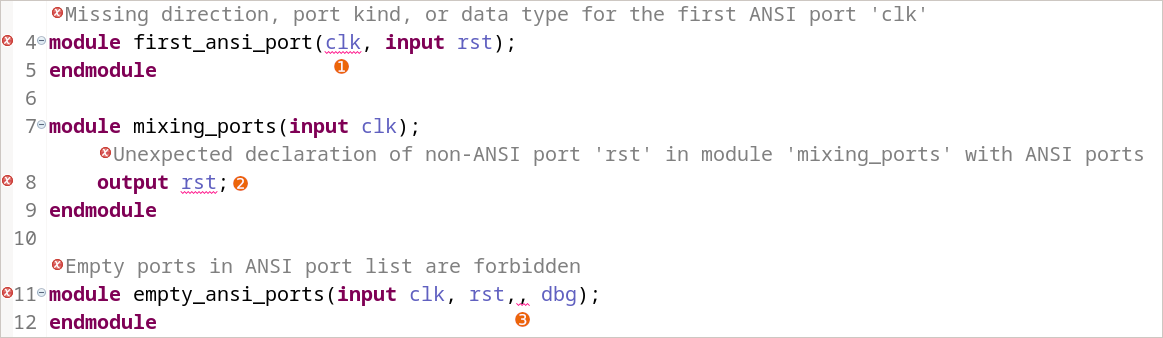

ANSI and Non-ANSI Ports

Modern ANSI port declarations were introduced in SystemVerilog. However, Verilog’s original non-ANSI port declarations are still supported for backward compatibility. This burdens the designer by doubling the number of rules they must remember when creating port declarations.

Learn moreANSI Ports

ANSI ports are fully declared in the port list, in contrast to non-ANSI where only the name is present in the list, but the port declaration must be completed in a separate statement.

- To use ANSI port declarations, the first port must declare its direction, port kind, or data type

- Mixing ANSI and non-ANSI styles is not allowed. Non-ANSI is only available for backward compatibility.

- Empty ports are only allowed (but discouraged) in non-ANSI port declarations. Learn more

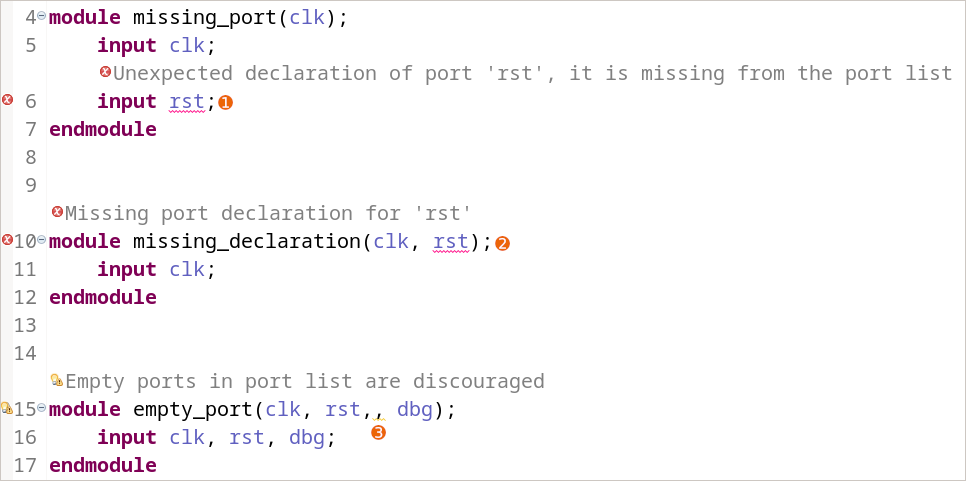

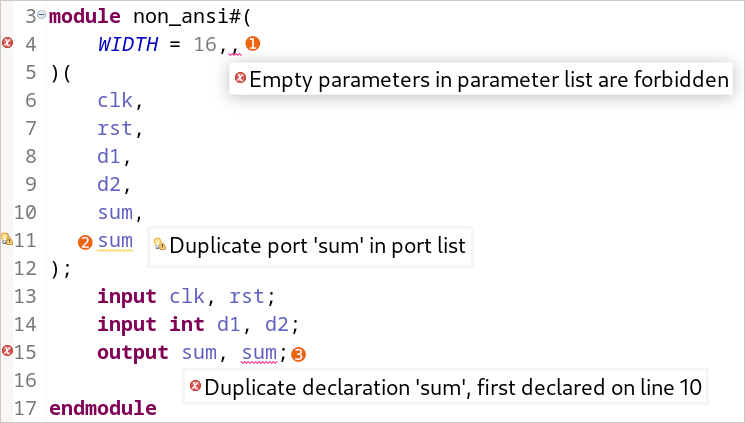

Non-ANSI Ports

Non-ANSI port declarations only define the name. The net and datatype are declared further on in the design unit.

- Ports can only be further declared if they are present in the port list

- Every defined port needs to be assigned a direction, data type, or net type

- Empty ports are allowed for non-ANSI, but they are most often a typo and do not reflect the intended design. Learn more

Hierarchical Confusion

Keeping an overview can be a challenge, but Sigasi keeps an eye on design and component hierarchies warning us when dubious patterns show up.

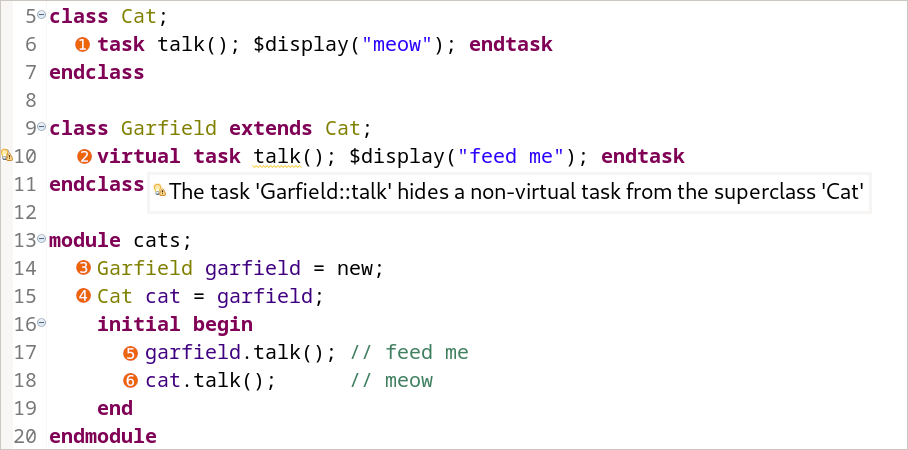

Hiding Superclass Methods

When we “override” a non-virtual method with a virtual one we are not actually overriding it, it is being hidden.

Looking at the example above, it would be fair to assume ➎ and ➏ would display the same value.

- A method called

talkis created on the superclassCatand outputsmeow - A method called

talkis created on the subclassGarfieldand outputsfeed me. This function hidesCat.talk()instead of overriding it. garfieldis of typeGarfieldgarfieldis upcasted toCat- As

garfieldis of typeGarfield,talk()outputsfeed meas expected - Surprisingly, the result is different from ➎ because ➋ was only hiding ➊, not overriding it.

meowis printed.

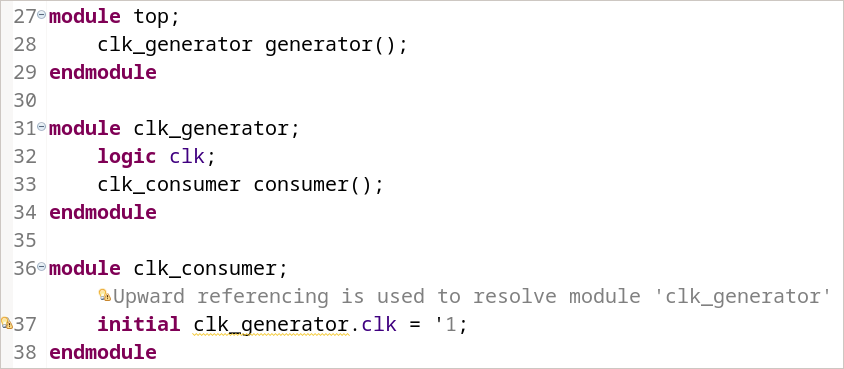

Hierarchical Upward References

Verilog and SystemVerilog allow referencing upwards in the component hierarchy. However, keeping the hierarchy in mind is a difficult task by itself, so referring to single lines within it affects the readability of the code, hurting debugability and maintainability.

clk_generator.clk is only available because clk_consumer was instantiated in clk_generator. When a different top level is selected, the clk that is referred to might change depending on who instantiates clk_consumer.

Copy and Pasting

All good designers are lazy. We copy-paste to fill in recurring structures. However, once in a while, a lapse of attention causes us to forget to edit this copied code. Other times - due to a lack of caffeine - we accidentally add a few seemingly harmless characters, which end up structurally changing the design.

- Being trigger-happy, we accidentally entered two commas. Verilog and SystemVerilog forbid empty parameters in parameter lists. Learn more

- The port on line 10 was copy-pasted but we forgot to rename the port. Learn more

- When fully declaring our ports, we forgot to rename the copy-pasted

sumonce more. Learn more

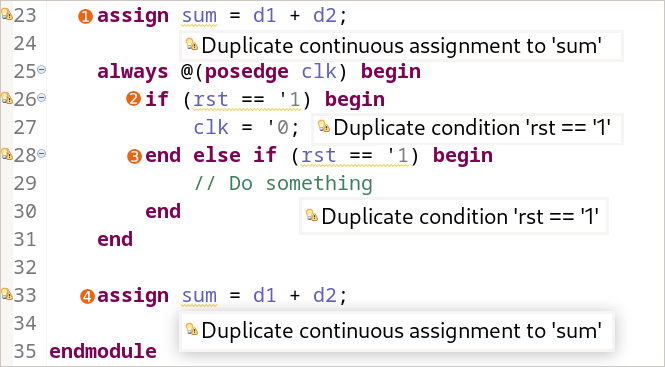

Continuing from the previous example:

d1andd2are added tosumusing a continuous assignment- We check whether

rstis high - Having copy-pasted ➋, we mistakenly check the same condition in the

else if. Learn more - Being in the flow of writing the logic of ➋ and ➌, we forgot we had already written this line in ➊. Learn more

Type Checking

As promised in previous releases, we have expanded our type checker with more rules and enabled it in more contexts. As we write code, sometimes we go on auto-pilot or rely on autocomplete too much. This is where - in hindsight - obvious mistakes can be made. Below are a few examples of the many hundreds of situations one can end up in. Sigasi catches these instantly, instead of hours or days after writing, shifting left and thereby drastically improving the design flow.

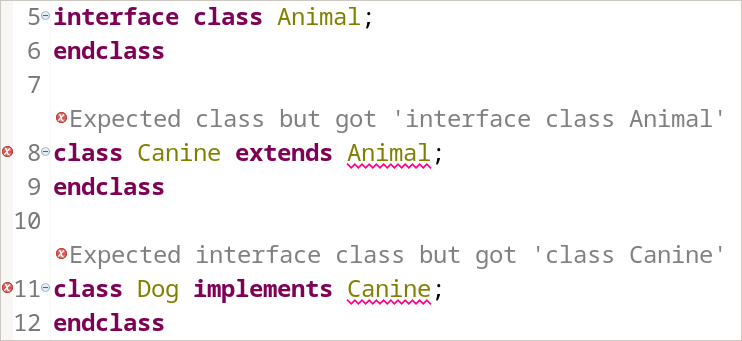

Class Extending

Classes can only be extended while interface classes can only be implemented.

Caninecannot extend the interface classAnimal, but it can implement itDogcannot implement the classCanine, but it can extend it

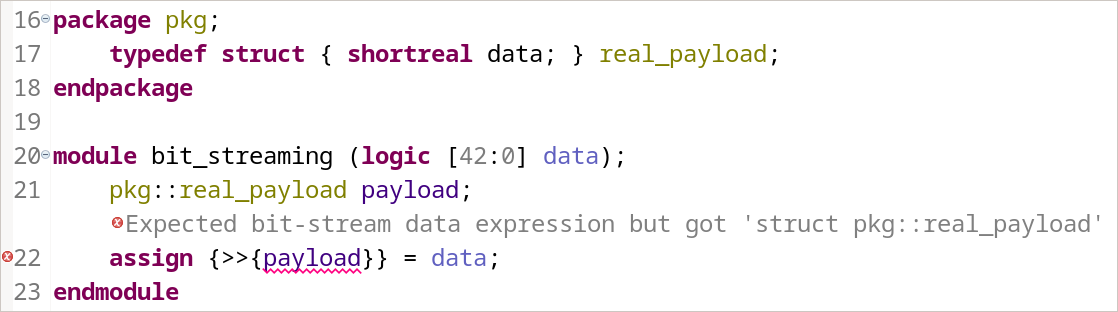

Streaming Operators

We are trying to unpack data into payload but data is not of a bit-stream type.

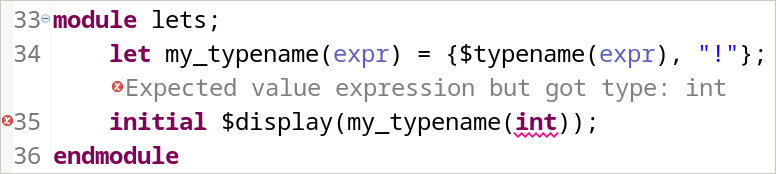

Let Declarations

Unlike their system function ($typename) counterpart, let declarations can only accept values, not types.

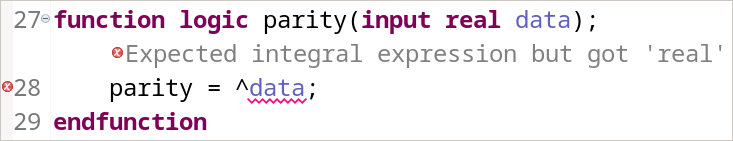

Unary Reduction Operator

Unary reduction operators perform a bitwise operation to produce a single-bit result. However, their operand must be of the integral type. shortreal is not integral, some valid types are int, logic, and bit.

Further New and Noteworthy Changes

- Brought consistent styling to capitalization of menus and commands

- The autocomplete description dialog now shows the same information as hovers

- Eclipse The performance of Export Documentation was improved further

- Verilog Increased incremental preprocessing speed by up to 300% on large projects

- Verilog Added hovers for range enum members e.g.

B4intypedef enum {B[5:3]} E - Verilog Adding VUnit support now also links in the required

vunit_defines.sh - Verilog The local parameter cannot be overridden linting rule was improved and detects more cases

- Verilog Added a description for

$unitin our information views, e.g., outline, hover, and autocomplete - Verilog Improved accuracy of Semantic Highlighting

- Verilog Added navigation for

exportstatements - Verilog Added error when trying to include a folder, e.g.,

`include "folder/" - Verilog Added navigation and Occurrence Highlighting for

.*port connections - Verilog Added support for empty assignment patterns, e.g.,

logic queue[$] = '{} - Verilog Preprocessor tool compatibility linting rules are now configurable

Quality of Life

- Improved readability of very long linting messages

- The outline no longer repositions the

ParametersandPortswhenSort alphabeticallyis enabled - The autocomplete description dialog now wraps lines instead of cutting them off

- Eclipse The Open Design Unit Dialog now highlights matched characters and is more keyboard friendly

- Eclipse

VHDL Typing backslash (

\) with an identifier selected now forms an extended identifier, e.g.,\identifier\ - VHDL The incomplete sensitivity list Quick Fix adds the whole array instead of every array element separately

- Verilog Added autocomplete templates for

structandunion - Verilog The default name for the autocomplete template of

modules was changed to the filename - Verilog Corrected the Smart Indentation following a

typedefininterfaces

Updates and Deprecations

- The Graphics Configuration is deprecated and will be removed in Sigasi 5.3

- JustJ - the JRE shipped with Sigasi Studio - has been updated to 17.0.7

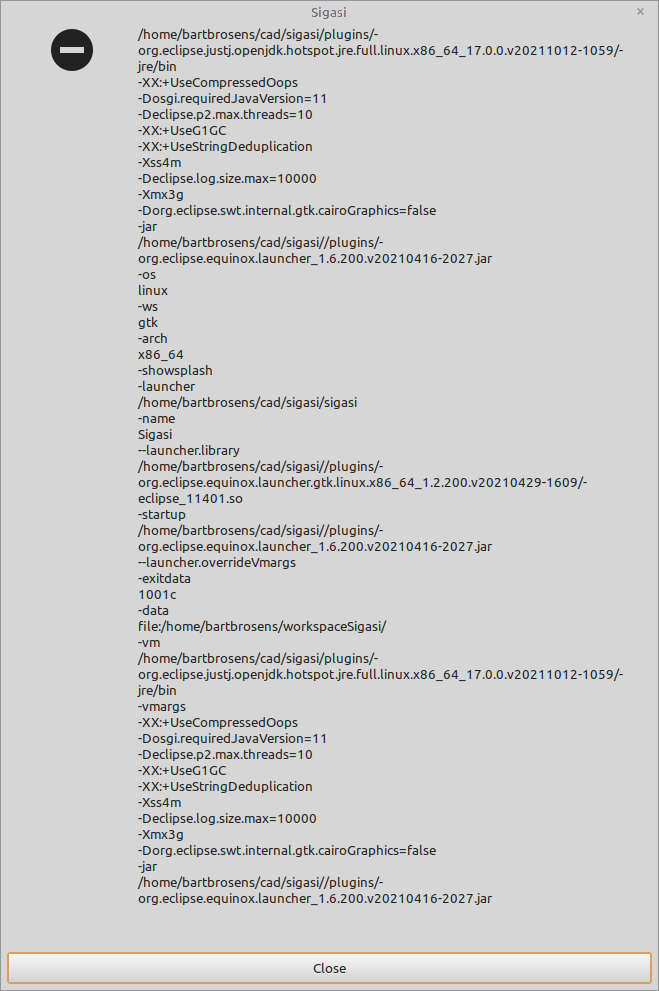

Note that an error dialog might be shown upon restarting Sigasi Studio after updating because the JRE was updated. Closing the dialog, and restarting Sigasi Studio manually will fix the issue.

Talkback Changes

Talkback messages include information about

- the currently checked-out and available license types

- the currently used product, e.g., Sigasi Studio Eclipse or Sigasi Studio for VS Code

Bug Fixes

- The

Unresolved declarationlinting rule uses correct capitalization in its message - Improved cursor handling during autocomplete

- Redundant license servers are taken into account

- Fixed performance regression in the Quick Outline

- Eclipse No more temporary license check-outs are done on boot

- Eclipse The Errors/Warnings preference page is populated even if the checked-out license is invalid

- Eclipse Fixed incorrect navigation from the Hierarchy View to include files

- Eclipse Verilog After saving a file with the Class Hierarchy open, the focus remains on the editor

- VHDL The

Add missing port associationsQuick Fix also succeeds if the port map contains a capitalization mismatch - VHDL Case statement linting supports port selections

- VHDL Fixed highlighting and double-click behavior for character pairs, e.g., quotes, parenthesis and backslashes

- VHDL Fixed occasional blank autocomplete suggestions

- VHDL Fixed false positive error on local parameters in protected types

- Verilog The module instantiation autocomplete inserts an unconnected port when necessary

- Verilog The

randcasestatement no longer triggers the same linting as the regularcasestatement - Verilog Keyword proposals take the configured language level into account

- Verilog Fixed navigation from the outline to the editor when dealing with included files

- Verilog Fixed occasional missing navigation in the Preprocessor View

- Verilog Fixed occurrence highlighting near the usage of double backticks (

``) - Verilog Fixed missing markers for the Check line length linting rule

- Verilog Fixed missing navigation targets for wildcard imports, e.g.,

import p::* - Verilog Fixed the surrounding of selected text by character pairs by typing a double quote, parenthesis, or other

- Verilog Fixed navigation for duplicate non-ANSI subprogram arguments

- Verilog Fixed false positive error on calls to

newwhen an invalid function callednewis present - Verilog Fixed false positive error when importing from packages defined in unmapped files

- Verilog Fixed false positive

Net data type must be integralerror forinterconnects - Verilog Fixed false positive Consider using named port connections warning when named connections cannot be used

Thank you for all the bug reports and for enabling Talkback. All your reports have helped us fix many issues that would otherwise have gone unnoticed.

Sigasi Studio 5.2.1 Point Release

On June 30, we released Sigasi Studio 5.2.1. This release contains the following changes and bug fixes:

- Fixed empty outline after startup

- Eclipse Corrected paths in compile order CSV Export

- Eclipse

Right-click > Show Inis available for Graphical Views - Verilog Fixed startup slowdown when using the cache

Sigasi Studio 5.2.2 Point Release

On August 9, we released Sigasi Studio 5.2.2. This release contains the following changes and bug fixes:

- Learn how to deal with files containing a pound sign (

#) - Eclipse Updated to Eclipse 2023-03

- Eclipse Fixed bad interaction with

webkit-gtk-4.0

System Requirements

- Sigasi Studio standalone is supported on:

- Windows 10 or Windows 11 64-bit

- RedHat Enterprise Linux RHEL 7.9 64-bit or newer, including RHEL 8 and 9

- Sigasi Studio depends on

libXss.sowhich can be obtained by installinglibXScrnSaver - Sigasi Studio depends on

webkit2gtk4.0which can be installed through your package manager of choice

- Sigasi Studio depends on

- More information on supported Linux OSes can be found on the Eclipse website

- Sigasi Studio as a plugin in your Eclipse installation:

- Eclipse IDE 2021-03 up to and including Eclipse IDE 2023-03

- Java JRE 11 or 17

- Sigasi Studio extension for VS Code:

- Windows 10 or Windows 11 64-bit

- RedHat Enterprise Linux RHEL 8 or 9 64-bit

- VS Code >= 1.77 and < 2.0

- Java JRE 11 or 17 (shipped with the extension)

- Veresta

- Windows 10 or Windows 11 64-bit

- RedHat Enterprise Linux RHEL 7.9 64-bit or newer, including RHEL 8 and 9

- Java JRE 11 or 17 (shipped with Veresta)

We recommend having at least 4GB of memory and about 1GB of free disk space available for Sigasi Studio.

Feedback

We welcome your feedback through the usual channels or the comments below. Note that comments on this page are cleared after each official release.