The Sigasi Studio 5.1 release focuses on productivity and verification for Verilog and SystemVerilog. Building on the new foundations laid in the Sigasi Studio 5.0 release, we added a type checker, many new linting rules, improved our performance and memory usage, and further refined our information-rich hovers and views. These improvements increase the designer’s efficiency and liberate them from many intricacies of Verilog and SystemVerilog.

As per usual, Veresta and our VS Code extension benefit from all of the changes not explicitly marked as Eclipse.

New Verilog and SystemVerilog Linting Rules

Precision, correctness, and insight are of paramount value when creating your design, all the more when it quickly becomes more and more complicated. Trying to balance project setup, expansive languages like Verilog and SystemVerilog, legacy code, and external IP can be daunting. Here is where our linting rules shine, alleviating these difficulties and allowing you to focus on the design.

Problems ranging from implicit casting to missing code or ambiguous references are a thing of the past. No need to wait for your linter or synthesis tool to wade through a sea of errors and warnings. Sigasi 5.1 helps you catch problems early, instantly detecting them at every keystroke.

Type Checker

Verilog and SystemVerilog’s type compatibility rules can be obscure, especially considering implicit type conversion and complex expression evaluation rules. To help you avoid any pitfalls, the type checker ensures that assigning ports, nets, or variables is done safely. You can find a preview of the type checker’s manyfold capabilities below.

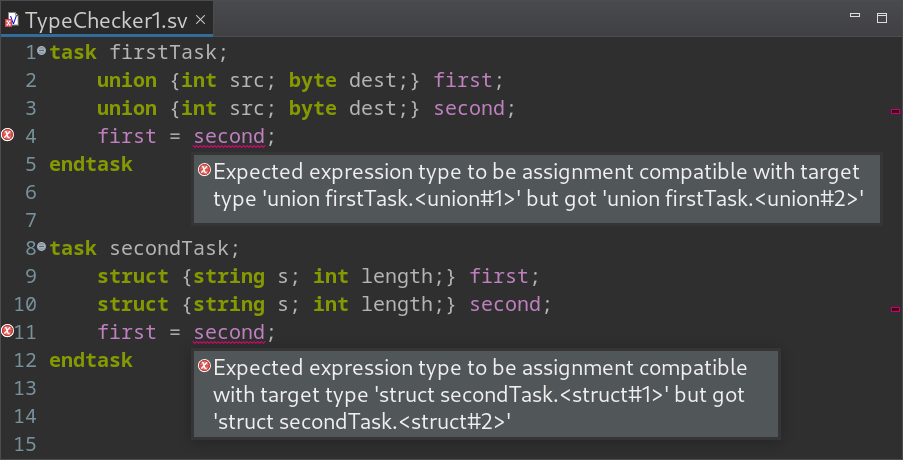

Unions and Structs

Even though these two unions and structs have the same signature, they implicitly define two anonymous types; they are thus not assignment compatible.

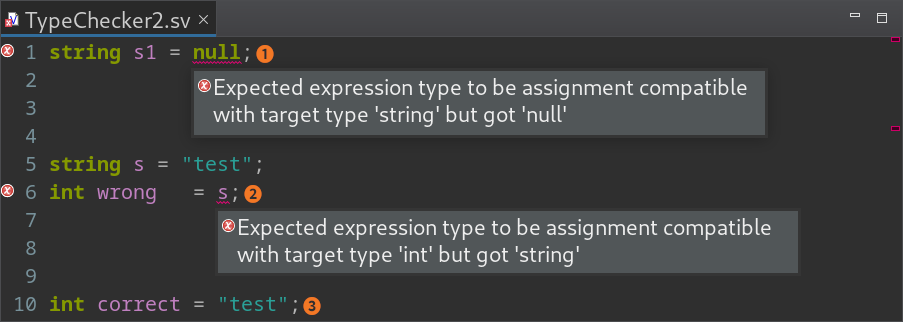

String Variables and Literals

string variables and literals behave differently.

nullcannot be assigned tostringvariables.- String variables cannot be assigned to

intvariables because they are dynamically sized ordered collections of characters that are not assignment compatible toint. - However, string literals can be used to initialize

ints as they are treated asunsigned integerconstants.

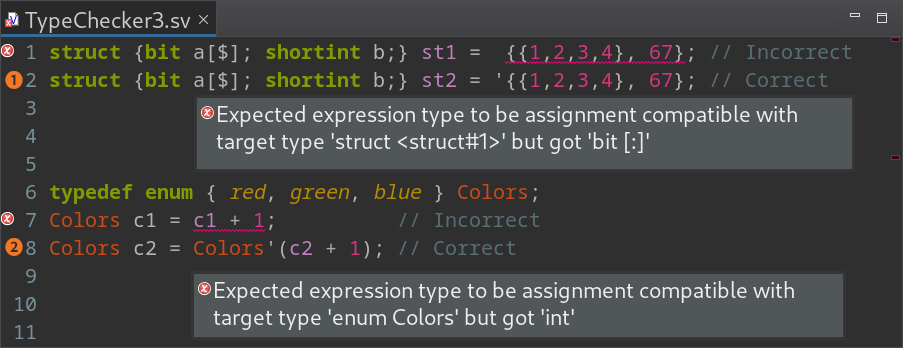

Syntax Confusion and Implicit Casting

- The concatenation and assignment pattern syntax confusingly resemble each other a lot.

- It is not always clear what assignments will be implicitly cast.

enums are implicitly cast toints, but not the other way around.

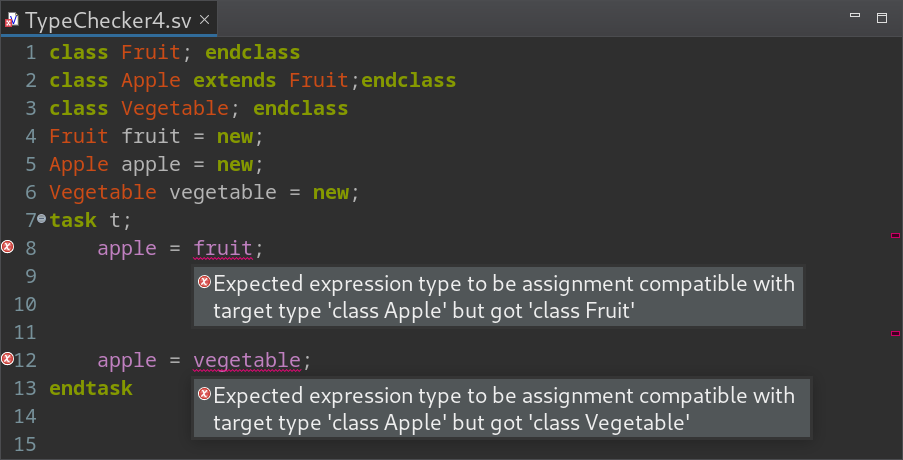

Classes

Subclasses can be assigned to superclasses, but not vice-versa. Every Apple is a fruit, but not every Fruit is an Apple. Similarly, classes unrelated to one another (Fruit and Vegetable) are not assignment compatible.

Sigasi Studio also helps with the other type compatibility rules defined in SystemVerilog. For example:

- The type of the actual value should be equivalent to the formal

refport type - Argument types should match when comparing overridden or extern method signatures

If you like what we presented here, you will be happy to hear that we will expand further upon our type checker release by release.

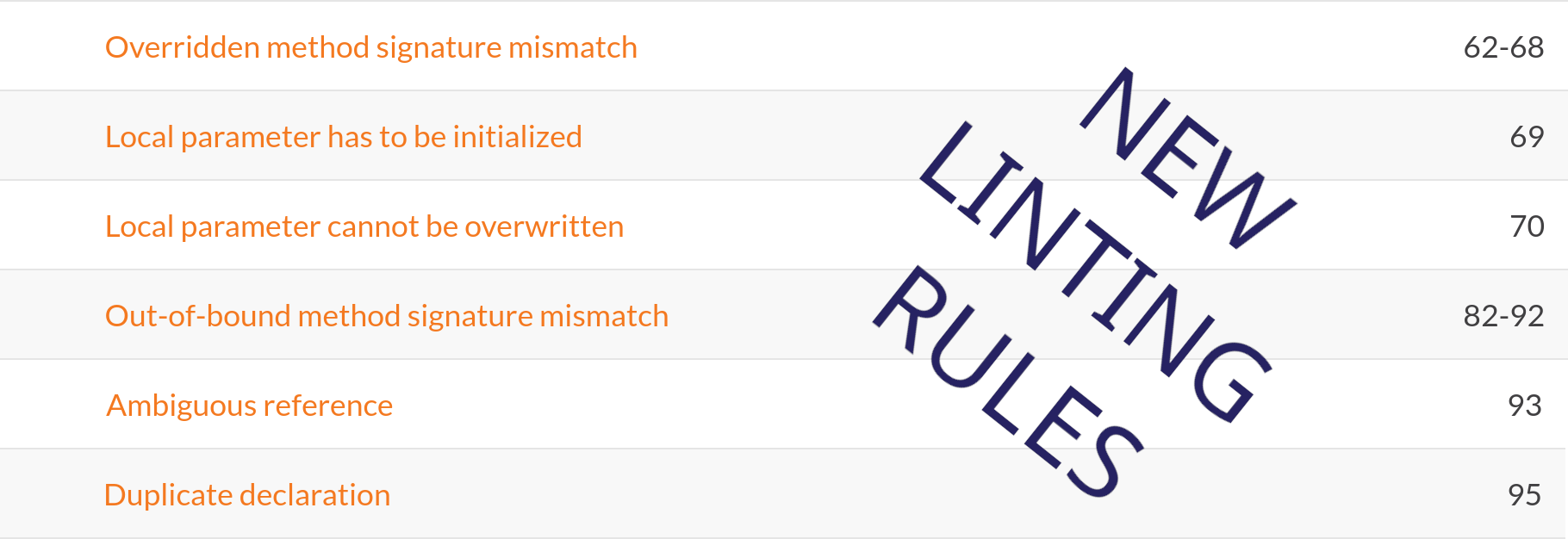

New Linting Rules

Small oversights, ambiguity, and keeping track of a language’s many rules and restrictions are struggles you deal with daily. Instead of waiting for elaboration or synthesis to spot in hindsight obvious mistakes, Sigasi 5.1 instantly points these out.

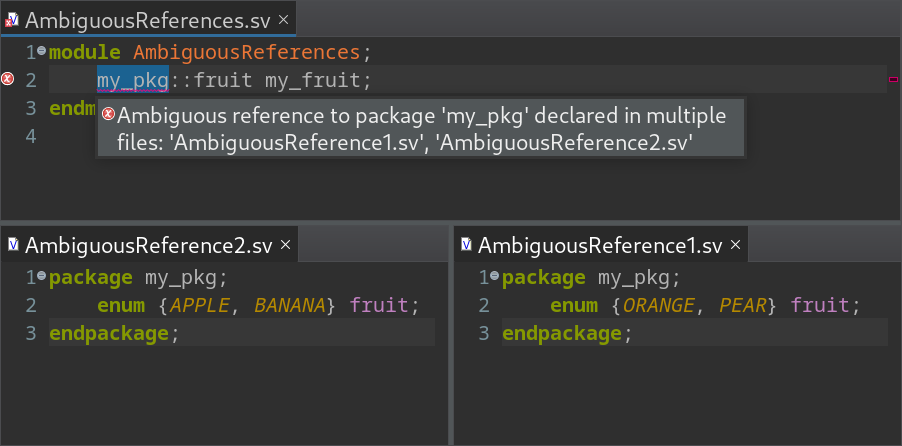

Ambiguous Reference

Inaccuracies in the project setup can result in multiple declarations with the same name. Sigasi flags references to these names as ambiguous.

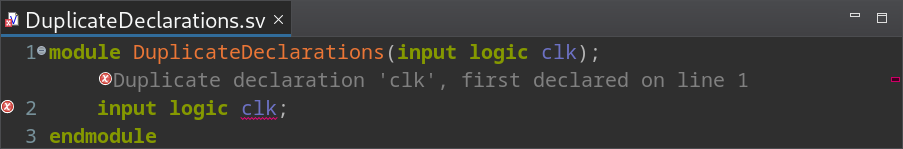

Learn moreDuplicate Declaration

Similarly, multiple declarations with the same name within the same file - or scope - will be flagged as duplicates.

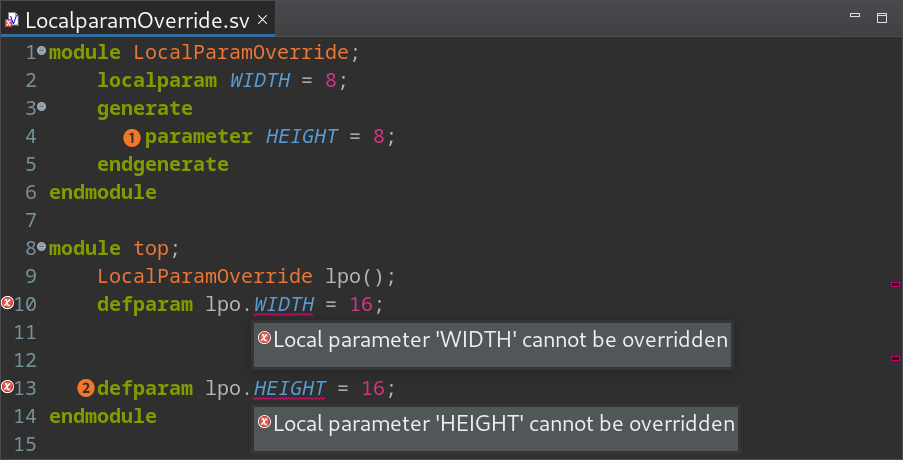

Learn moreLocalparam Override

Verilog and SystemVerilog forbid localparams from being overridden. This is a simple enough restriction, but you also have to be aware of parameters that are implicit localparams.

HEIGHTis defined as a parameter but it implicitly is alocalparam.- Overriding

HEIGHTis not allowed as it is actually alocalparam.

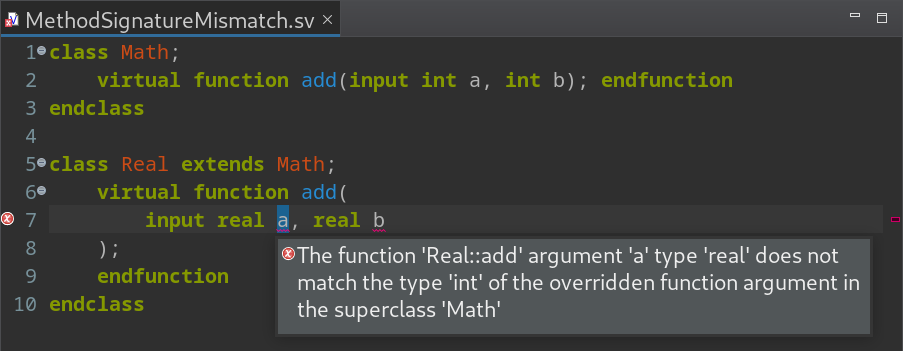

Overridden Method Signature Mismatch

In SystemVerilog, the types, names, qualifiers, and directions of the arguments of virtual method overrides must match their prototype. There are even more checks on the return type and the assigned default values of arguments.

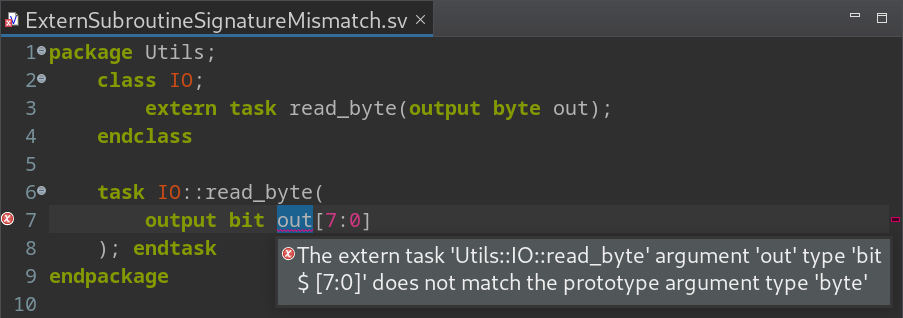

Extern Subroutine Signature Mismatch

Similarly, method declarations must match their prototypes exactly … though there are some exceptions for default arguments.

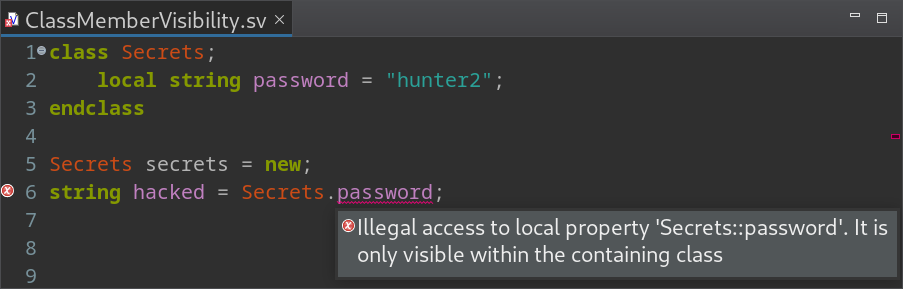

Learn moreClass Member Visibility

When working with classes, it can be hard to keep track of what properties, methods, classes … you have access to. Sigasi flags illegal accesses such that you can easily correct the access modifier.

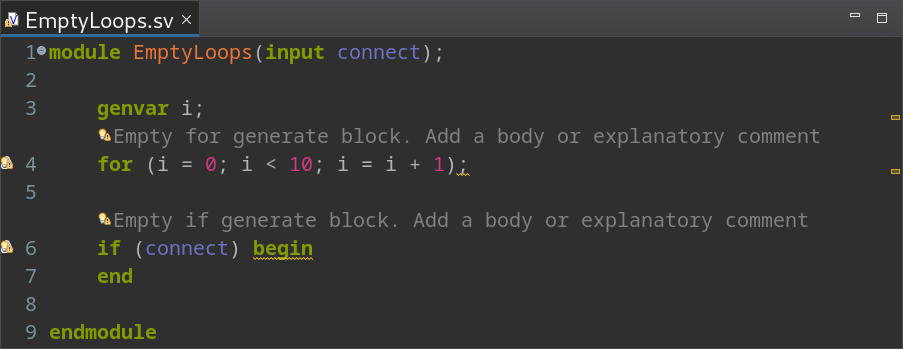

Learn moreEmpty Loops and Conditionals

Empty loop bodies are most likely unintended. They consume compute cycles without any useful contribution to the functionality of your design. Empty conditional branches can cause unwanted latches to be generated. They can also result from a typo or indicate some missing cases.

Learn moreImproved Performance and Reduced Memory Usage

Since we are obsessed with performance, we kept ourselves busy for Sigasi 5.1, further improving the interactive feedback of your favorite IDE. After all, to enable productivity, a snappy experience is of the utmost importance.

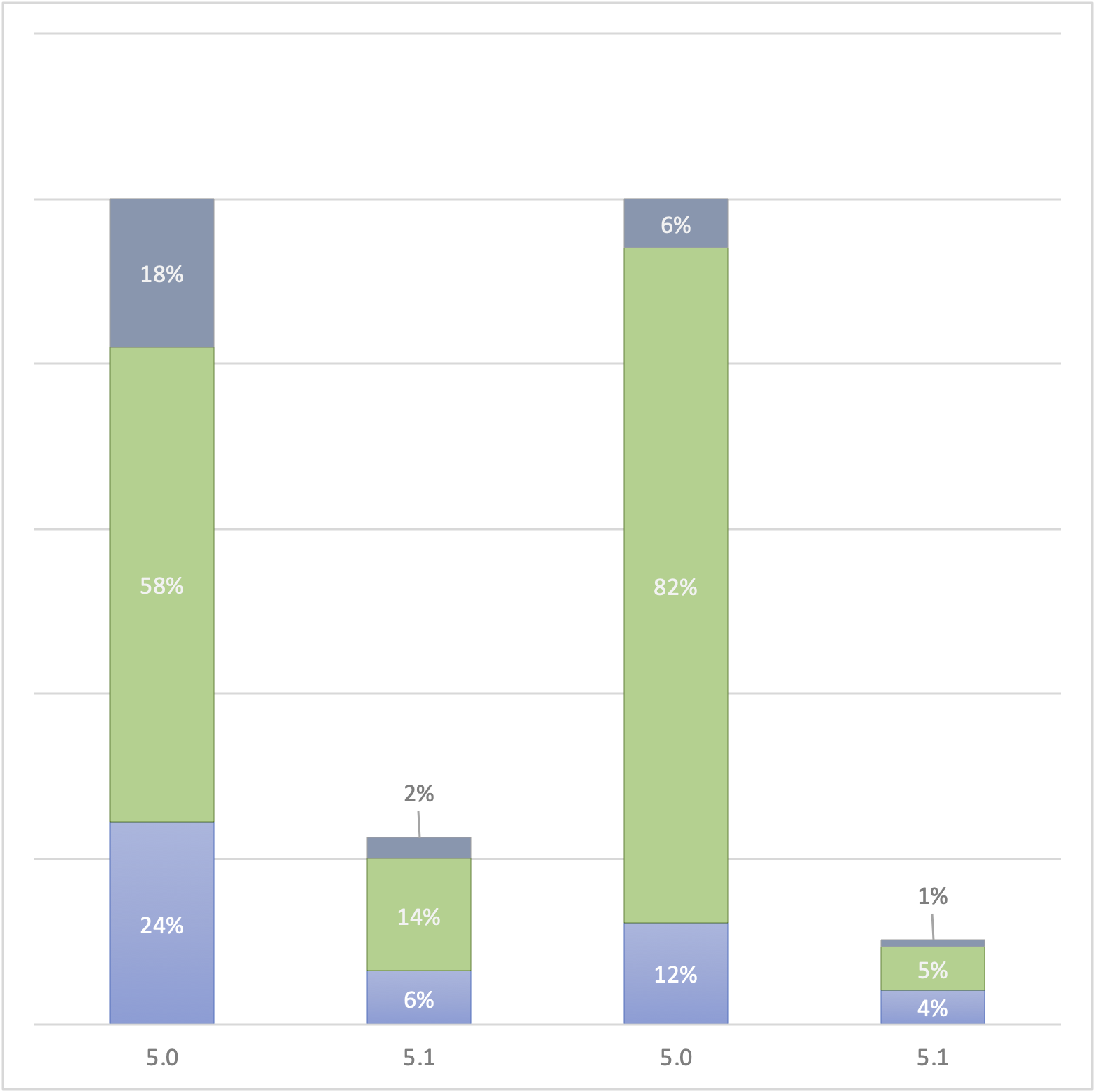

For that purpose, we worked on different parts of the analysis pipeline and carefully assessed various usage patterns and scenarios. For the use cases that we focused on for this release, we managed to reduce the runtime on average by 80% compared to Sigasi 5.0. For some parts of the analysis engine, an improvement of up to 95% could be achieved.

The chart shows the relative timing measurements of two different, sizable projects as a comparison between Sigasi 5.0 and 5.1. Starting from a baseline of 100%, we see that the same operation takes only a fraction of the time in Sigasi 5.1.

Besides performance, we also worked towards reduced memory consumption of Sigasi. Especially in large projects, you will find that Sigasi 5.1 requires, on average, 30% less memory depending on the structure of your project.

Information-rich Hovers and Views

To keep you in the flow, we introduced rich and accurate labels and hovers in Sigasi Studio 5.0. Context switches to look up small details are unnecessary as you are presented with many details at a glance through our information-rich hovers and views. In this release, we have refined our existing labels, added more information, and fixed a few incorrect labels across the board - be it in hovers, the Outline View, or the Hierarchy View - in VHDL, Verilog, or SystemVerilog.

- VHDL Improved labels in the Hierarchy View to show the configured name if a design unit binding indication is used, e.g.,

for all : test use entity work.low(RTL); - VHDL The Hierarchy View now shows the

generatebody label - Verilog Added hovers for built-in functions

- Verilog Added type information to

genvarlabels - Verilog Added

pureandvirtualinformation tointerface class’s function labels - Verilog Improved the labels within a

randsequence - Verilog Improved the labels of named assertions

- Verilog Improved the labels of (un)packed arrays

- Verilog Improved the labels of anonymous types

- Verilog Fixed the label of references to ports of concatenated packed arrays, e.g.,

ainmodule m(.a({b, c}))

GPG Signing

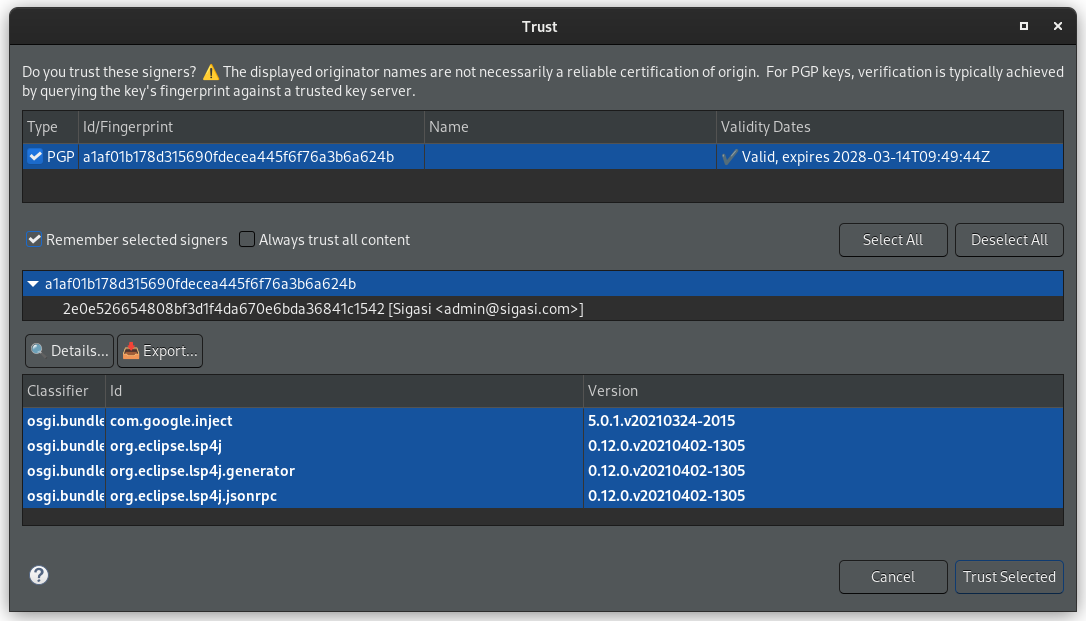

Eclipse 4.26 (2022-12) added GPG certificate checking capabilities. When you install new plugins, you will be prompted to trust any not-yet-trusted GPG keys or unsigned artifacts. Because Sigasi artifacts are correctly signed using GPG, you can expect to see the following screen the first time you install or update Sigasi in an Eclipse >= 4.26.

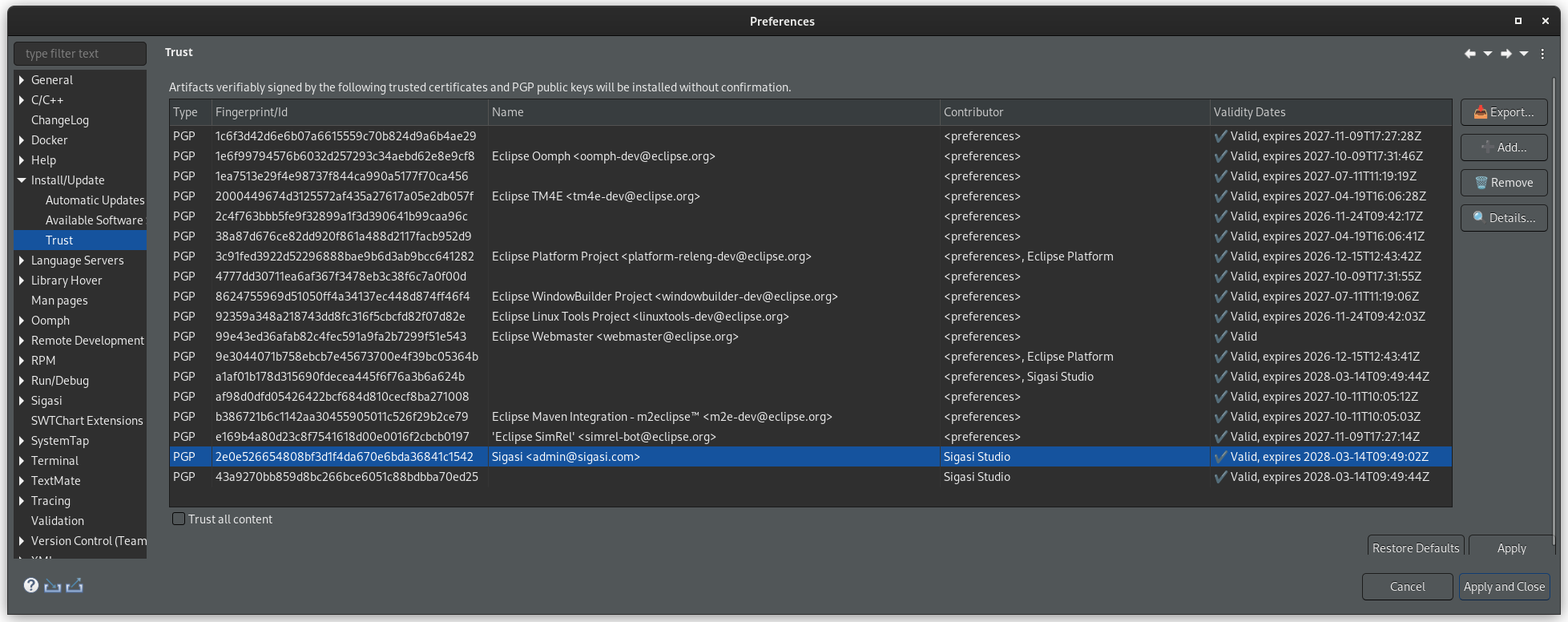

Previously trusted keys can be inspected by going to Window > Preferences > Install/Update > Trust.

You can refer to this page for all information regarding GPG at Sigasi.

Further New and Noteworthy Changes

- Eclipse The upper limit for the amount of autocomplete proposals has been increased. In practice, this means that important proposals will always be included.

- Eclipse Generated documentation now shows an empty cell instead of

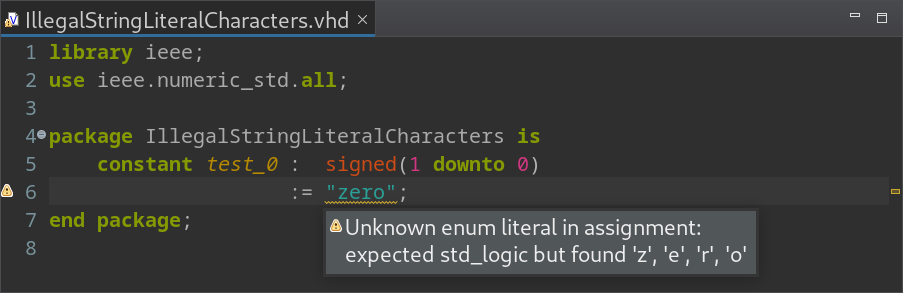

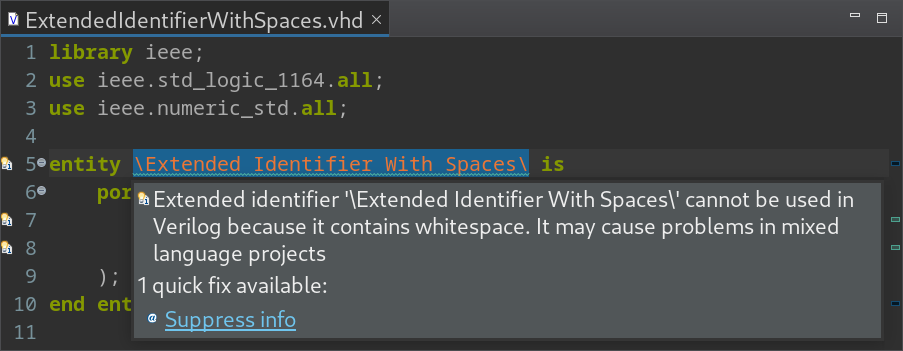

unspecifiedwhen no default is specified - VHDL Added a linting rule to check that the characters in a string literal are legal

- VHDL Added a linting rule to check whether spaces are used in extended identifiers referable from Verilog and SystemVerilog as these cannot be referenced in those languages

- VHDL Added formatting for

forceandreleaseassignments - Verilog Improved preprocessing performance

- Verilog Added navigation to identifiers in

showcancelled,noshowcancelled,pulsestyle_onevent,pulsestyle_ondetect - Verilog Added an error when a

genvaris referenced outside the loop’s body

Quality of Life

- Improved priorities for keywords in autocomplete. Relevant keywords are now listed higher up.

- Removed syntax highlighting of keywords in extended identifiers, e.g.,

\extended id\or\extended$id - Eclipse The Problems View

Sort by Locationnow sorts by line number - Eclipse The VUnit installation path is now updated when you set your

pythonpath, even if there are no VUnit projects open - Eclipse The descriptions of the options in the Documentation Generation Wizard no longer change when you enable or disable them

- Eclipse Added a description to the Export Marker wizard

- Eclipse Added missing keybind for Quick Outline

- Eclipse Added queueing for diagram exports. If an export is already in the works, it will not be canceled.

- Eclipse Improved caret positioning after formatting such that it jumps around only when strictly necessary

- Eclipse Improved icons for

typedefandnettypein the Outline View - Eclipse Fixed autocomplete proposals to highlight the matching prefix characters in bold

- Eclipse Removed hovers that are empty for whatever reason

- Eclipse Removed Suppress Warning Quick Fix when the problem is already suppressed

- VHDL Improved wording in many of our error messages

- VHDL Eclipse Fixed extra whitespace in the Add sensitivity list Quick Fix

- Verilog The variable being declared is no longer shown as autocomplete proposal when you are initializing it

- Verilog Eclipse Holding Ctrl while autocompleting a macro parameter now only replaces the parameter under the cursor instead of the rest of the line

Bug Fixes

- The include directive autocomplete now shows proposals for files that need encoding, e.g., when they contain a space or non-ASCII characters

- Eclipse Fixed the Capture Heap Dump command

- Eclipse Fixed a deadlock when closing a tab while the autocomplete window is open

- Eclipse Fixed backspace inadvertently deleting multiple whitespace characters

- Eclipse Fixed mac-style newlines (

\r) breaking the Documentation Export - Eclipse Fixed unintended character substitution in the CSV Marker Export

- Eclipse Fixed empty autocomplete when it is called very early during startup

- Eclipse Fixed an occasional hang during navigation

- Eclipse Fixed occasional incorrect navigation on Ctrl+Click

- VHDL Added linting when assigning

"-"to a vector - VHDL Added support for the standard library’s

readfunction to VHDL 2008 and 2019 - VHDL Fixed false positive warning when using

unsigned'()as the default value for aconstant - VHDL Fixed indentation of comments during formatting when they are placed after instantiations

- VHDL Fixed false positive

variable is never writtenwhen using non-shared protected type variables - VHDL

Eclipse The

Increase VHDL versionQuick Fix will now only update the file if the project already has the correct version - Verilog Include directives that start with a

/now correctly resolve relative to the project root - Verilog Added instance names to the Hierarchy View

- Verilog Added navigation from implicit port connections (e.g.,

.clk) to both the port/net and the actual - Verilog Fixed highlighting for multiline string literals

- Verilog Fixed positioning of errors with unusual define directives

- Verilog Fixed type inference for real literals

- Verilog Fixed highlighting of parameters in multi declarations, e.g.,

parameter WIDTH, SIZE - Verilog Fixed navigation of functions when a target is available in the enclosing class and the parent class

- Verilog Removed false positive override annotation in the Class Hierarchy View

- Verilog Removed duplicate

Open Declarationlinks when a file is included multiple times - Verilog Eclipse All inherited members in the Class Hierarchy View are now colored consistently

- Verilog Eclipse Fixed links to parent classes in generated documentation

- Verilog

Eclipse Fixed empty Class Hierarchy View when opening it on a class that has a

taskandfunctionwith the same name - Verilog

Eclipse Removed empty blocks in the Block Diagram for empty

forloops

Thank you for all the bug reports and for enabling Talkback. All your reports have helped us fix many issues that would otherwise go unnoticed.

Updates

- Eclipse Updated to Chromium 95 for rendering graphics and the Documentation View. This increases the stability and performance of these views

System Requirements

- Sigasi Studio standalone is supported on:

- Windows: Windows 10 or Windows 11 64-bit

- Linux: RedHat Enterprise Linux RHEL 7.9 64-bit or newer, including RHEL 8 and 9

- Sigasi Studio depends on

libXss.sowhich can be obtained by installinglibXScrnSaver

- Sigasi Studio depends on

- More information on supported Linux OSes can be found on the Eclipse website

- Sigasi Studio as a plugin in your Eclipse installation:

- Eclipse IDE 2021-03 up to and including Eclipse IDE 2022-12

- Java JRE 11 or 17

We recommend at least 4GB of memory available for Sigasi Studio, and you need about 1GB of free disk space.

Sigasi Studio 5.1.1 Point Release

On March 30, we released Sigasi Studio 5.1.1. This release contains the following bug fixes:

- Eclipse Fixed an issue with Talkback where the version was not being sent

- Eclipse Fixed an issue where hovers would not show on some versions of Windows

Sigasi Studio 5.1.2 Point Release

On May 10, we released Sigasi Studio 5.1.2. This release contains the following changes and bug fixes:

- Verilog Allow

modports to be applied on module instantiation actuals that are arrays of interfaces - Eclipse Upgraded Chromium to 95 from 80, maintaining the stability of 80 but improving its performance

Sigasi Studio 5.1.3 Point Release

On May 22, we released Sigasi Studio 5.1.3. This release contains the following changes and bug fixes:

- Missing build after changing the library of a file or folder

- Improved autocomplete responsiveness for its first invocation

- Eclipse Upgraded to a Chromium 95 that supports Red Hat Enterprise Linux 7

- Verilog Fixed a performance regression in autocomplete