We proudly present the all-new Sigasi Studio 5. In this release, we introduce the unique Sigasi analysis engine for Verilog and SystemVerilog, improved autocomplete, and faster documentation generation.

Note that Veresta and our VS Code extension benefit from all of the changes not explicitly marked as Eclipse.

Next Level Verilog and SystemVerilog Support

Speed, Accuracy, Consistency: To enable new levels of productivity and usability we’ve engineered the new Sigasi analysis engine with these primary goals in mind. It is the foundation for the new features in this and future releases. We can confidently say that we raised our support for Verilog and SystemVerilog to the next level.

The Sigasi analysis engine continuously powers through your project to provide precise and immediate feedback. Due to its massively parallelized approach, it scales up to any kind of project. The engine is agnostic to your design methodology, provides feedback at type time, and directs your focus to the root cause of potential problems.

Rest assured: while you design, we verify, let’s keep moving!

Smart Error Reporting and Navigation

Sigasi 5 has a vastly improved understanding of the designs in your project. Based on the analysis that continuously runs in the background, Sigasi provides reliable and consistent feedback about missing declarations, broken references, and other semantic problems. The reported errors will guide you to the root cause of the issues, hiding distracting consequential problems.

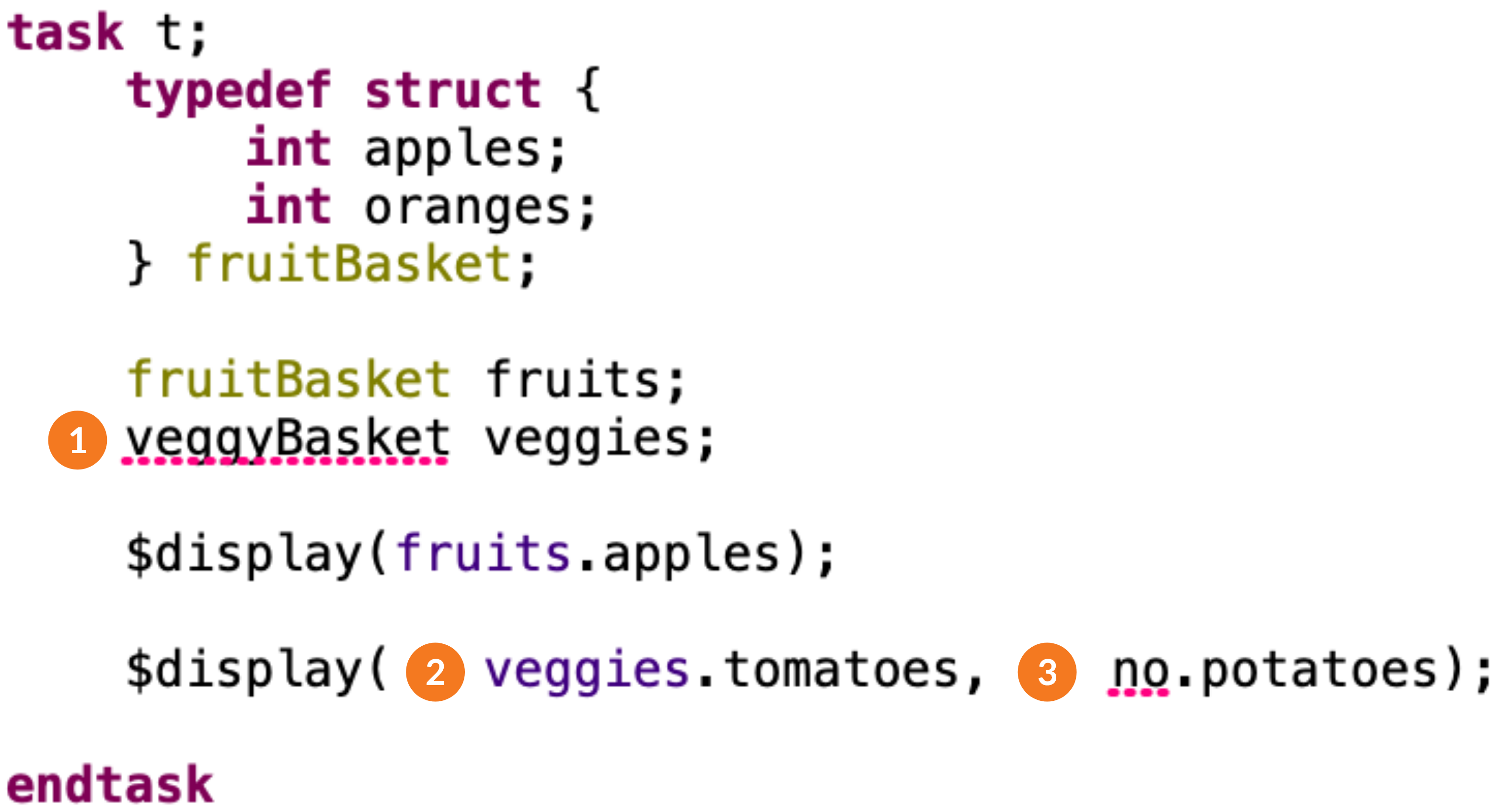

- The variable

veggiesis declared with an unknown type. This is the root cause of the problem. - The usage of

veggiesdoes not report any consequential problems. potatoesis accessed on an unresolved objectno. That is reported as the root cause, no consequential error is reported onpotatoes.

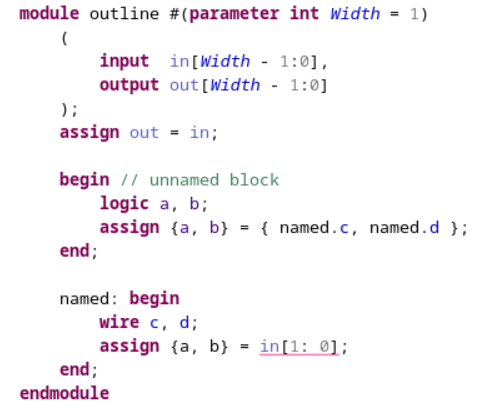

Even the most complex design hierarchies are understood and validated instantaneously. Sigasi 5 analyzes the regular instantiations, the module tree, and bind directives. No matter how complex or deep your design is, the hierarchy information is immediately available at your fingertips. You can follow your hierarchical references, navigate to the referenced instances and structures, and immediately get an accurate understanding of your design. No matter how many top-level units your project contains. Everything is discovered, analyzed, and checked.

The hierarchy is created from four different modules, top, a, b, and c. They form a tree. The screenshot demonstrates that lower-level modules can readily reference items above them in the hierarchy.

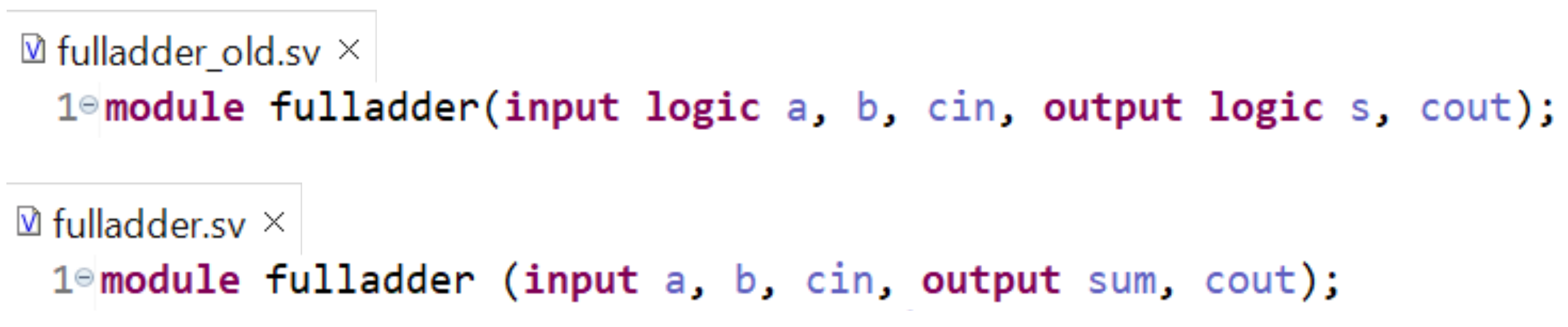

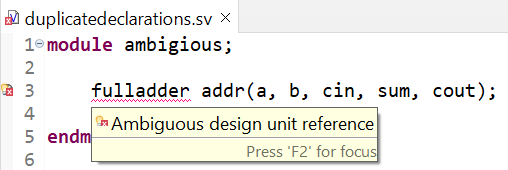

Duplicate declarations, ambiguous references, or simply a copy-and-paste mistake can sometimes be hard to track down. Occasionally, a duplicate top-level design can be on purpose, depending on your project setup. Sigasi will power through anyhow and provide all the information you need to make the right decisions and remain in the flow.

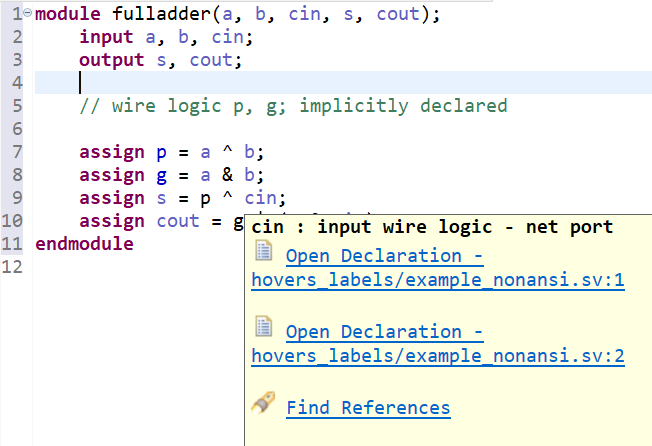

In a misconfigured project it can be the case that multiple declarations with the same name are available. The screenshot above shows an example, where a copy of an older fulladder implementation is lingering around accidentally.

Sigasi 5 will reveal this configuration problem and point out the ambiguity when fulladder is being instantiated.

All the ambiguous declarations are revealed when you choose Go-to-declaration (Ctrl+Hover). Sigasi will point out the duplicates and show their location such that you can directly jump to them.

Labels and Hovers

Rich and accurate visualizations of your design elements are at the heart of Sigasi. The hovers and the label representations show detailed information augmented with the results of the project analysis.

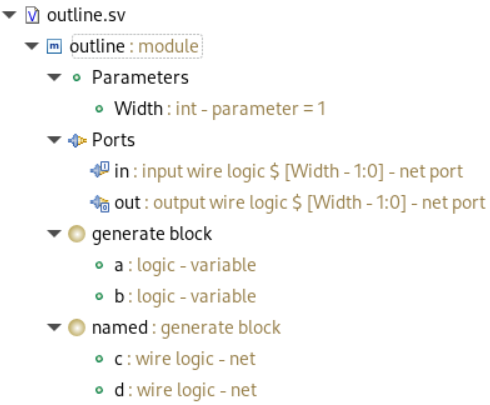

The explicit and implicit properties of Verilog and SystemVerilog objects are rendered in the outline view and all other locations in Sigasi. The details also include information about the object types. Similarly, rich data is also shown in the hover for all declarations and all usages.

The hover information includes details about split declarations or ambiguously resolved references.

Extended SystemVerilog Support

Generic Interfaces

Sigasi 5 has sophisticated support for SV interfaces and modports. Error checking, code navigation, and occurrence highlighting fundamentally help to understand the design and to follow the port mappings. We support named as well as generic interfaces.

The example illustrates the superb support for interfaces in Sigasi 5. The interface declaration ➊ defines two ports gnt and ack. The top module ➋ uses a generic, untyped interface port. Upon instantiation ➌ of the module, Sigasi 5 understands that ack and gnt ➍ are accessible on a in the module body, but data is not. All Sigasi features work accordingly, e.g. navigation, autocomplete, and highlighting.

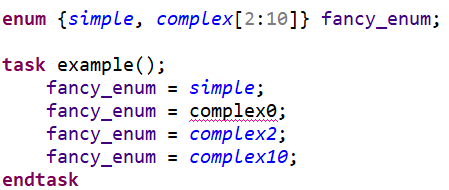

Complex Enum Declarations

SystemVerilog has concise means to define enum types, which are fully understood by Sigasi 5. Usages of the enum literals are accurately detected, analyzed, and highlighted.

The capabilities when working with enum declarations are demonstrated in the screenshot. The fancy_enum is defined with 10 literals, one of them being a simple enum literal, the other 9 remaining literals are unfolded from the range declaration on complex.

Improved Autocomplete

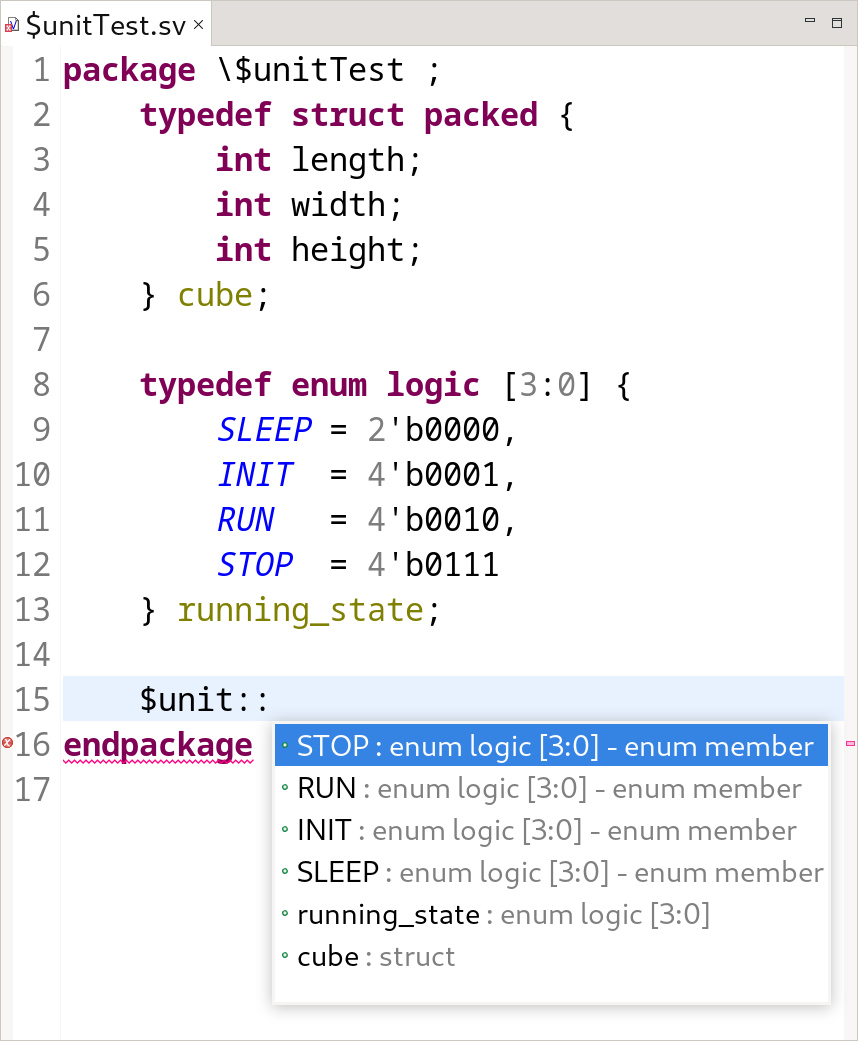

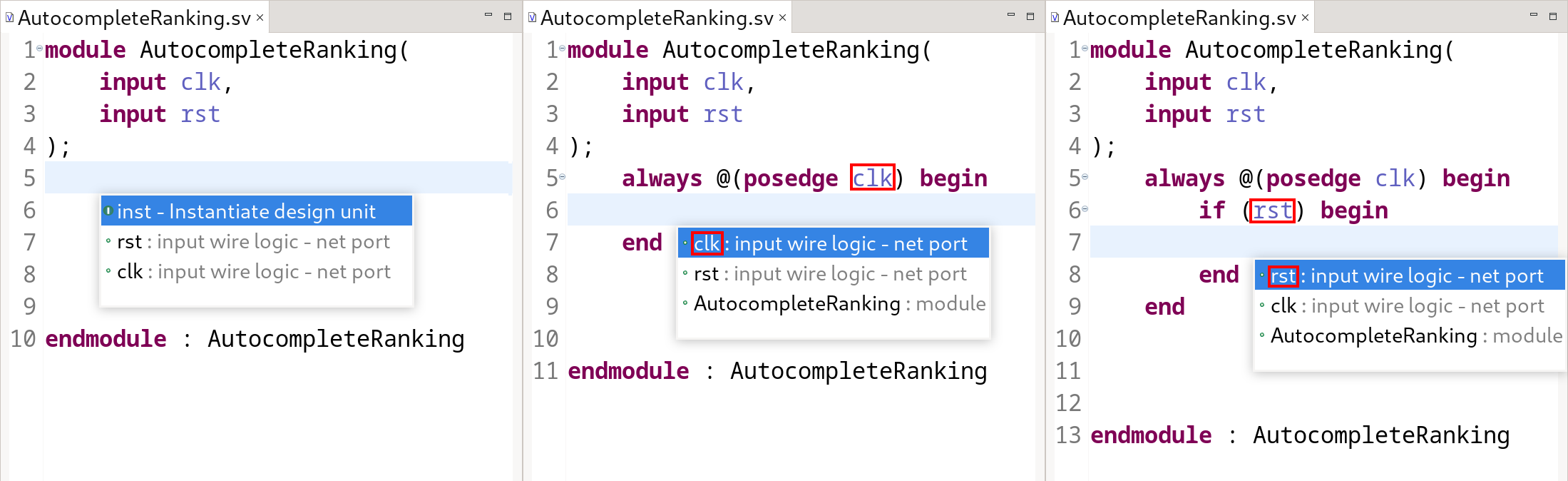

Higher relevance, better prioritization, and improved usability of the autocomplete suggestions embrace the reliability and consistency focus of this release.

Selecting the best autocomplete suggestion has never been easier. Autocomplete now uses substring matching for VHDL, Verilog, and SystemVerilog to filter relevant suggestions, even when you only remember part of the name. The autocomplete pop-up displays the type of each suggestion and matching characters are shown in bold as you are typing.

Specifically for Verilog and SystemVerilog, accuracy improved across the board but especially in scopes like $unit, $root, local::, hierarchical references, structs, and enumeration type ranges i.e. enumeration[N].

A new prioritization mechanism offers you the best matching suggestions first. It is based on a self-adapting statistical model incorporating code-usage statistics (how often an identifier is used) and user-usage statistics (how often a similar autocomplete was selected in a similar context). The image above demonstrates prioritization based on proximity (STOP is closer to the cursor than SLEEP), while the one below demonstrates code-usage statistics.

Finally, autocomplete now conveniently works inside macro parameters.

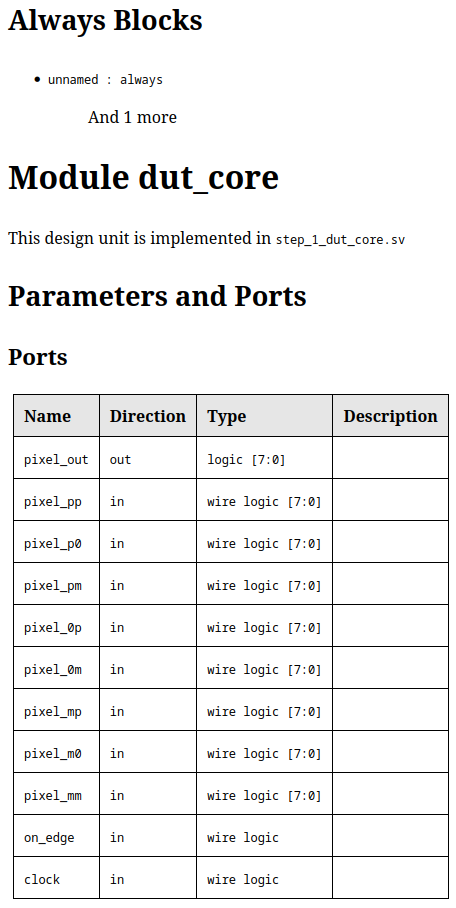

Documentation Improvements

The focus in this release, in addition to some smaller refinements, is on faster documentation export in Eclipse.

Documentation Performance

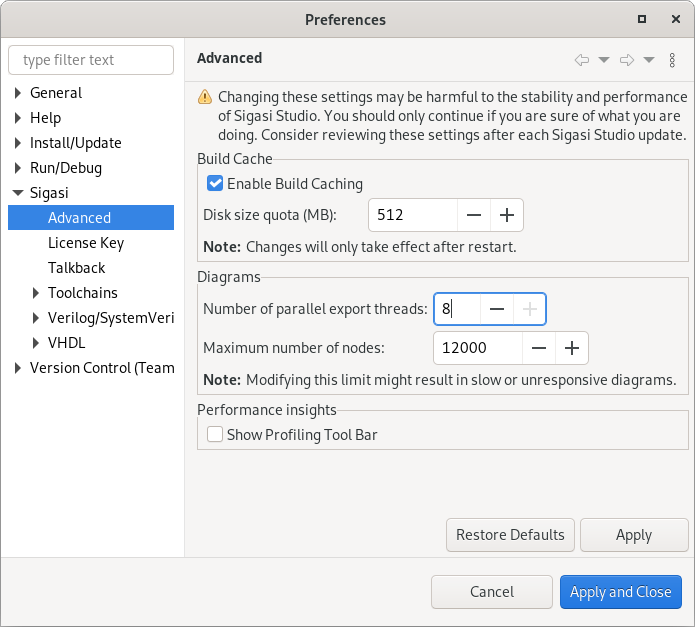

Documentation generation speed has been massively improved by running the most lengthy part, the diagram generation, in parallel. This approach scales linearly with the number of assigned threads. The average 8-core machine can now generate documentation up to 8x faster.

The number of threads that should be used for diagram generation can be configured in Preferences > Sigasi > Advanced.

Small Refinements

- The generated HTML now adheres to the HTML and CSS standards

- Classes now only show their directly declared members, not the inherited ones

- All function return types are shown

- Source code and identifiers always use a monospace font

Removals

- Support for Mac has been dropped

- Eclipse OneSpin integration has been dropped

- Verilog Renaming identifiers has been disabled pending a rework of the rename functionality on top of the new Verilog analysis engine

- Verilog Eclipse The rename design unit to match filename quickfix was disabled for the same reason

Talkback Changes

- Talkback notes which license a user uses

- Eclipse Talkback now automatically offers to enable itself for educational users

- Eclipse Pressing the

without featureslink on the welcome page when you have no (valid) license opens a dialog offering to enable talkback - Eclipse Talkback no longer notes the command line arguments used to start Eclipse

Further New and Noteworthy Changes

- Introduced a new theme with all-new Sigasi logos and artwork

- Our tutorials have been updated to reflect the new 5.0 functionality

- Eclipse Made icons in our import and export wizards consistent

- Eclipse Improved consistency & typography between Sigasi views, wizards, and dialogs

- Eclipse The Verilog tutorial is now available at Help > Sigasi > Start Verilog Tutorial

- Verilog Navigation has been improved to feel snappier. It now immediately opens the relevant region

- Verilog Added support for include-directives using absolute paths e.g.

`include "/libraries/includes/my_include_file.svh". These include paths will be resolved starting from the root of your Sigasi project and ignore the include search paths that were configured. - Verilog Changed default severity of the Disallow reg datatype linting from

WARNINGtoINFO - Verilog Sigasi now also checks that untagged unions do not use dynamic types or

chandles - Verilog Eclipse Assigns to interfaces are now also shown in the Block Diagram

- Verilog Eclipse Library names are no longer shown as part of the name of design units in the Libraries View

- VHDL Component instantiations now insert default values and no longer add a redundant space before the semicolon

- VHDL Eclipse Sigasi Auto Export now restricts top levels to those present in the given project

- VHDL A warning is shown when assigning identifiers using string literals that include underscores, as this is only possible in bit string literals

Updates

- Eclipse Updated to Chromium 88 for rendering graphics and the Documentation View. This improves the performance and stability of these views

Bug Fixes

- Open Design Unit now always has icons for all items

- Eclipse Fixed alphabetical sorting in the Hierarchy View

- Eclipse VHDL preference page options are now properly aligned

- Eclipse Missing python installations are now correctly reported to the user

- Verilog Eclipse Preprocessor property page buttons are now more responsive

- VHDL Fixed VHDL 2019 conditional variable processing in singular, non-project files

- VHDL Fixed a rare formatting case where it did not apply to parts of the code

- VHDL Range checks now work in VHDL 2019

- VHDL Eclipse The quickfix for the component/entity mismatch now shows up when the entity contains empty ports

Thank you for all the bug reports and for enabling Talkback. All your reports have helped us fix many issues that would otherwise go unnoticed.

System Requirements

- Sigasi Studio standalone is supported on:

- Windows: Windows 10 or Windows 11 64-bit

- Linux: RedHat Enterprise Linux RHEL 7.7 64-bit or newer, including RHEL 8

- Sigasi Studio depends on

libXss.sowhich can be obtained by installinglibXScrnSaver - More information on supported OSes can be found on the Eclipse website

- Sigasi Studio depends on

- Sigasi Studio as plugin in your own Eclipse installation:

- Eclipse IDE 2021-03 up to and including Eclipse IDE 2022-12

- Java JRE 11 or 17

We recommend at least 4GB of memory available for Sigasi Studio, and you need about 1GB of free disk space.

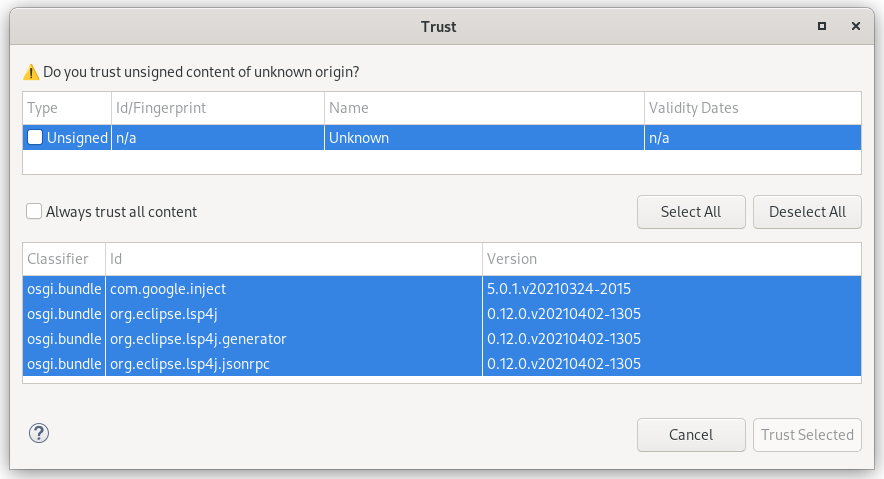

NOTE: you may run into the warning dialog below when installing Sigasi Studio in your own

Eclipse 2022-12 or above installation because this Eclipse version introduces GPG signing.

Sigasi Studio 5.0.1 Point Release

On February 14, we released Sigasi Studio 5.0.1. This release contains the following bug fixes and improvements:

- Autocomplete proposals ignore

_in the prefix. This results in better ordering for snake_case identifiers i.e.my_clkwill be one of the top proposals when using the prefixmycl - Eclipse Sigasi Studio is installable as plugin in your own Eclipse installation given these prerequisites

- Eclipse IDE 2021-03 up to and including Eclipse IDE 2022-12

- Java JRE 11 or 17

- Eclipse Hover windows correctly resize to fit their full content

- Eclipse Applying an autocomplete only moves the viewport if the cursor is not yet within it

- Eclipse Fixed an issue where Window > Preferences > Sigasi > Advanced could only be opened once per session

Sigasi Studio 5.0.2 Point Release

On March 1, we released Sigasi Studio 5.0.2. This release contains solutions for the following reported bugs:

- Templates are not the top suggestion during autocomplete

- Eclipse Error dialog is shown when opening Sigasi Studio

- Eclipse Caching error for specific files

- Eclipse Hover and autocomplete block the editor and take a long time to pop-up