With the Sigasi Studio 4.16 release, we proudly present the following noteworthy changes.

- VHDL 2019 tool directives

- Signed Windows binaries for better interaction with Windows SmartScreen

- A new and improved regex engine

As always, there are many other improvements that enhance speed and usability to offer you a better experience, read on to discover them all.

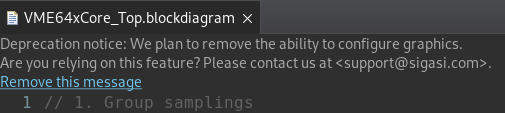

This release we’re deprecating the Graphics Configuration. We’ll introduce a new and improved solution in a following release. If this feature is vital to you please let us know .

VHDL 2019 tool directives

VHDL 2019 improves many aspects of the popular hardware design language. One of the novel features it brings is tool directives - a simplified version of the preprocessor found in SystemVerilog or the C family of languages.

Tool directives allow to conditionally enable code based on tool type, debug mode, or really any other custom variable. This release adds full support for these new VHDL 2019 directives to Sigasi Studio.

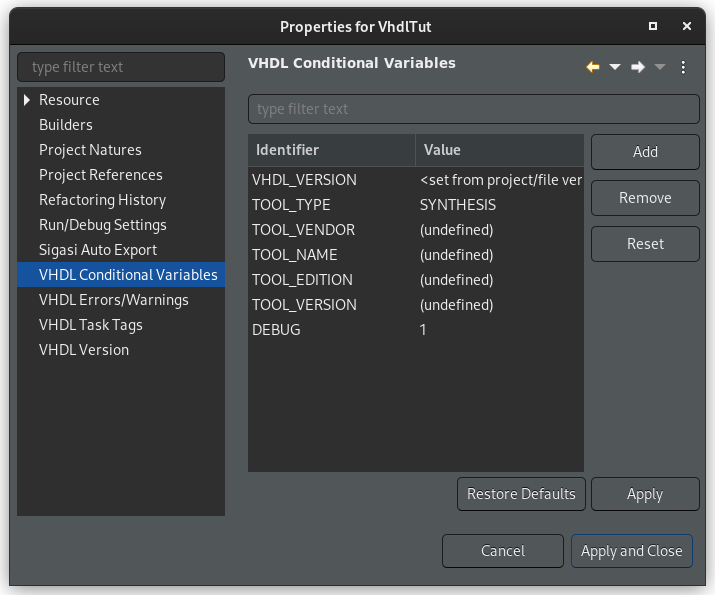

You can edit the defined tool directives by right-clicking your project and then going to Properties > VHDL Conditional Variables.

Check out the video to see directives in action.

Signed Windows binaries

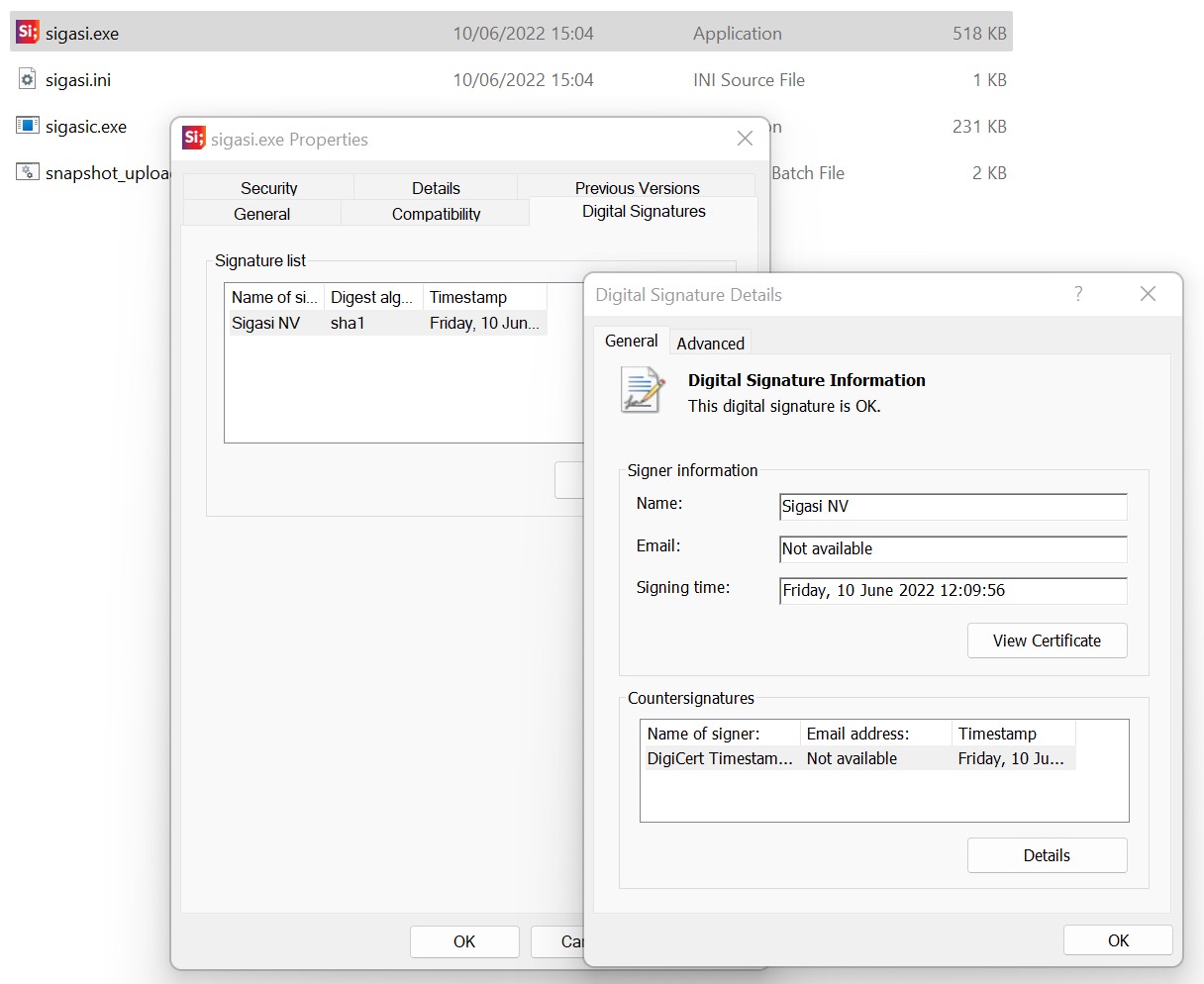

Starting with the Sigasi 4.16 release, our installation files are signed and notarized for Windows, Mac and the Java virtual machine.

Windows SmartScreen, Mac OS, and malware detection software will no longer raise an alarm when Sigasi Studio is launched for the first time because all the binaries are now published with irrefutable proof that no malicious third party tempered with the original installation files.

New and improved regex engine

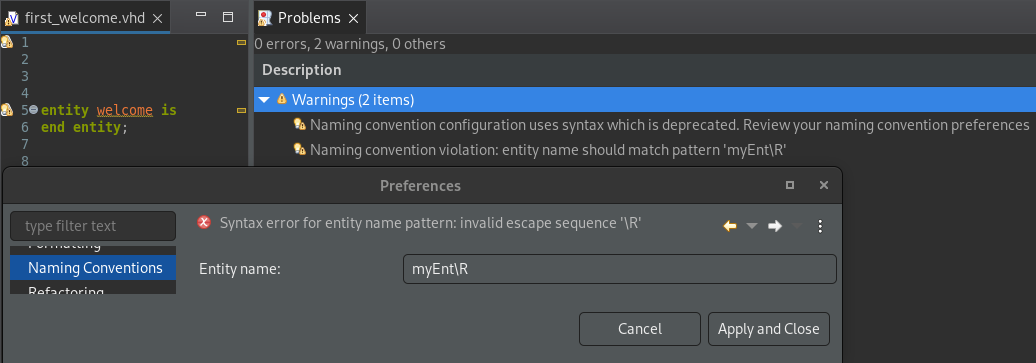

Regular expressions are used in many parts of Sigasi Studio. The most visible feature using it is the Naming Conventions, where you can fill in your own expressions to be used in validations. Next to writing syntax errors however, a regex can easily incur a large, exponential performance hit. A small change to a regex can cause a high amount of backtracking, skyrocketing its execution time.

We carefully evaluated different options to mitigate potential performance problems that are caused by some shapes of regular expressions. Sigasi Studio 4.16 now ships with RE2/J which scales nicely for large inputs and even complex naming conventions.

Do note that an extra warning directing you to the naming conventions will be shown if a regex is used that is supported by the Java regex engine, but not by RE2/J.

Deprecated Graphics Configuration

Sigasi can automatically generate a Block Diagram and a State Machine from your code. However, these autogenerated diagrams might become quite complicated and hide the essence of the design. Sometimes you also just want to create custom visualizations or simplifications.

For this reason, Sigasi features a custom DSL (called the Graphics Configuration) that allows you to filter, color, highlight, group,… parts of your design in these diagrams. However, a custom DSL, even with good a good editor, is quite a cumbersome solution to this issue.

Sigasi has deprecated this cumbersome solution and will present a more user-friendly approach in a future release. If you feel like this feature is vital to you please let us know .

New and Noteworthy Changes

- Sigasi on linux now shows Chromium dependencies in an error dialog at startup. Mac and Windows have no need for such a dialog as they always have all the necessary dependencies available

- All remaining mentions of the Creator license have been removed

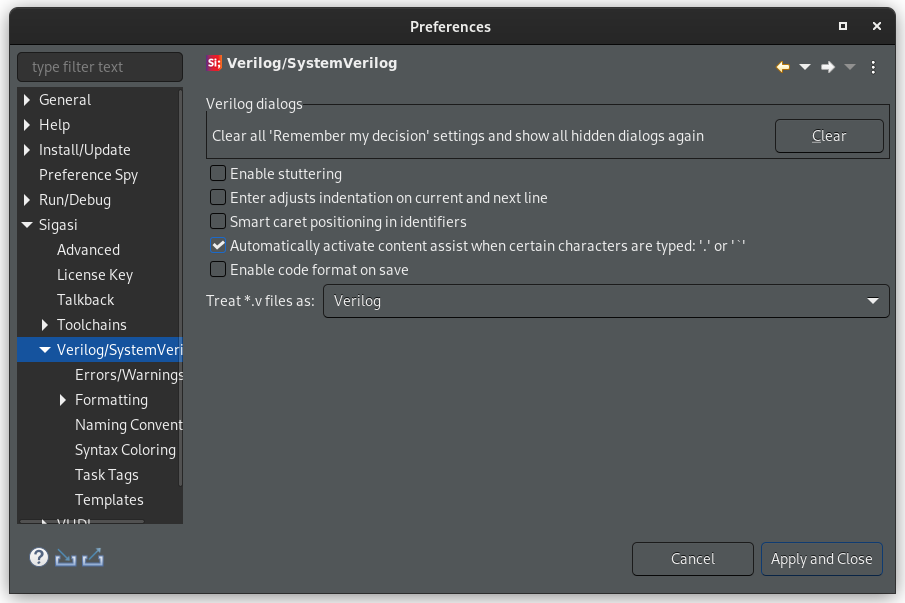

- The automatic autocomplete after typing

.or`can now be disabled inPreferences > VHDLorPreferences > Verilog/SystemVerilog - Formatting has been enabled for files that use keywords of a higher language version

- We’ve made it easier to Ctrl + hover over very short identifiers

- Improved resilience to changes in the project for the Find References View

- Improved responsiveness for the Find References View

- Removed the button from views in which they were redundant

- Removed outdated documentation from Eclipse’s internal documentation pages

- Navigating from the Outline View or the Hierarchy View to the editor now selects more relevant constructs

- A warning is now issued on the

.library_mapping.xmlwhen it references non-existent files. A Quick Fix to remove the offending mapping has been also been added. - Errors reported by external toolchains that do not contain a location are now propagated to Sigasi Studio as errors on the project

- The Documentation View now reacts better to all kinds of changes to the project, assuring it never misses a refresh

Show In > Dependenciestries harder to select the right element, preventing disturbing beep sounds- Colors changed through

Preferences > Sigasi > VHDL or Verilog/SystemVerilog > Syntax Coloringare now immediately applied - The State Machine View icon to show edge labels (

) has been replaced by an icon to hide comments (

) has been replaced by an icon to hide comments ( ) and an icon to hide the conditions (

) and an icon to hide the conditions ( ). The Graphics Configuration now also offers the ability to show only comments or conditions separately through

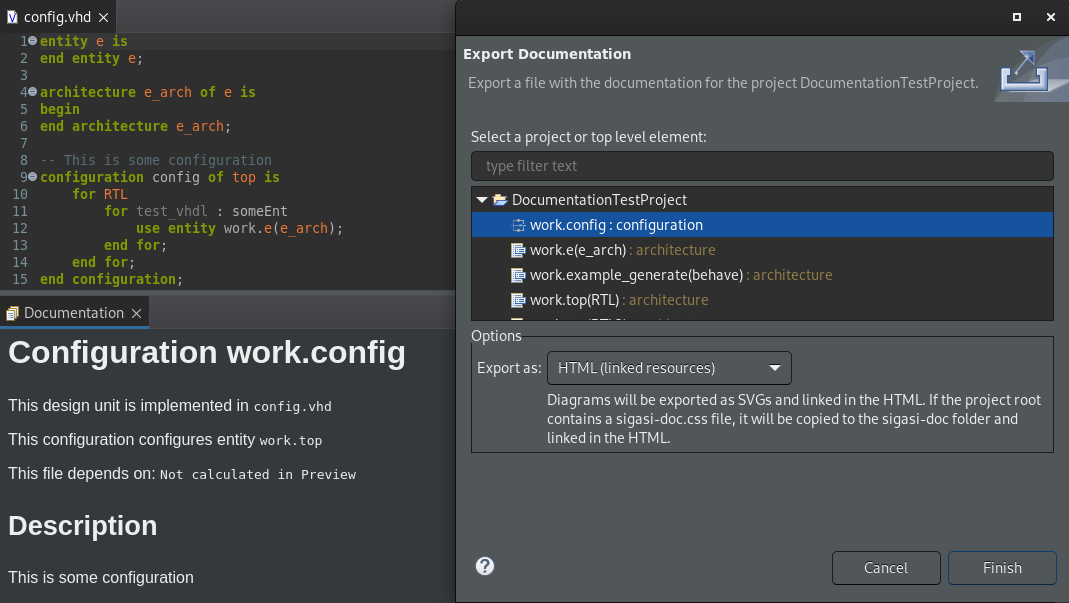

). The Graphics Configuration now also offers the ability to show only comments or conditions separately through labels commentorlabels condition. - All of our tree views (Hierarchy View, Open Design Unit, Export diagrams, …) now use consistent capitalization and coloring

- It’s now possible to select the project for which to configure VUnit in the Add VUnit support dialog

- Improved cleanup of OS resources in autocompletes

- We’ve reformatted our license files to improve readability, the actual content was not changed

- We’ve made our tutorials more consistent, making sure they use correct wording, hotkeys and directions towards other screens

- [VHDL] Attributes now have an icon and are marked as attributes in the autocomplete pop-up window

- [VHDL]

openin ranges is now taken into account for validations - [VHDL]

configurations are now included in the exported documentation - [Verilog] Greatly decreased memory usage and increased performance when using many include files

- [Verilog] All macro invocations are now highlighted

- [Verilog] Added support for

edgein timing checks - [Verilog] Added support for assignment patterns in initial blocks

initial begin

'{c} = s;

end

- [Verilog] Removed

localparameters from theParameterstable in exported documentation as these are not externally modifiable - [Verilog] Added linking support for

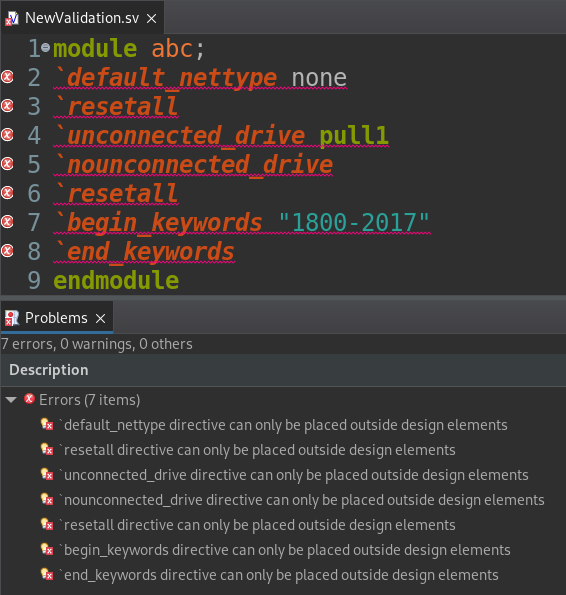

letdeclarations inclockingblocks - [Verilog] Using invalid constructs - such as

modulesorinterfaces- inpackageswill now generate an error - [Verilog] Pressing

enterat the end of many constructs (package,class,interface, …) will now trigger Smart Indent to unindent the ending line - [Verilog] Stuttering has been removed from Verilog as it’s only useful for VHDL

- [Verilog] Improved highlighting of the

Invalid package itemvalidation - [Verilog] Xilinx encrypted files (starting with

Xlx) are now ignored by the Verilog engine - [Verilog] The Hierarchy View now shows the labels of

generateblocks - [Verilog] Added new validations for

- infinitely nested preprocessing directives

- allowed locations of preprocessor directives

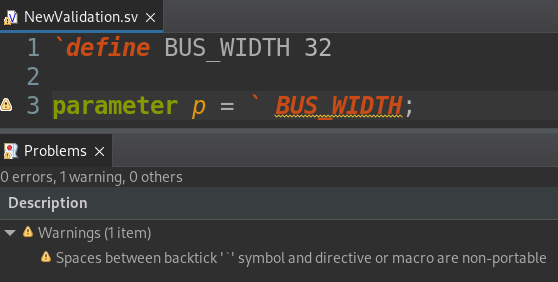

- spaces between the backtick and the preprocessor directive’s name

- infinitely nested preprocessing directives

Updates

- Eclipse has been updated to 2022-03

- JustJ (the JRE shipped with Sigasi Studio) has been updated to 17.0.3

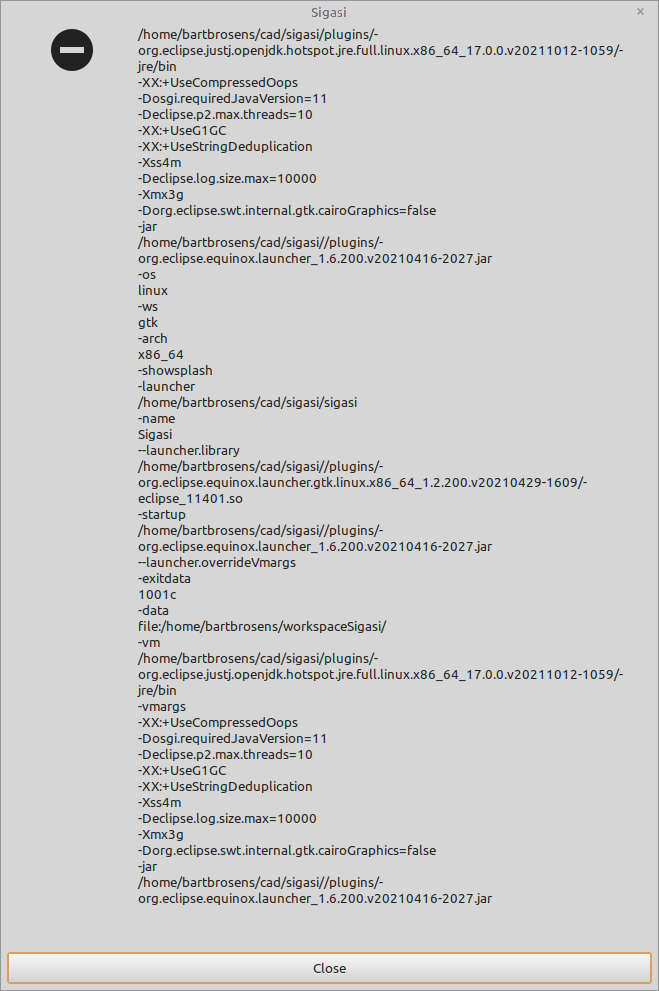

Note that you may run into the error dialog below when you restart Sigasi Studio after the update because the JRE has changed. If you close the dialog, and restart Sigasi Studio manually, everything should work as expected.

Bug fixes

- [VHDL] Fixed linking for array types that use

openin their ranges - [VHDL] Fixed formatting for

elseclauses that have a trailing single line comment - [VHDL] Only present Quick Fix suggestion for subprogram invocations without matching subprogram when the Quick Fix can improve the situation

- [VHDL] Fixed missing autocompletes

- [Verilog] Fixed false positive errors for blank ports in modules

- [Verilog]

`ifdef,`else,`endifdirectives are now correctly greyed out in disabled preprocessor branches - [Verilog] The right file encoding is now passed to Verible

- [Verilog] Block Diagram generation will no longer fail for net declarations without a name

- [Verilog] Fixed formatting for files containing unclosed multiline comments

- [Verilog] Fixed Verible formatting when there is a space in the Verible installation path

- [Verilog] Fixed missing autocomplete when typing a single backtick in an empty file

- A lot of other issues we could fix thanks to your Talkback reports

System requirements

- Sigasi Studio standalone is supported on:

- Windows: Windows 10 (64 bit) or newer

- macOS 11.6 Big Sur or newer

- Linux: RedHat Enterprise Linux RHEL 7.7 (64 bit) or newer

- Sigasi Studio depends on

libXss.sowhich can be obtained by installinglibXScrnSaver - More information on supported OSes can be found on the Eclipse website

- Sigasi Studio depends on

- Sigasi Studio as plugin in your own Eclipse installation:

- Eclipse IDE 2021-03 up to and including Eclipse IDE 2022-03

- Java JRE 11 or 17

We recommend at least 4GB of memory available for Sigasi Studio, and you need about 1GB of free disk space.

Thanks for all the bug reports and enabling Talkback.

Sigasi Studio 4.16.1 point release

On July 14 we released Sigasi Studio 4.16.1. This release fixes the following reported issues:

- Fixed custom templates not showing up in preferences

- Fixed content assist not working for vector range declarations

- Fixed content assist ignoring default values for ports

- Fixed incompatibility with Eclipse 2022-06

- Added new template variable

${filename_ext}that inserts the filename with its extension