We are proud to present the Sigasi Studio 4.14 release. This release continues to improve the user experience with improved semantic highlighting in VHDL, Verilog and SystemVerilog, better navigation in Verilog and SystemVerilog and speed improvements for clean builds. The handling of multiple language versions has been improved. Also, VUnit projects now handle their own library mapping.

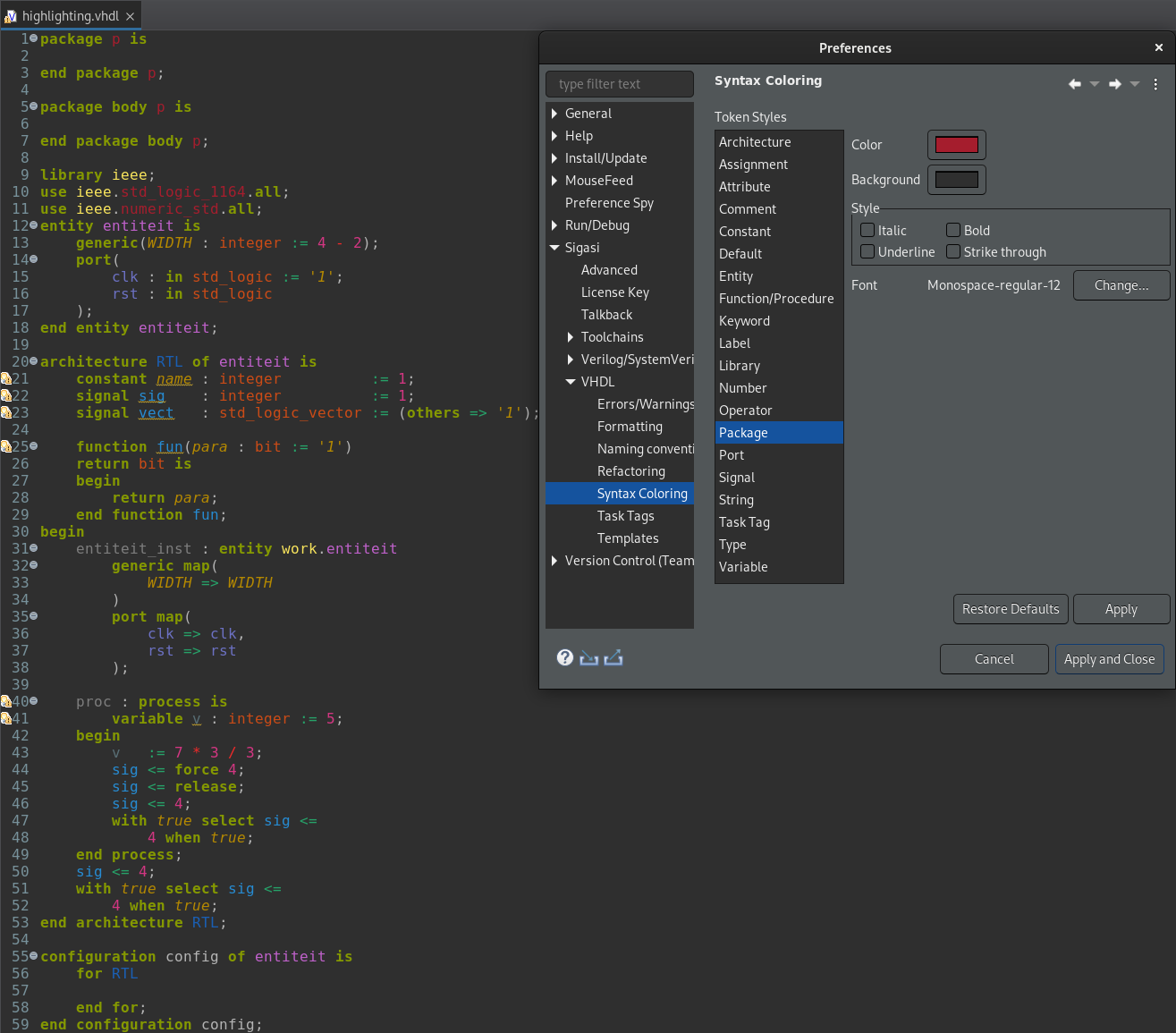

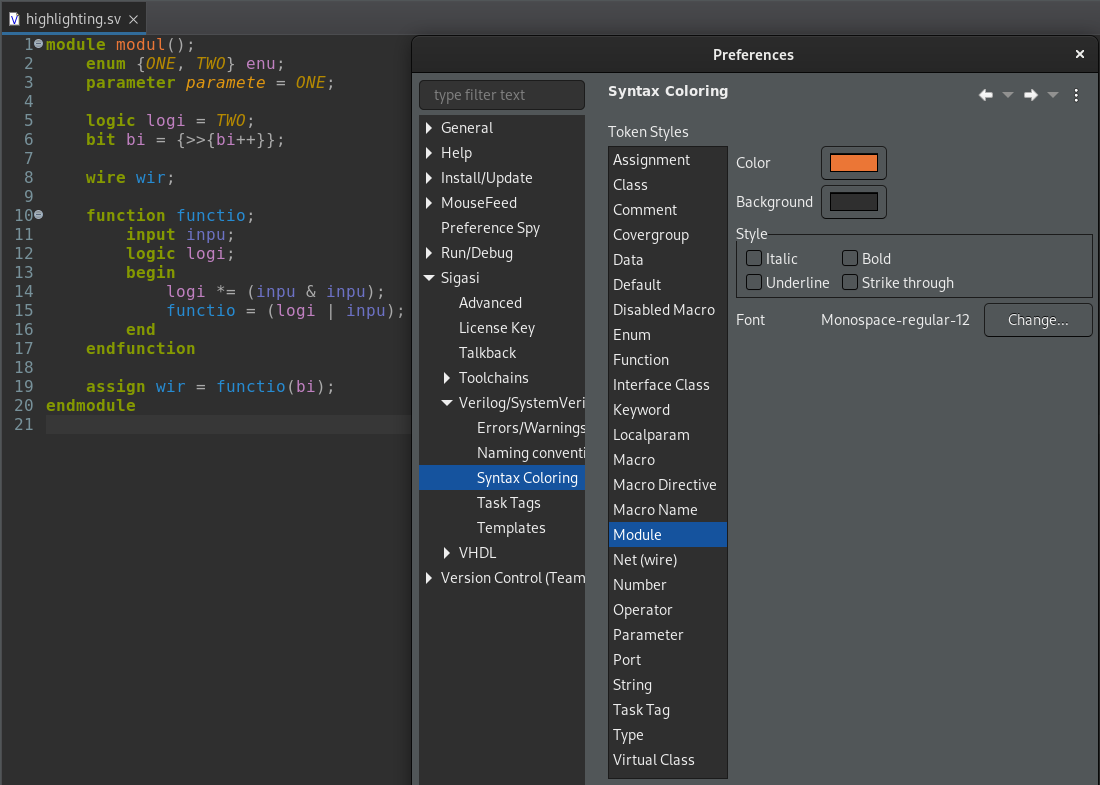

Improved highlighting for VHDL, Verilog and SystemVerilog

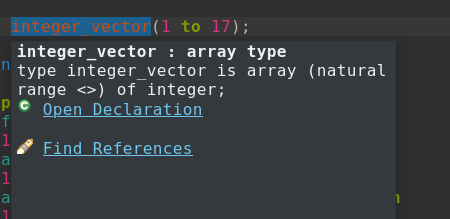

Recently, we’ve been requested to allow color customization of more constructs. This update allows users to customize the highlighting of 6 new VHDL and (System)Verilog constructs to their needs. However, the default for these constructs remains identical to the previous releases for those who are happy with what Sigasi Studio offers out of the box.

While we were looking into the highlighting anyway, we’ve alleviated a bottleneck, greatly improving the performance of highlighting in Sigasi Studio.

For VHDL, Sigasi Studio now allows custom entity, architecture, library, package, operator, and assignment highlighting

For [(System)Verilog], Sigasi Studio now allows custom data, enum, function, module, operator, and assignment highlighting

Improved navigation in Verilog and SystemVerilog

This release, we’ve further increased the correctness and accuracy of our core (System)Verilog engine, which brings with it improved navigation.

We’ve added navigation for

- ports being referenced in

specifyblocks - references in the initialization expressions in UDP ports

- type and parameter declarations from subclasses to superclasses

- hierarchical references in clock variable initialization expressions

- references in default clocking rules

- variable references in

randsequenceconstructs - arguments of

randomizecalls - return types of top level functions when there are multiple constructs with the same name as the return type

- static-property references of parameterized classes

- unqualified constructor invocations

superand parameter references used in parameterization of a super class

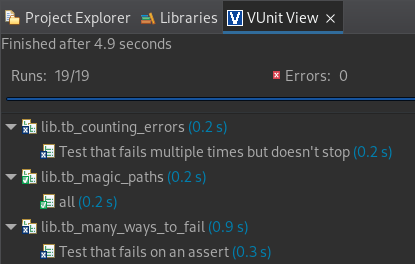

VUnit automated library mapping

The Sigasi Visual HDL VUnit Integration has been improved.

The information from the VUnit run.py file is used to automatically handle libraries in Sigasi Studio.

There is no more need to maintain a redundant library configuration yourself. This saves time and reduces the potential for errors.

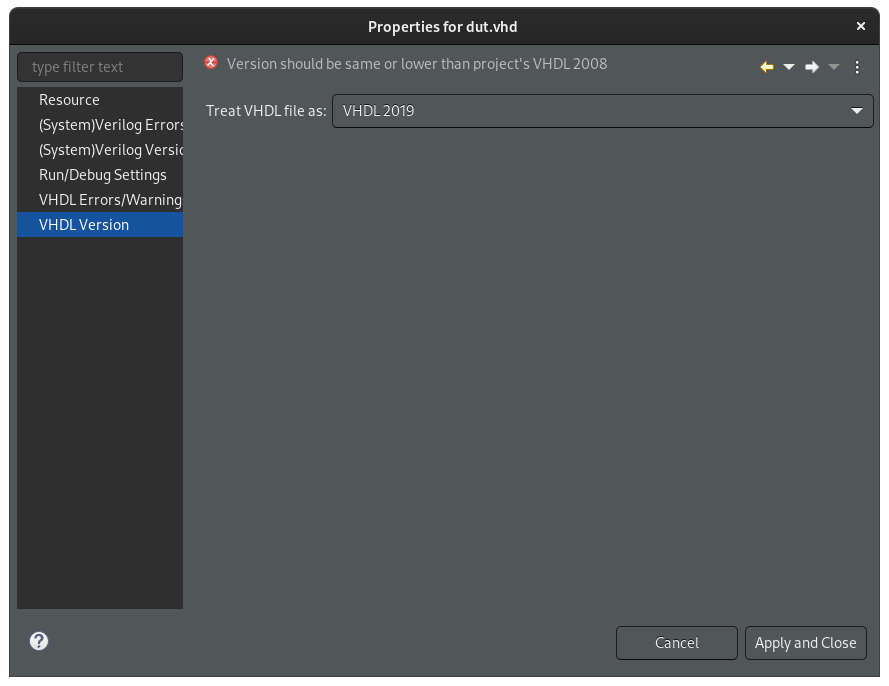

Improved handling of language version mismatches

Sigasi Studio uses the concept of Common Libraries. This is a folder in which to add reusable libraries. These can be vendor libraries, third-party IP libraries or your own reusable libraries. By default, the STD and IEEE libraries are added to this folder.

When a VHDL project’s language level changes, or when one of the VHDL files within has to be parsed with a higher language level, the Common Libraries need to be updated. In this release we’ve improved the fixing of mismatches between the Common Libraries’ and the project’s VHDL version.

- Changing the project VHDL version will now reset the Common Libraries

- When VHDL support is added to a project, Common Libraries with the correct version are automatically added

- Improved the message for the

Reset Library Mappingaction - Added new, and modified existing, validations, that can reveal additional errors on existing projects

- Added a validation when a file’s VHDL version is higher than the project’s

- Improved the validation when the Common Libraries’ and the project’s VHDL version differ

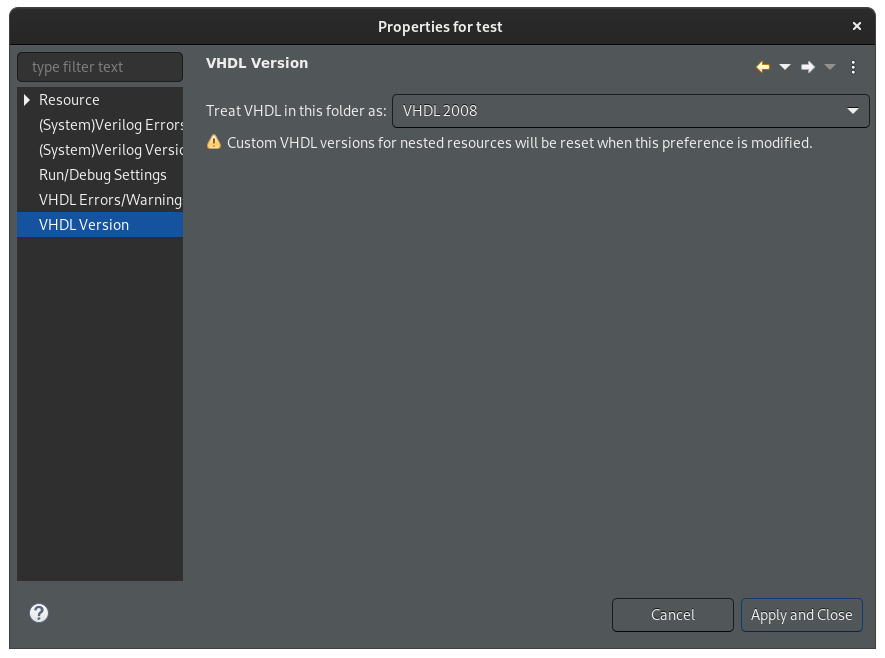

- It’s no longer possible to set the VHDL version of a file higher than the project’s VHDL version

- Added a warning when the VHDL version of a folder or an entire project is changed, since it affects all contained files and will reset their versions too

Other New and Noteworthy Changes

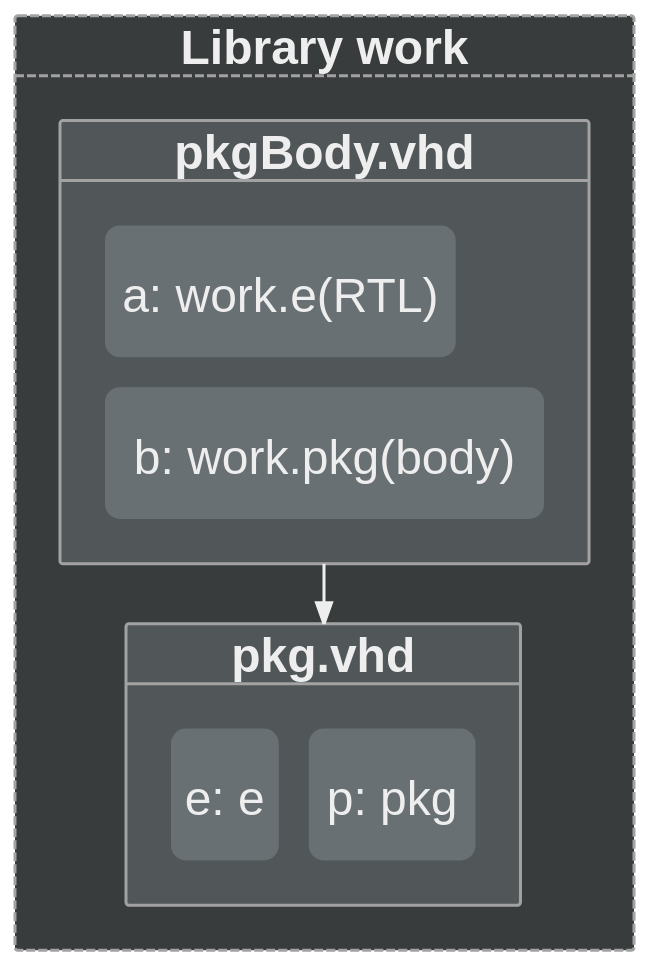

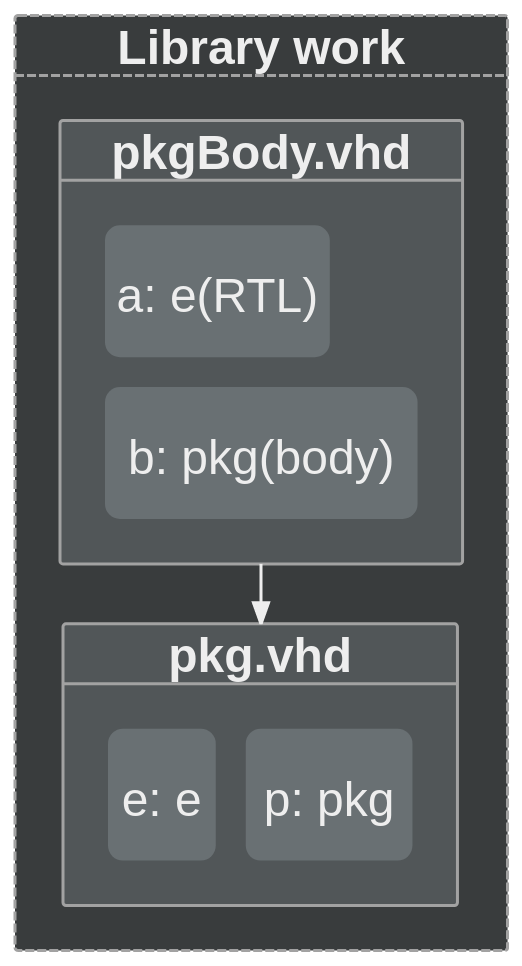

- The dependencies view now hides implied libraries in the qualified name where possible (e.g.

pkginstead ofwork.pkg)

Old view

New view

- Improved support for deeply nested expressions (e.g.

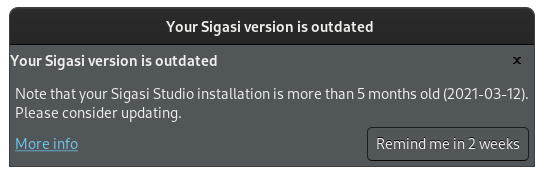

1 + 1 + 1 + ...). As a side effect, clean (successive) builds are now up to 20% faster - Added an option to be reminded of your outdated Sigasi Studio version instead of having to close the dialog every time you open Sigasi Studio

- Reordered, deduplicated, and cleaned up the

Newmenu when right clicking files/projects. To make new Sigasi example projects you can use File > New > Sigasi > Other > Examples - Sigasi now uses a monospace font in autocomplete template view. This should help to achieve the desired formatting more easily

- Placed Verilog and VHDL next to each other in the Sigasi preferences

- Hovers now use the font and font size configured in General > Appearance > Colors and Fonts > Basic > Text Font

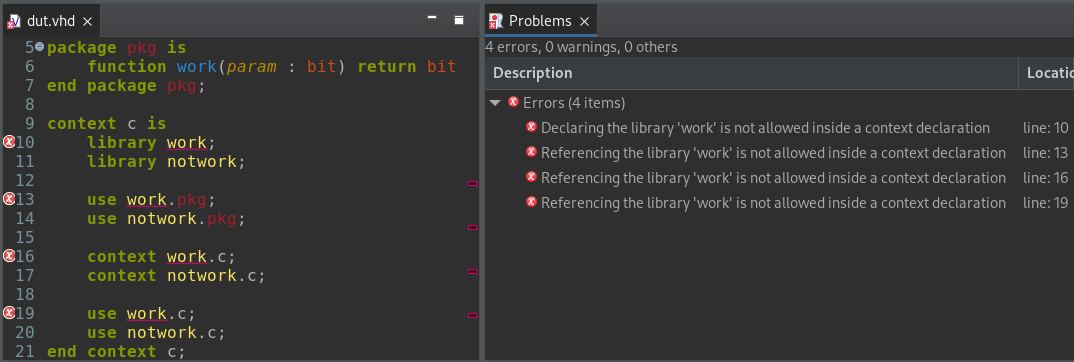

- [VHDL] Sigasi now reports errors when the library

workis defined or referenced incontextdeclarations

- [VHDL] Improved quick fix for removing unused declarations such that it always removes the entire declaration

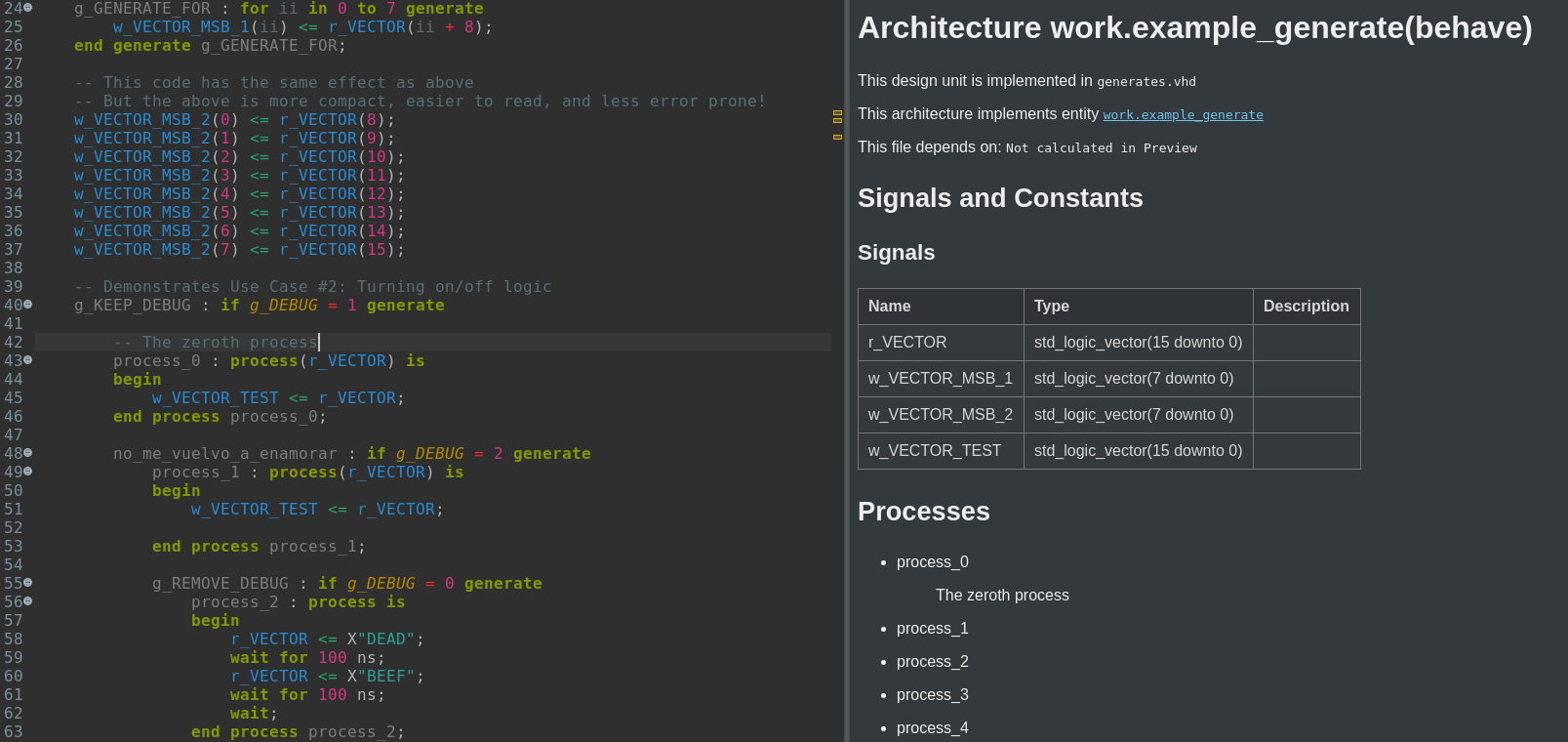

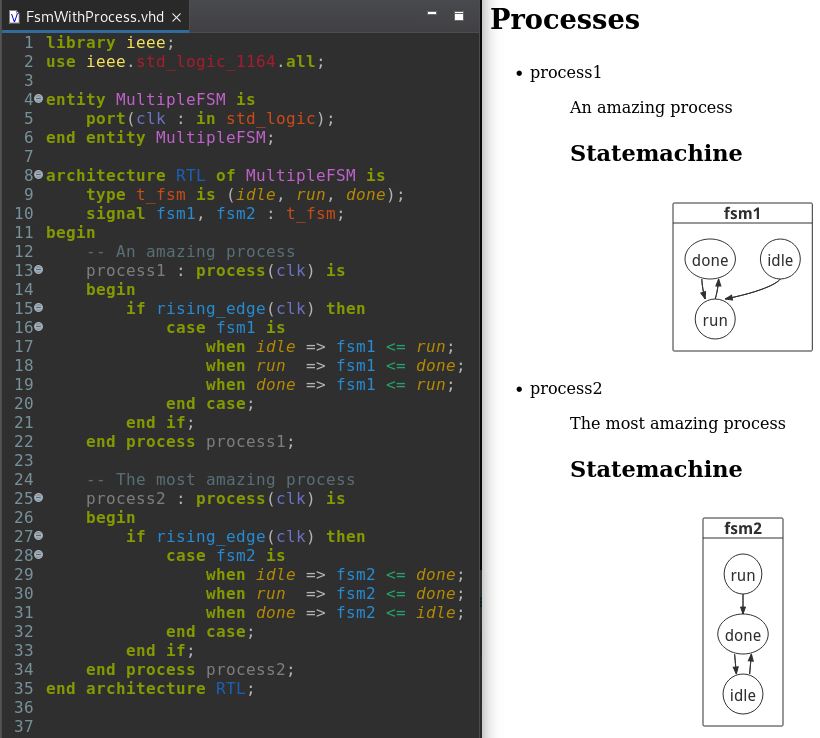

- [VHDL] Added processes that are nested in generate statements to the documentation

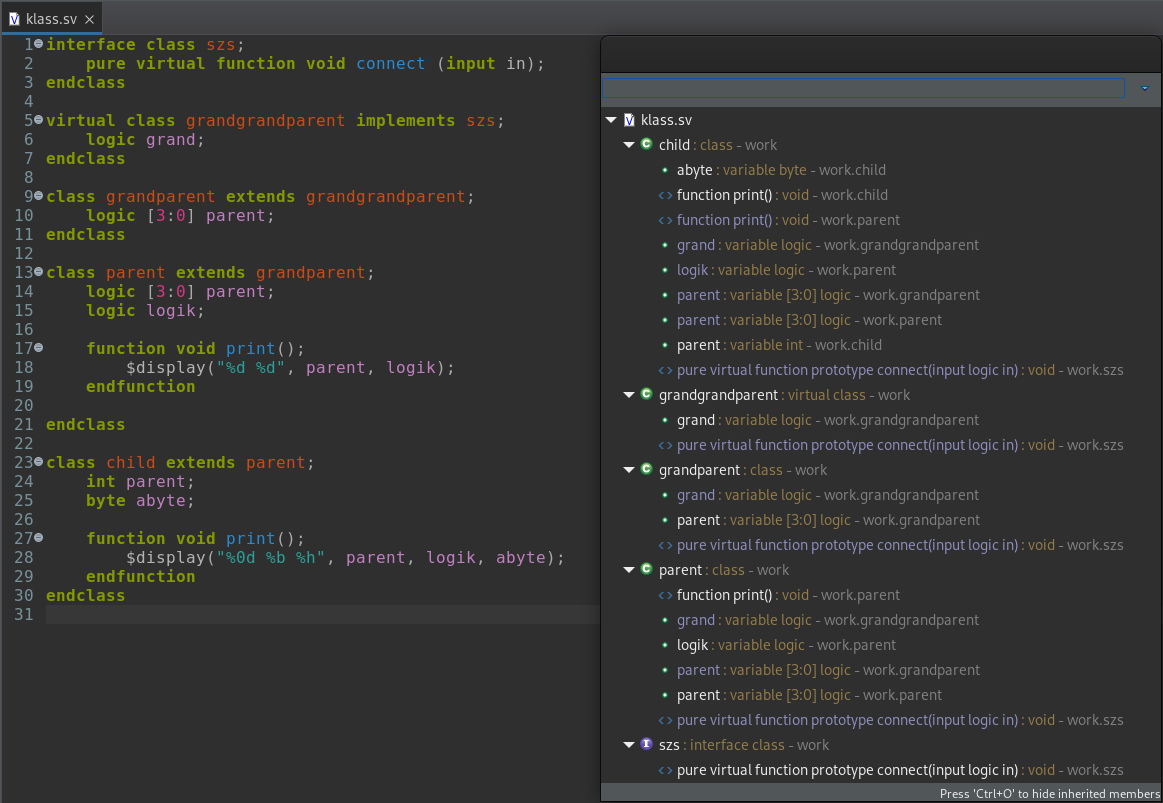

- [Verilog] Added inherited members to the quick outline. You can show them by pressing Ctrl+O again when you already have the Quick Outline open

- [Verilog] Improved formatting for

constraint,sequenceandpropertyblocks - [Verilog] Improved handling of recursive file inclusion

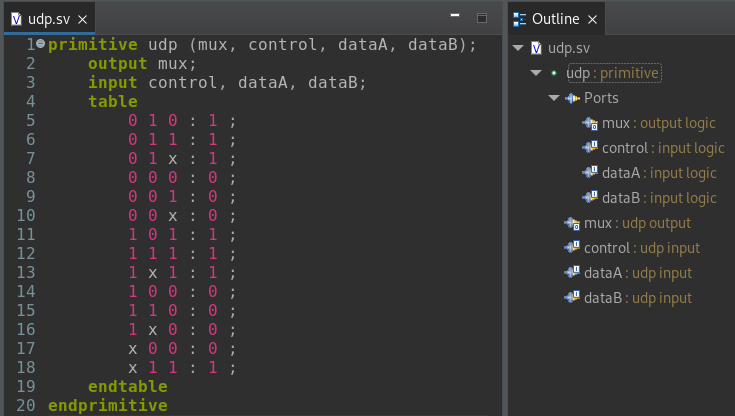

- [Verilog] Added user-defined primitives to the outline

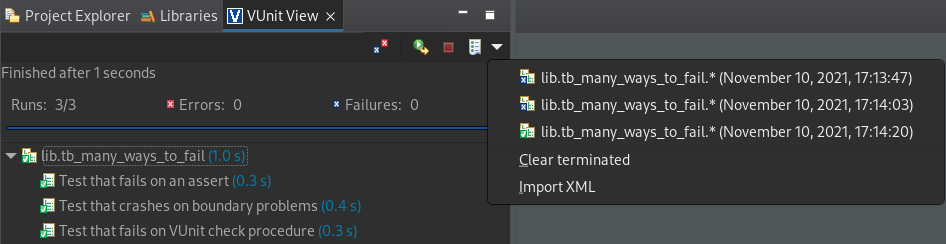

- [VUnit] You can now view the history of your VUnit runs

- [VUnit] Sigasi now shows different icons when a test failed, throws an error, or is successful

- [OneSpin] Improved error message when the

$ONESPINROOTenvironment variable is not set, or is set incorrectly - [Documentation] FSMs are now shown with the processes or always blocks that define them, instead of in there own section

- [Documentation] When there is no documentation to show for the current file, the documentation view now shows

No documentation to showinstead of a blank page

Updates

- The JRE shipped with Sigasi Studio is now Java 17

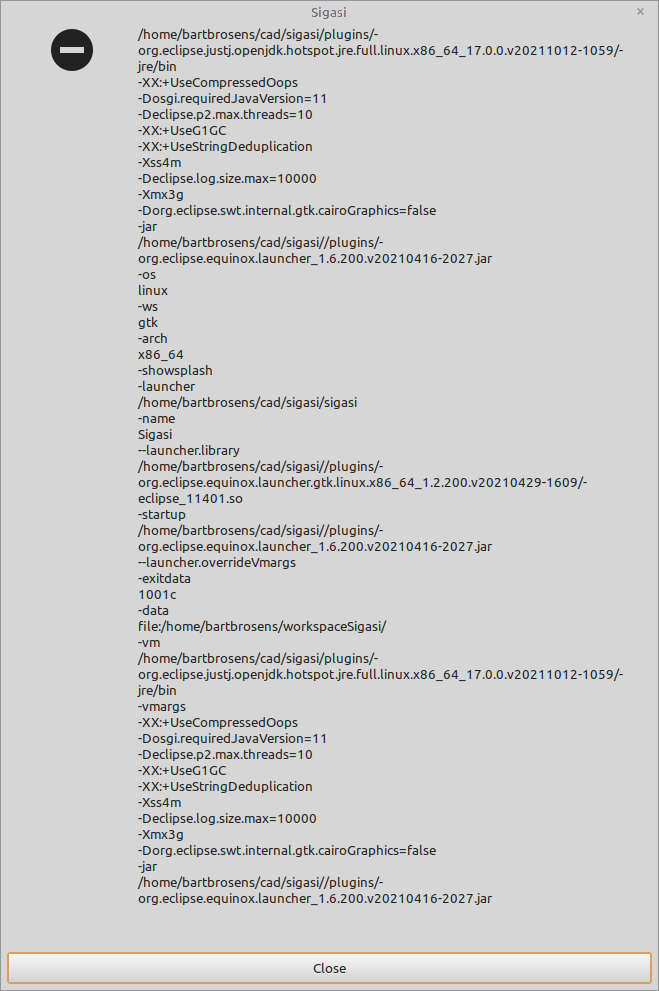

Note that you may run into the error dialog below, when you restart Sigasi Studio after the update because the JRE has changed. If you close the dialog, and restart Sigasi Studio manually, everything should work as expected

- We’ve updated Eclipse in the standalone Sigasi Studio to Eclipse 2021-09

Bug fixes

- Made sure graphics run flawlessly under Java 17

- Sigasi now allows refactoring with the cursor positioned at the end of an identifier

- The

Start Async Samplingbutton has been disabled on Windows since YourKit does not support this feature on Windows - Made sure the quick fix for mismatched components works when the

entityormoduledeclarations are incomplete - Removed duplicated Edit > Toggle Block Selection menu entry

- Added a missing decoration for HDL projects in the project explorer

- Trying to open a file in Sigasi Studio from the command line will no longer crash

- Mapping files to a library with ignored markers will now correctly remove the markers on said files

- [VHDL] When writing to a

std_(u)logic_vectorvariable, different from the one selected in acasestatement, a state machine will no longer be produced - [VHDL] The icon for

components in the outline view that was lost in the 4.13 release has been reinstated - [VHDL] Removed false positive errors in Sigasi Studio Starter

- [VHDL] Removed false positive errors for incomplete port and generic declarations

- [VHDL] Fixed missing validations when an invalid

returnexpression is used - [VHDL] Fixed regressions in auto indentation near lines ending with parentheses

- [Verilog] Fixed a rare missing autocomplete for hierarchical references

- [Verilog] Fixed the symbol for

part selectin the outline - [Verilog] Removed false positive errors for

classextensions with incorrect syntax - [Verilog] Added missing type error when assigning a

bytearray, on which a built-in method is called, to astring - [Verilog] Fixed highlighting of non-ANSI parameters in classes

- [Verilog] Fixed rare error in hover and outline of

letdeclarations - [VUnit] Fixed initialization issues with VUnit projects

- [VUnit] Sigasi now only shows

Run VUnit testsin HDL editors for projects configured for VUnit - [Vivado] Fixed compilation issues when editing an architecture whose entity is defined in a separate file

- [Documentation] Fixed documentation export for some incomplete designs

- [Graphics] Fixed

openport visualization in block diagrams - [Graphics] Fixed error message when hovering over elements in graphical views

- A lot of other issues we could fix thanks to your Talkback reports

System requirements

- Sigasi Studio standalone is supported on:

- Windows: Windows 10 (64 bit) or newer

- macOS 11.6 Big Sur or newer

- Linux: RedHat Enterprise Linux RHEL 7.7 (64 bit) or newer

- Sigasi Studio depends on

libXss.sowhich can be obtained by installinglibXScrnSaver - More information on supported OSes can be found on the Eclipse website

- Sigasi Studio depends on

- Sigasi Studio as plugin in your own Eclipse installation:

- Eclipse IDE 2021-03 up to and including Eclipse IDE 2021-09

- Java JRE 11 or 17

We recommend at least 4GB of memory available for Sigasi Studio, and you need about 1GB of free disk space.

Sigasi Studio 4.14.1 point release

On February 1 we released Sigasi Studio 4.14.1. This release fixes the following reported issues:

- Project specific validations not working when there are spaces in the path

- Added Java 17 support to our profiling features

- [Verilog] Class Hierarchy View not working when opening it from a class instance instead of the class’ identifier

Sigasi Studio 4.14.2 point release

On February 8 we released Sigasi Studio 4.14.2. This release fixes the following reported issues:

- Language versions not working when there are spaces in the path

Thanks for all the bug reports and enabling Talkback.