We are proud to present the Sigasi Studio 4.13 release. This release contains a lot of overall improvements, a better editing experience, richer documentation and many other new and noteworthy changes for Sigasi Studio’s Verilog, VHDL and SystemVerilog support.

Improved editing experience

- We improved the behavior of using backspace for “indentation whitespace”. If you are using spaces for indentation, backspace now removes one level of indentation instead of a single space character

- We made it easier to put an expression between parentheses: When you select a region and press

(or[, the selected region is enclosed with the matching closing parentheses ()or])

- We made it easier to create strings. When you select some text and press

", the selected text will be transformed into a string. This works for both regular and multi-line strings

- Improved auto de-indentation (

casestatements,functionsignatures,intial, …)

- Improved warning hovers: long texts are now trimmed to make sure quickfixes are always visible

Other New and Noteworthy Changes

Improved documentation generation

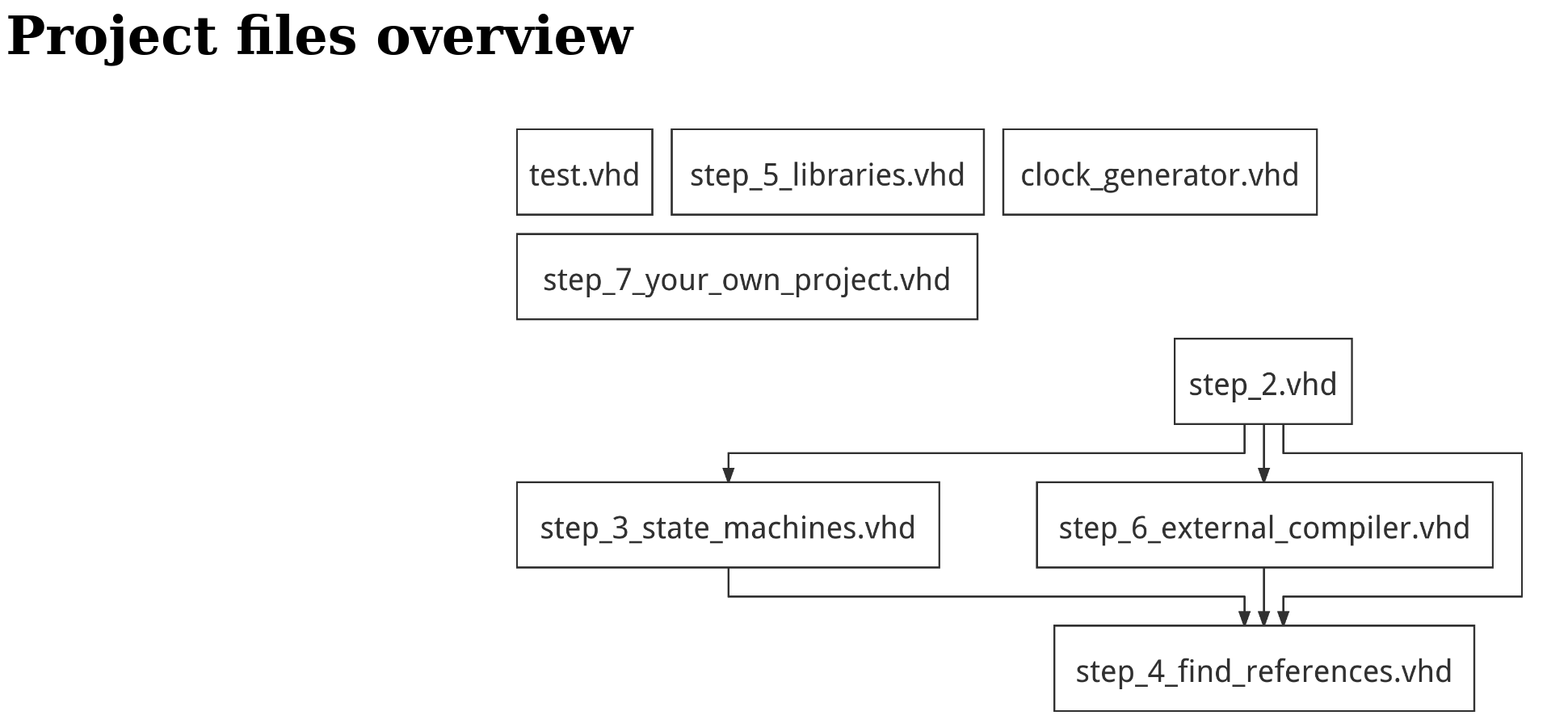

We enriched the Documentation Generation export with an overview of the dependencies between all project files.

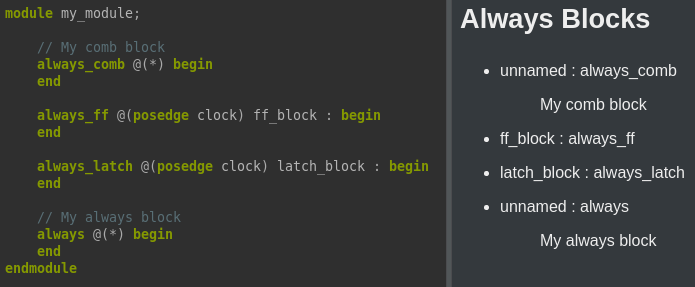

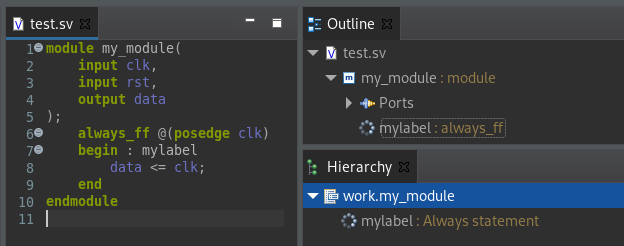

For Verilog projects we now also add always blocks to the generated documentation.

(System)Verilog Improvements

- Added support for Verilog files with

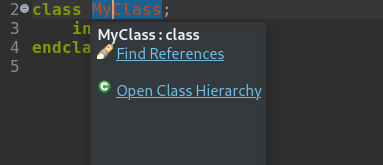

.vpand.svpextensions Open Class Hierarchyin the context menu now shows its keybinding (F4) andOpen Class Hierarchyis now shown as a hyperlink when hovering over classes

- Improved hover information for VHDL

entityinstantiations in Verilog code - Improved covergroup’s

samplemethod support - Named

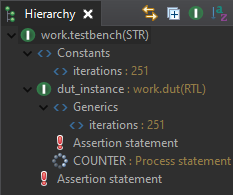

alwaysblocks are now shown in the Outline View and Hierarchy View

- Faster preprocessor performance

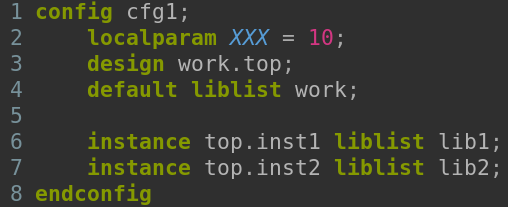

- Added support for

configdeclarations

- Better navigation support for:

- tagged unions expressions

foreachloop variables that are multidimensional arrays- match patterns

disablestatements

VHDL improvements

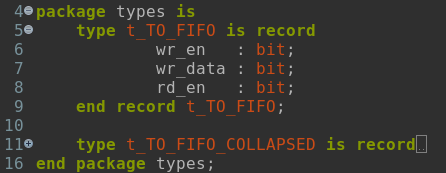

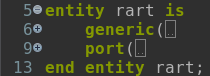

- We added folding support for

recordtypes,genericsandports

- Formatting support for signature filter path element (in

aliases) - Improved formatting for

assertionstatements andprocedures withgenerics - Added

package bodiesto the Dependencies View

Other Improvements

- ALINT support has been removed in favor of ALINT-PRO

- Support projects with spaces in its paths in the OneSpin and GHDL toolchains

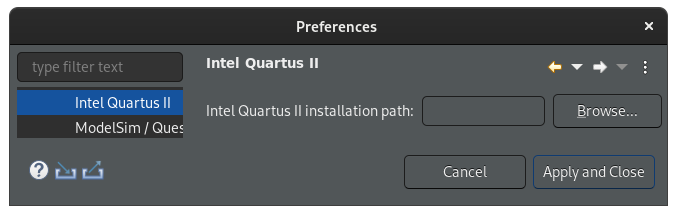

- Renamed “Altera Quartus II” to “Intel Quartus II”

- Use secure

httpsto download from our update site - Improved general user experience and error feedback on our Talkback page

- Added decorations to the Hierarchy View’s nodes

- SVG export can now handle extended identifiers (

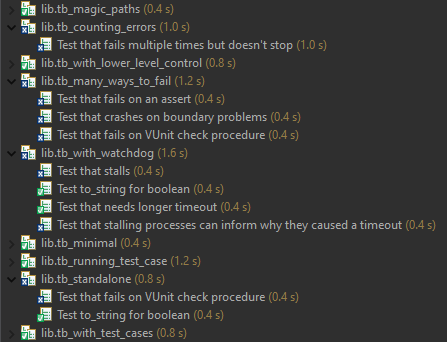

\VHDL___Extended____IdEnTiFiEr\,\verilog___*) - We improved the VUnit View. It now shows progress while the tests are running and it also shows the total run time of the tests

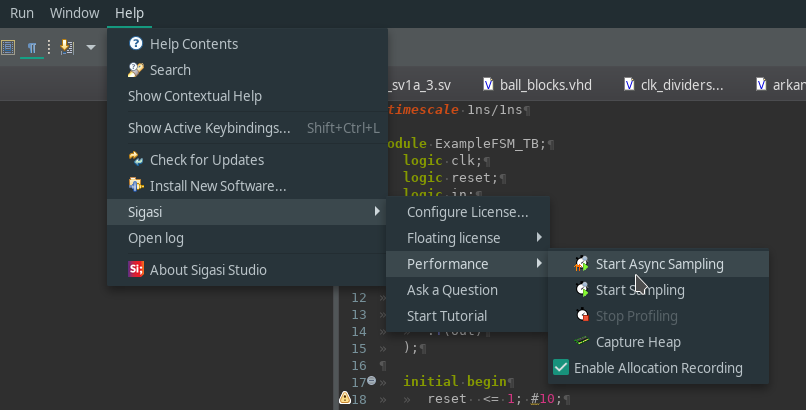

- Added the functionality to create memory and performance snapshots. These (anonymized) snapshots can help the Sigasi development team analyse performance issues offline

Bug fixes

- Fixed problem with

@symbol on the license preference page - Made sure color customization in the Graphics Configurations does not affect labels

- Fixed overflow issue in state machine headers

- Fixed user-defined autocomplete templates with

Anywherecontext with empty prefix - Fixed rare case in which pressing the graphical views’

pinbutton wouldn’t work - [VHDL] Fixed Sort associations quickfix for long association lists

- [VHDL] Made sure to always show VHDL versions in chronological order where applicable

- [VHDL] Fixed hover for negative exponents

- [VHDL] Fixed incorrect error on decorators for overloaded

entitytags - [VHDL] Fixed syntax highlighting in extended identifiers when those contain keywords

- [Verilog] Fixed formatting for files containing incomplete macro invocations (a lonely backtick)

- [Verilog] Fixed incorrect error when using tagged unions inside ternary conditional expressions

- [Verilog] Made sure the Preprocessor View also works when opening previous versions of a file through version control

- [Verilog] Fixed a rare error in verilog autocompletes

- [Verilog] Added an icon for UDP in Open Design Unit

- [Verilog] Fixed incorrect error for include path auto-configuration when including files from a folder

- [Verilog] Fixed overwrite mode (hold

Ctrlwhile selecting an entry from the context menu) for autocomplete for macros - [Verilog] Fixed incorrect error for parameterized range of UDP instances with delay

- [Verilog] Fixed incorrect error for assignment patterns

- [Verilog] Fixed incorrect warning for attributed port connections

- [Verilog] Fixed incorrect warning for targets of disable statements

- [Verilog] Fixed export of symbols in packages

- [VUnit] Fixed automatic library mapping based on

run.pycontents

+ A lot of other issues we could fix thanks to your Talkback reports

System requirements

- Sigasi Studio Standalone is supported on:

- Windows: Windows 10 (64 bit) or newer

- macOS 10.15 Catilina or newer

- Linux: RedHat Enterprise Linux RHEL 7.7 (64 bit) or newer

- Sigasi Studio depends on

libXss.sowhich can be obtained by installinglibXScrnSaver - More information on supported OSes can be found on the Eclipse website

- Sigasi Studio depends on

- Sigasi Studio as Plugin in your own Eclipse installation:

- Eclipse IDE 2021-03 up to and including Eclipse IDE 2021-06

- Java JRE 11

We recommend at least 4GB of memory available for Sigasi Studio, and you need about 300MB of free disk space.

Sigasi Studio 4.13.1 point release

On October 1 we released Sigasi Studio 4.13.1. This release fixes the following reported issues:

- Net search often does not work

- Using the rename dialog does not work

- The Hierarchy View doesn’t show up for certain entities

- Fixed

Check Matching Componentsfor components of incomplete Verilog modules - [VHDL] No hovers for declarations with an incomplete conditional initializer

- [VHDL] False positive errors on scientific exponent notation

- [VHDL] Dead state machine states are not being reported when an enum has duplicate literals

- [Verilog] The

Show Inherited Membersin the Class Hierarchy View doesn’t work - [Verilog] Support for

configconstructs is incomplete

Thanks for all the bug reports and enabling Talkback.