Sigasi Studio 3.5 brings full support for the SystemVerilog language, a frequently asked VHDL quickfix, a better State Machine Viewer and much more.

Full SystemVerilog language support

Sigasi Studio 3.5 finally brings full SystemVerilog support. Providing good editing and navigation support for the complex and colossal SystemVerilog language was an interesting technical challenge. We are proud to present our solution, that is both powerful and requires only very limited configuration.

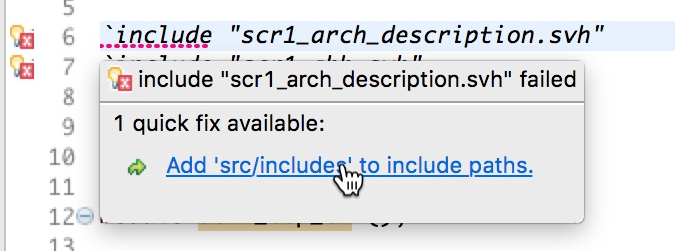

In addition to the SystemVerilog source files, Sigasi Studio only needs to know the include paths. Based on this information, Sigasi Studio automatically figures out in which order to analyze the files.

Sigasi Studio processes the code in a predictable order and keeps track of the preprocessor state. This allows us to offer full support for both SystemVerilog source files and include files. With Sigasi Studio, you can edit include files as if they were included in a SystemVerilog file.

SystemVerilog features in Sigasi Studio

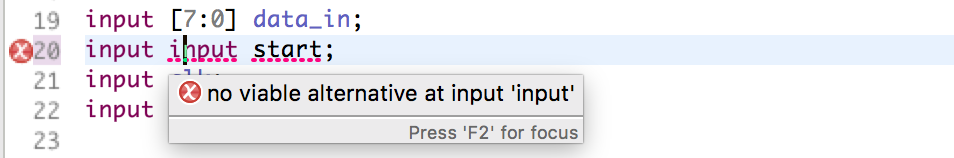

- Syntax error feedback: All valid SystemVerilog-2012 code should be accepted as valid code. Syntax errors are flagged while you type.

This works for both SystemVerilog and Include files, and for both Preprocessor and real SystemVerilog code.

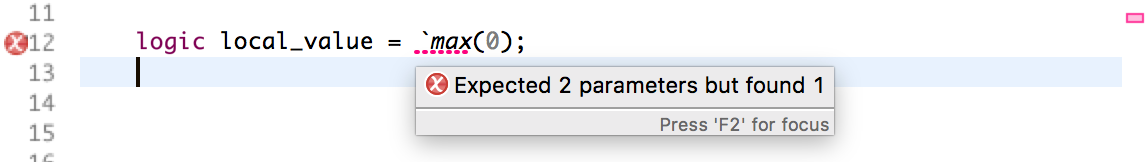

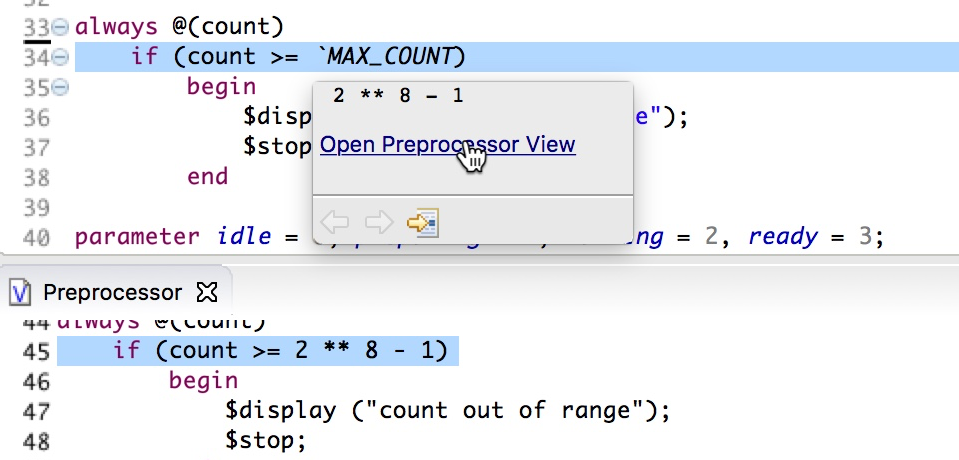

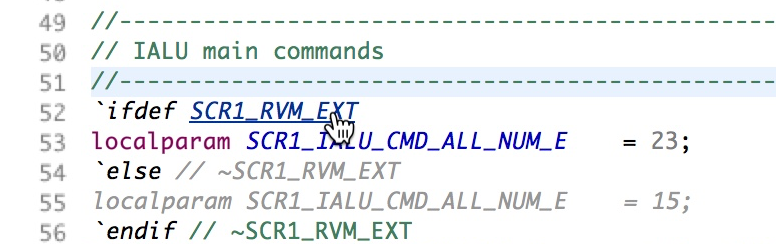

- Preprocessor: Sigasi Studio has a complete preprocessor. You can preview the text expansion with a hover or in the Preprocessor View.

- Include paths can be set with a quickfix, or by right clicking a project, selecting Properties, and opening the Verilog Preprocessor page.

- Semantic highlighting, Open Declaration and Find References

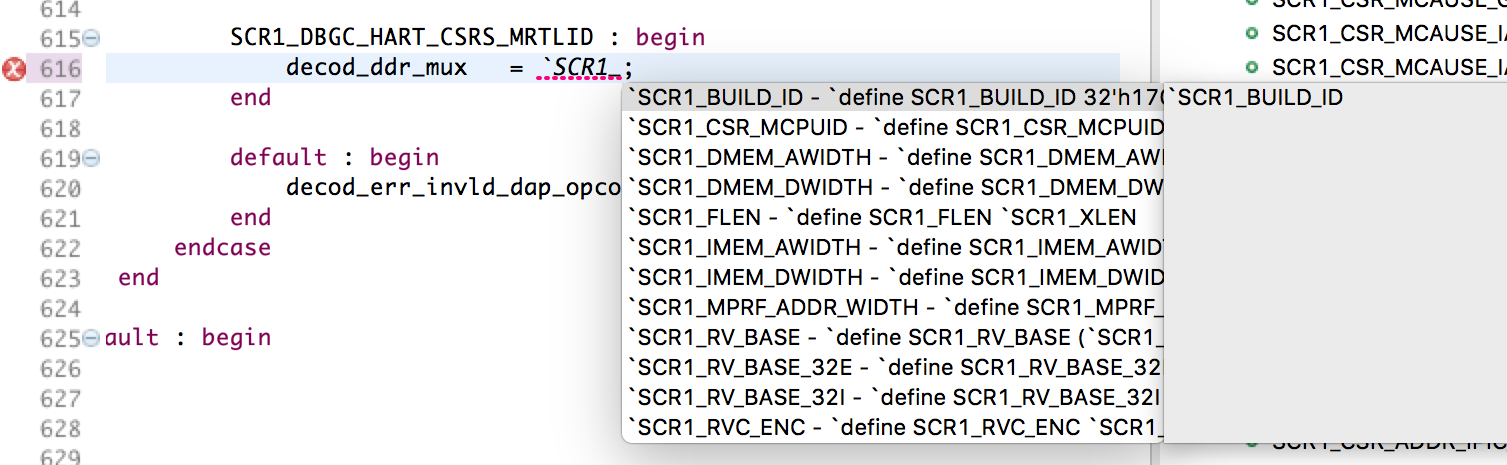

- Autocomplete (Ctrl+Space):

- Syntax: autocomplete for keywords and identifiers

- Fixed Templates: these templates can be modified

- Smart Templates: module instantiations

- Preprocessor directives

- Integration with an external compiler (Riviera-Pro, ModelSim, NCsim, OneSpin).

- We have a first version of SystemVerilog formatting. Clean Indentation (Ctrl+Shift+F) formats the entire file in the editor.

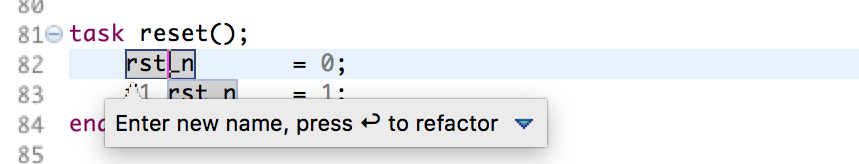

- Rename refactoring

- Libraries View gives an overview of all design units in your project.

Getting started

Getting started with Sigasi Studio on your own projects is easy. The blog post “How to setup a SystemVerilog project in Sigasi Studio”, describes how easy it is.

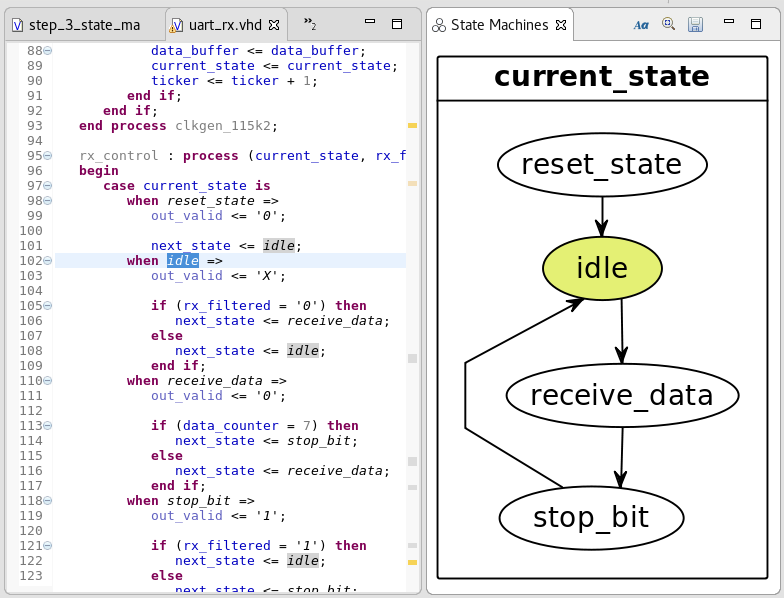

Improved State Machine Viewer (VHDL)

We gave the State Machine Viewer a refreshing update. We improved the looks. We have real bubbles now and transitions (edges) no longer overlap with states. If a design file has multiple state machines, we now display all state machines next to each other (i.e. no more tabs).

If your state machine uses simple if-conditions for transitions, the conditions will be displayed on the transistions (if you enable the “Aa”-button).

Other new and noteworthy improvements

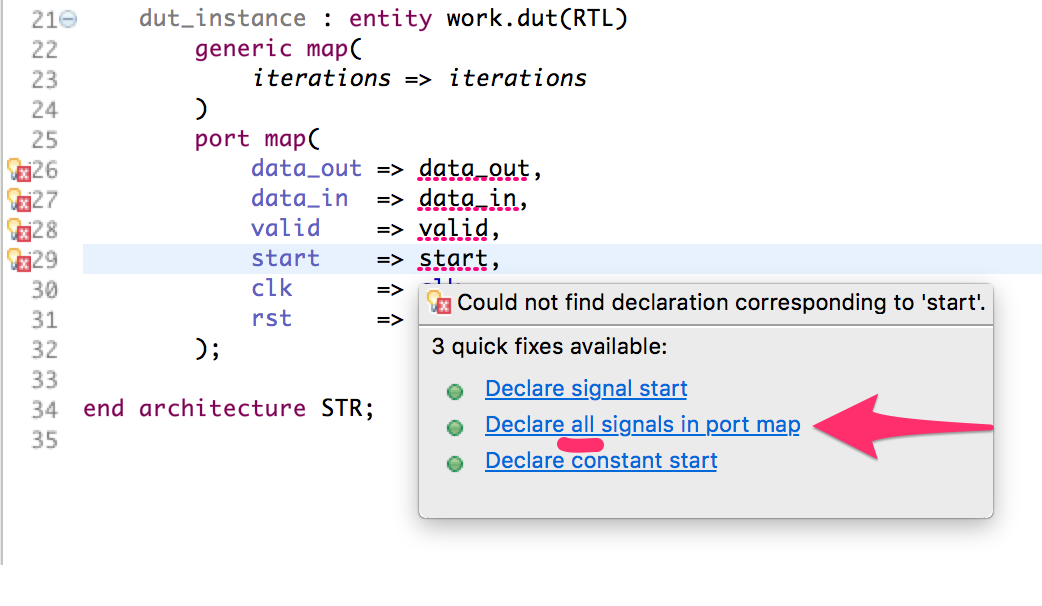

[Only for VHDL] Quickfix all undeclared signals in a port map. This was the number one feature request for our VHDL editor. You can now declare all signals in a port map (and all constants in a generic map) in a single action

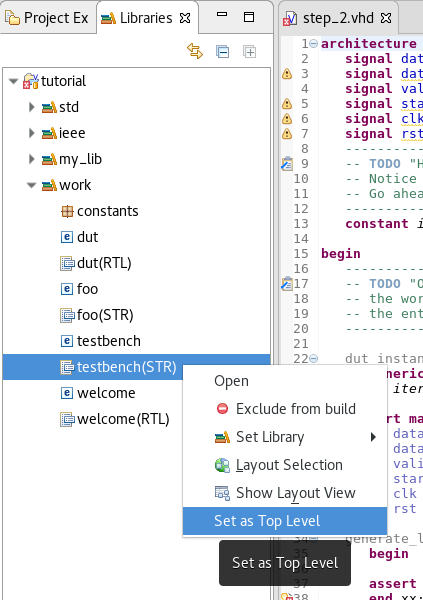

Improved Libraries View:

- Mixed language support

- Added action to Set toplevel

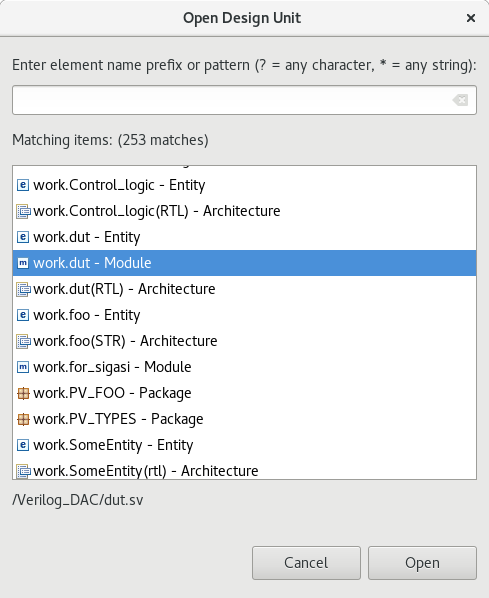

Open Design Unit dialog (Ctrl+Shift+D): We added an extra action to quickly open a (VHDL or SystemVerilog) design unit in an editor: hit Ctrl+Shift+D (or via Navigate > Open Design unit…), and type a pattern that matches the design unit name you’re looking for

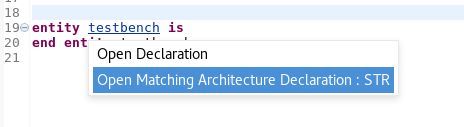

[Only for VHDL] Hyperlink from Entity to its architectures. There has always been an easy way to navigate from an architecture to its entity, by Ctrl+clicking (Open Declaration) the entity name. You can now also easily navigate in the other direction with Ctrl+click. If an entity has multiple architectures, they will all be listed in a drop down menu

[Only for VHDL] Better autocomplete for

configurations[Only for VHDL] Offer “Declare variable” quickfix for procedure parameters inside processes

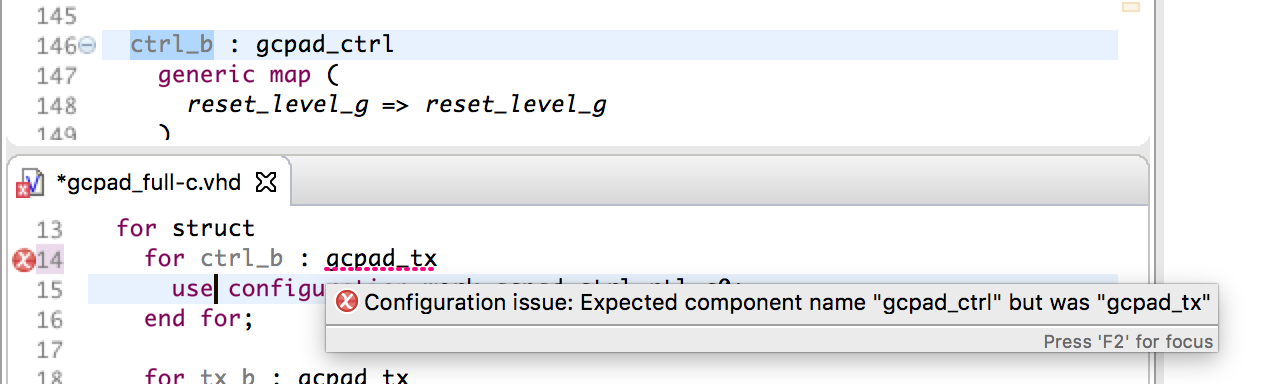

[Sigasi Studio XL ] Better validations for

configuration

[Sigasi Studio XL ] keyword autocomplete now respects the uppercase/lowercase formatting settings

[Sigasi Studio XL Doc ] The block diagram view now displays the component name of component instantiations

We updated the Eclipse Xtext dependency to

2.12.0

Bug fixes

As expected the old formatter had some untested “features”, that the new formatter in Sigasi 3.4 didn’t have.

This release brings many improvements to make the new formatter return the same results.

Thanks a lot for all the feedback!

Formatting bug fixes:

- ticket 3826 : Performance issues for certain VHDL constructs

- ticket 3827 : Format alignment on first parameter does not indent if a comment precedes the line

- ticket 3841 : Comments do not always break alignment blocks

- ticket 3848 : Formatting issue in

componentdeclarations - ticket 3856 : Do not break Doxygen (

--!) comments - ticket 3857 :

transportkeyword confuses the formatter - ticket 3858 : Formatting on first parameter with a component declaration and commented ports confuses the formatter

- ticket 3866 : Format on first parameter gets confused when declarations are grouped

- ticket 3869 : Align comments in group goes wrong

- ticket 3879 : Comments preceded by a tab break syntax on format

- ticket 3902 : Comments are not indented during format when they are before the end of an indented region

Other bug fixes:

- ticket 3845 : [VHDL-2008] Scoping issue with package generics in UVVM

- ticket 3019 : Entity instantiation autocomplete does not work in

generatestatements - ticket 3895 : Avoid

NoSuchMethodErrorwhen Sigasi is used with newer Guava versions (Eclipse 4.6.3) - ticket 3884 : Scoping error with

ifcondition labels ingeneratestatements - ticket 3876 : Silent exception while exporting block diagrams (project without mapped files)

- ticket 3844 : Calling QuickFix from problems view applies the changes twice

- ticket 3820 :

Case/for/elsegenerate show asunknownin Block Diagram - ticket 3893 : SystemVerilog parse error on Properties

- ticket 3741 : One off error in Verilog macros

- ticket 3921 : Autocomplete does not work after a SL comment

How to update?

If you have Sigasi Studio 3 installed, you can Update Sigasi or Download the Latest Version of Sigasi .

Sigasi 3.5.1 point release

On August 10 we released Sigasi Studio 3.5.1. This release contains only minor bug fixes.

Thanks for all bug reports and enabling Talkback.