Sigasi Studio can check that header comments match specified patterns. A header comment is a comment associated with a declaration or file. A file header comment starts at the first character of the file (no leading whitespace). Documentation Generation details how comments are associated with declaration. For VHDL, Sigasi supports checking header comments on files, architectures, concurrent blocks, configurations, contexts, entities, functions, package bodies, packages, package instantiations, procedures, and processes. For Verilog and SystemVerilog, only header comments on files are currently supported.

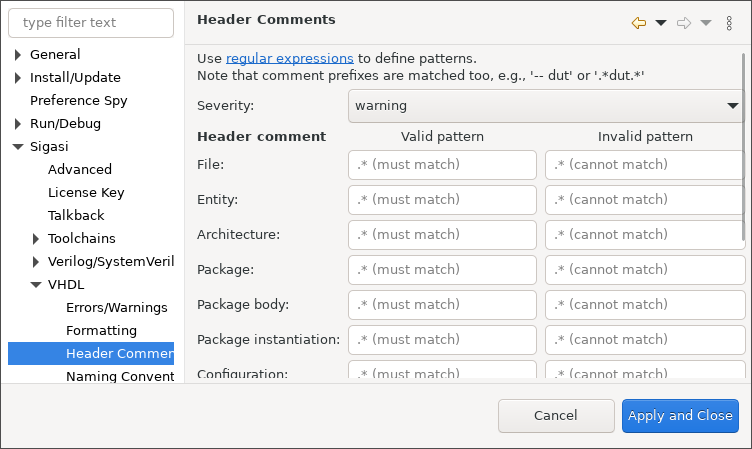

The check can be enabled for the entire workspace via Preferences > Sigasi > VHDL|Verilog/SystemVerilog > Header Comments. The patterns can be configured on the same page. More information on header comment checking and naming conventions is available on the general Linting and Quick Fixes page.

Note that the entire comment is checked, including comment characters (-- or /* */).

These characters have to be handled by your patterns too.

Since Sigasi Studio 4.4, the raw string of the header comment is checked to allow for maximum compliance checking.

This means that when a new line is matched, users should use \r?\n or the newly introduced \R to make sure the naming conventions work on all platforms.

Rule configuration

These rules can be disabled for your project, or their severity and parameters can be modified in the project linting settings. Alternatively, they can be manually configured with the following template:

# Note: two patterns can be specified. These patterns are separated by a tab

# character. The first pattern specifies a *valid* pattern (something that must

# match), and the second pattern specifies an *invalid* pattern (something that

# can not match). If only a valid pattern is required, the tab character can

# be left out. If only an invalid pattern is required, the pattern should be

# specified after a (backslash-escaped) tab character.

# In the VHDL linting preferences file

188/severity/${path}={error|warning|info|ignore}

188/params/architecture_header_comment/${path}=${regex} ${regex}

188/params/comment_header/${path}=${regex} ${regex}

188/params/configuration_header_comment/${path}=${regex} ${regex}

188/params/context_header_comment/${path}=${regex} ${regex}

188/params/entity_header_comment/${path}=${regex} ${regex}

188/params/function_header_comment/${path}=${regex} ${regex}

188/params/package_body_header_comment/${path}=${regex} ${regex}

188/params/package_header_comment/${path}=${regex} ${regex}

188/params/package_instantiation_header_comment/${path}=${regex} ${regex}

188/params/procedure_header_comment/${path}=${regex} ${regex}

188/params/process_header_comment/${path}=${regex} ${regex}

188/params/concurrent_block_header_comment/${path}=${regex} ${regex}

# In the Verilog/SystemVerilog linting preferences file

22/severity/${path}={error|warning|info|ignore}

22/params/comment_header/${path}=${regex} ${regex}