Linting is largely shared between our products. This page only covers Eclipse specific use cases. Refer to the common documentation to learn more.

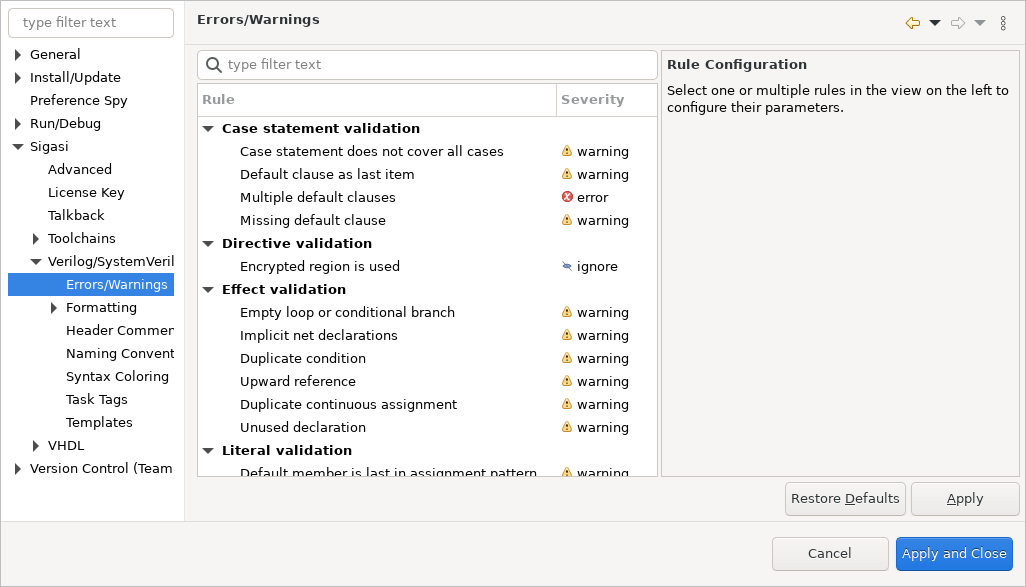

Configuring the Linting Rules

Linting rules can be configured per project, folder, or file by right-clicking a project, folder, or file > Properties and select Verilog Errors/Warnings or VHDL Errors/Warnings. On the top of the dialog, select Enable project specific settings to activate the rule configuration.

You can also configure the rules for the entire workspace through

- Window > Preferences > Sigasi > Verilog/SystemVerilog > Errors/Warnings for Verilog/SystemVerilog rules.

- Window > Preferences > Sigasi > VHDL > Errors/Warnings for VHDL rules.

Workspace Settings vs. Project Specific Settings

Workspace linting settings are only valid for the local workspace.

If you enable project specific settings, a .linting.prefs file is created in your .settings folder with the following lines.

eclipse.preferences.version=1

isEnabled=true

The second line (isEnabled = True) makes the workspace settings ineffective. After this point, your project’s linting settings are configured by this file.

Default values are used for the rules that are not configured in the .linting.prefs file.

If you change True to False in the file, then the workspace settings become effective again.

Marker Icons

marks an ignored problem that has a Quick Fix.

marks an ignored problem that has a Quick Fix. marks an ignored problem.

marks an ignored problem. marks an info message that can be resolved automatically with a Quick Fix.

marks an info message that can be resolved automatically with a Quick Fix. marks an info message.

marks an info message. marks a warning that can be resolved automatically with a Quick Fix.

marks a warning that can be resolved automatically with a Quick Fix. marks a warning that cannot be resolved automatically.

marks a warning that cannot be resolved automatically. marks an error that can be resolved automatically with a Quick Fix.

marks an error that can be resolved automatically with a Quick Fix. marks an error that cannot be resolved automatically.

marks an error that cannot be resolved automatically.

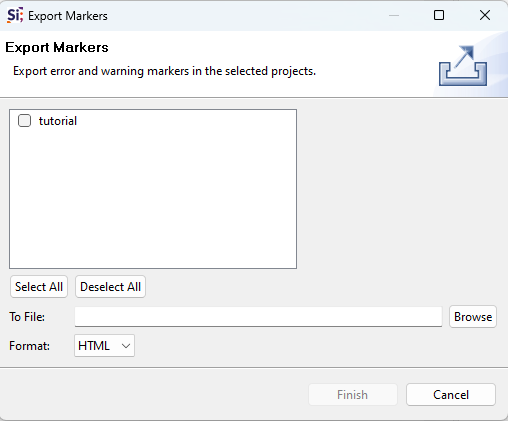

Export Markers

You can export markers for the entire project via the Export… menu. This feature is quite useful if you want to focus on the markers without generating documentation.

First, you have to check the box that is located next to the name of your project. You can then select the format of the file (either HTML or CSV) to be generated.

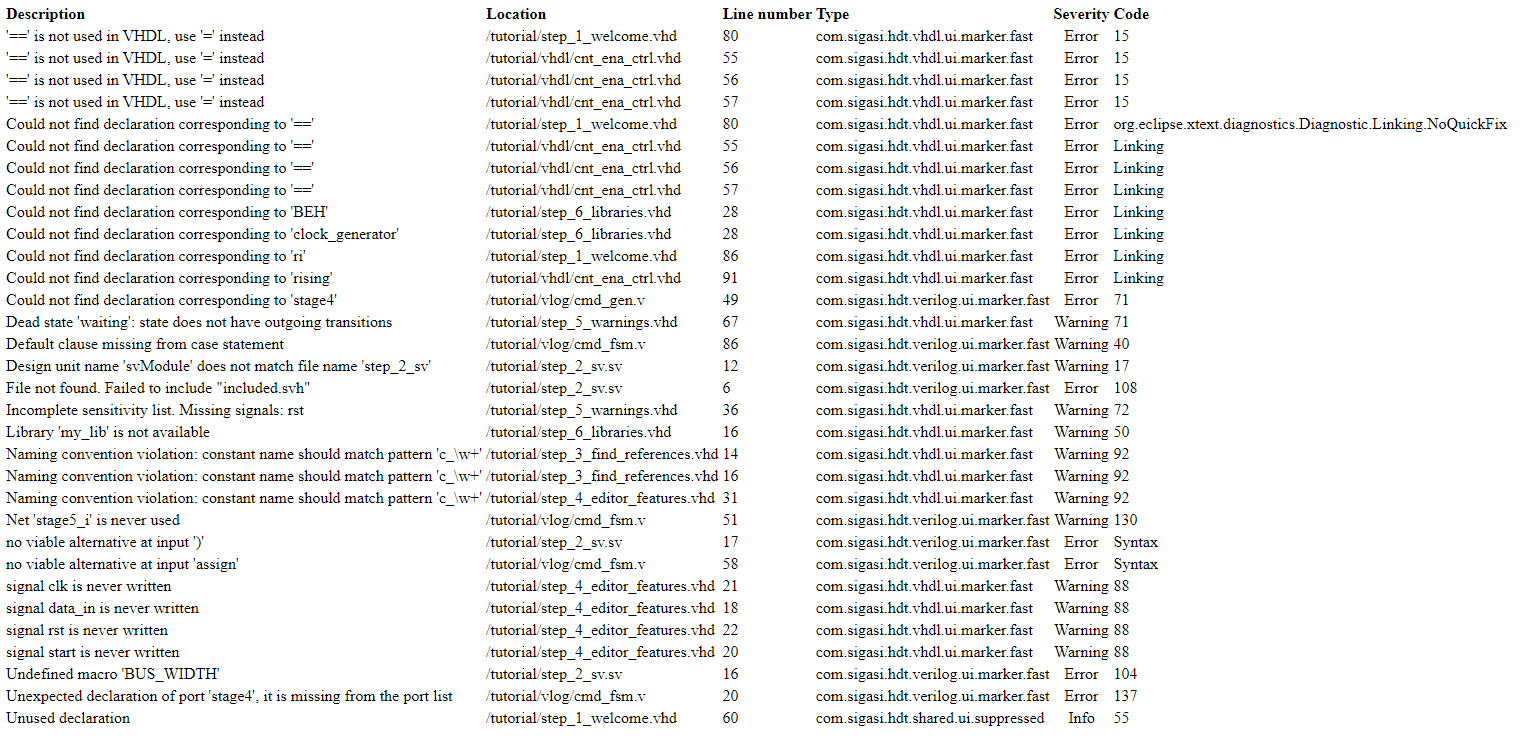

Markers Report

In the report, you can see all the markers in your project. The entries in the report are layed out in six columns:

- Description: shows what the marker is about

- Location: shows in which file the problem is marked

- Line number: line number of the marker

- Type of the marker

- Severity: severity that is set in the linting preferences

- Code: linting rule number for problem type

Note that suppressed markers are also listed in the report (see the last line in the image below).

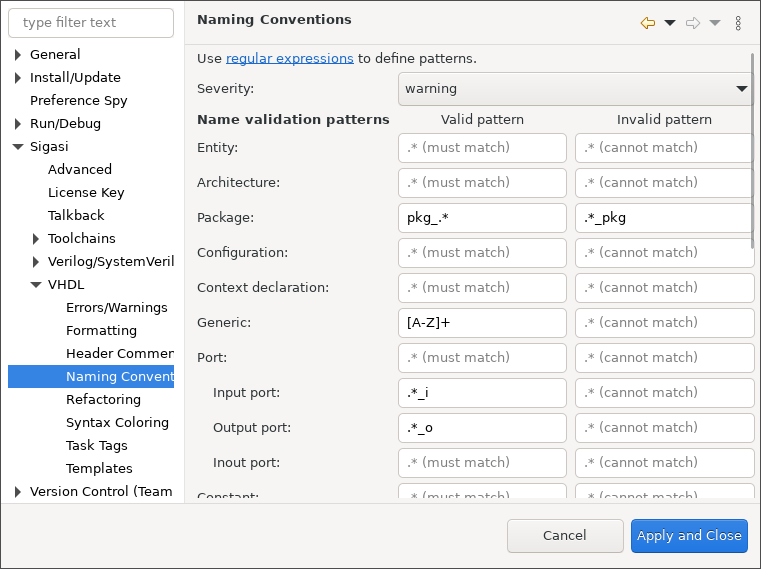

Naming Conventions and Header Comment Checks

Sigasi can check whether all sorts of names in the design -

entities, instances, modules, signals, variables… - follow

particular patterns. This may help designers to follow their

company’s or team’s coding rules. For example, coding rules may

prescribe that signal names must have a s_ prefix, that generics

names must be written in capitals, or that variable names must use

CamelCase. A naming convention rule is empty by default, which means

that the particular rule is not checked.

In addition, Sigasi can also check for header comments of files, design units, subprograms, etc. This could for instance be used to check whether a copyright notice or disclaimer has been included in the file header comment.

Workspace-wide naming convention settings are accessed via

- Window > Preferences > Sigasi > Verilog/SystemVerilog > Naming Conventions for Verilog and SystemVerilog, and

- Window > Preferences > Sigasi > VHDL > Naming Conventions for VHDL.

Workspace-wide header comment check settings are accessed via

- Window > Preferences > Sigasi > Verilog/SystemVerilog > Header Comments for Verilog and SystemVerilog, and

- Window > Preferences > Sigasi > VHDL > Header Comments for VHDL.

At the top, you can set the severity of naming convention non-conformities. Below, you can enter the validation patterns. Patterns use the RE2/J regular expressions syntax. Note that names are not validated if the corresponding validation pattern is empty.

Note that you can add two patterns per name: a valid pattern that the name must match (a marker will appear if it does not match) and an invalid pattern that the name must not match (a marker will appear if it does). You can set either or both patterns per name.

You can also configure naming conventions and header comments per project, or even per file or folder. You can read more on this on the Naming Conventions and Check Header Comment pages.

Quick Fixes

Problems that have markers annotated with a lightbulb icon (like ![]() )

can be automatically resolved through a Quick Fix.

To trigger a Quick Fix, click the problem marker or press Ctrl+1 and select the Quick Fix.

Quick Fixes can also be triggered from the Problems View by right-clicking

on a problem and clicking

)

can be automatically resolved through a Quick Fix.

To trigger a Quick Fix, click the problem marker or press Ctrl+1 and select the Quick Fix.

Quick Fixes can also be triggered from the Problems View by right-clicking

on a problem and clicking Quick Fix. Multiple problems of the same kind can also be selected in the Problems View, to

fix them all at once.