While support for VHDL-2019 is being improved, this page lists the VHDL-2019 features that are supported in the latest release.

Currently supported

All the new VHDL 2019 APIs in the updated

stdandieeelibrariesFunctions now know the type of the receiver of the return value

function convert_to_slv(constant i: in integer) return TResult of std_logic_vector is variable result: TResult; begin -- Can now access attributes of the receiver of this return value result := std_logic_vector(to_signed(i, result'length)); return result; end function; -- Now we can do the following x <= convert_to_slv(i); -- Instead of x <= std_logic_vector(to_signed(i, x'length));The ending

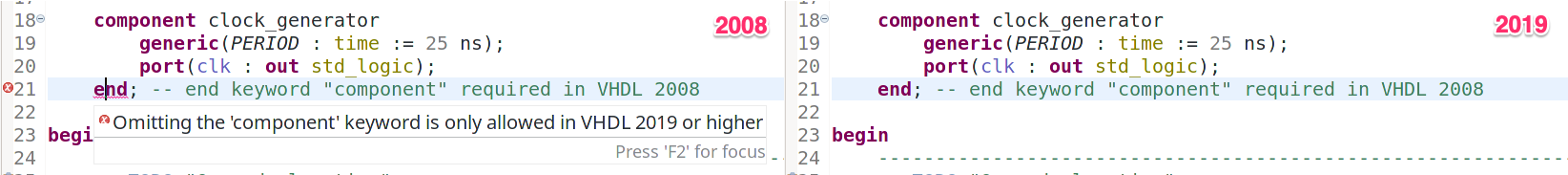

componentkeyword in a component declarations is now optional

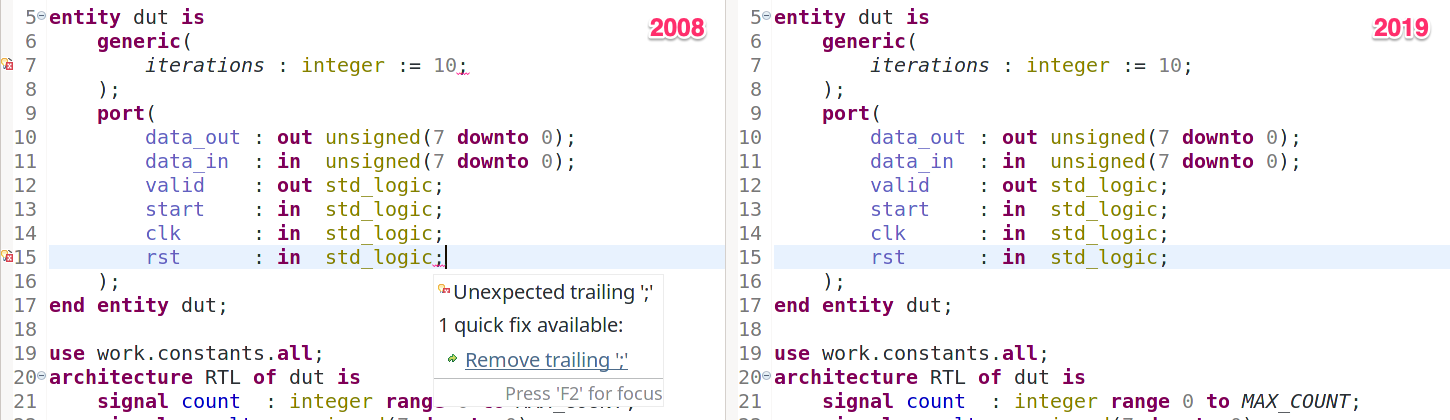

A trailing semicolon in

port,genericandparameterlists is now allowed

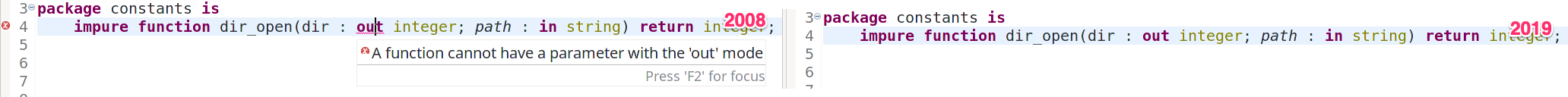

Parameters of

impure functions can now haveinoutandoutmodes

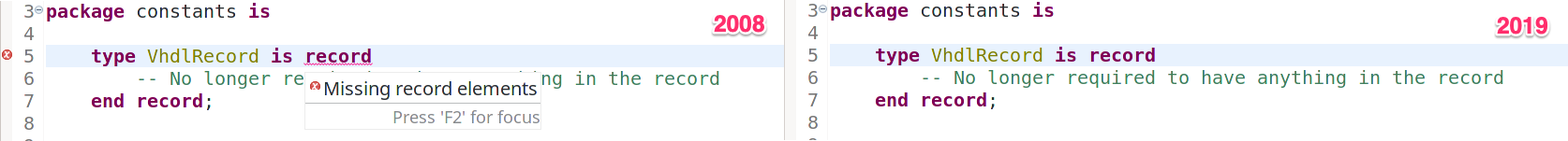

recorddeclarations can now be empty

Qualified expressions’ operand is now optional

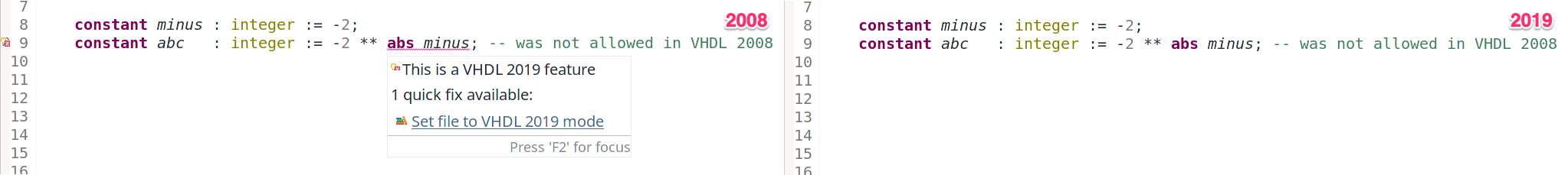

-- Value of "abc" is an empty value of the type std_logic constant abc : std_logic := std_logic'();Improved syntax of power expressions (

**)

when-elseandunaffectedexpressions are now allowed inreturnstatements

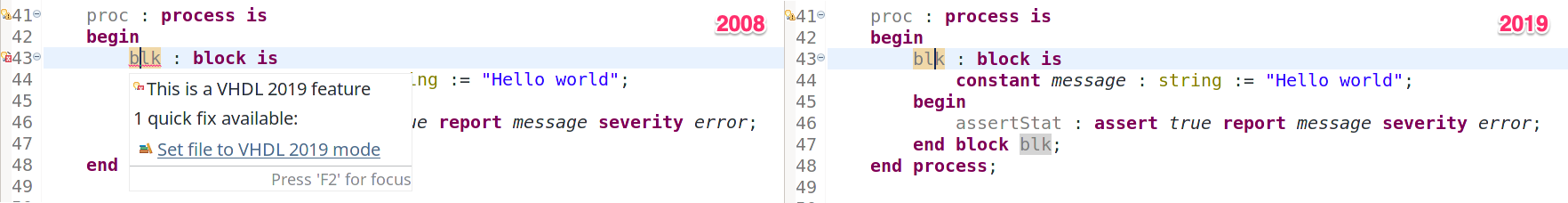

Sequential

blockstatements

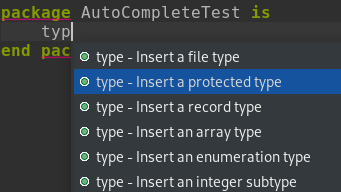

Added an autocomplete for, and improved automatic indentation of, protected type declarations

Added support for VHDL 2019 private variable declaration and aliases in protected declaration

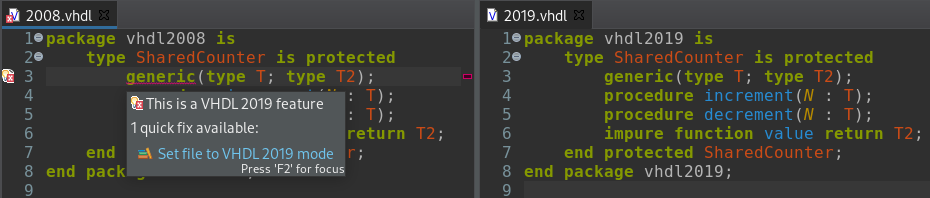

type SharedCounter is protected function increment(i : integer) return integer; private variable v : integer := 0; alias aliasName is increment; alias aliasName2 is aliasName; end protected SharedCounter;Added support for VHDL 2019 generic protected type declarations

Allow

conditional_or_unaffected_expressionwhere neededproc : process is variable v : bit := '1'; begin v := '0' when isAnswer(42) else unaffected; end process;Added support for VHDL 2019 Conditional Analysis

Enable VHDL-2019

The Sigasi Studio 4.11 release introduced VHDL 2019 into Sigasi Studio.

To make use of the improved language features and APIs you need to set your VHDL project (or a single file) to VHDL 2019 and update the std and ieee libraries:

- Update the project version: Right click the project (or file) and select Properties > VHDL Version > VHDL 2019.

- Update the

stdandieeelibraries: Right click theCommon Librariesfolder, and select Set Library > Reset Common libraries

We have made a screencast to demonstrate this.